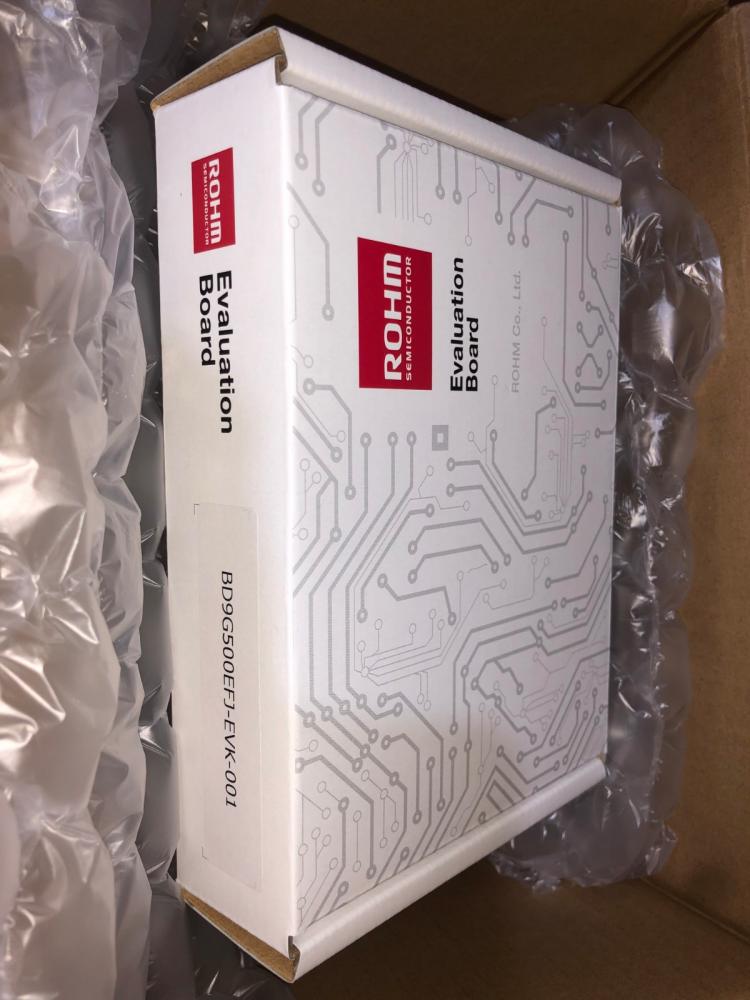

于近日收到罗姆DC/DC测试板一块,年底赶项目比较忙,将会持续更新。包装精致,板子接线柱很漂亮。搜了某商城居然有此颗料,如测试合适,将引入项目。

我又来了,项目繁多,抽空发帖

上回收到罗姆DCDC DEMO板一块,今着重测试如下:

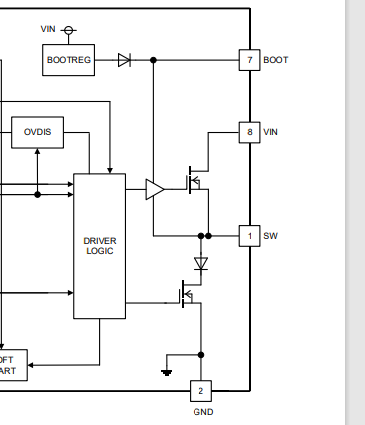

芯片的BOOT脚与SW输出脚

根据芯片的手册的内部结构框图,发现BOOT脚涉及到内部MOS管的控制信号电压(因此BOOT上外接了自举电容C3)、SW脚为MOS输出。

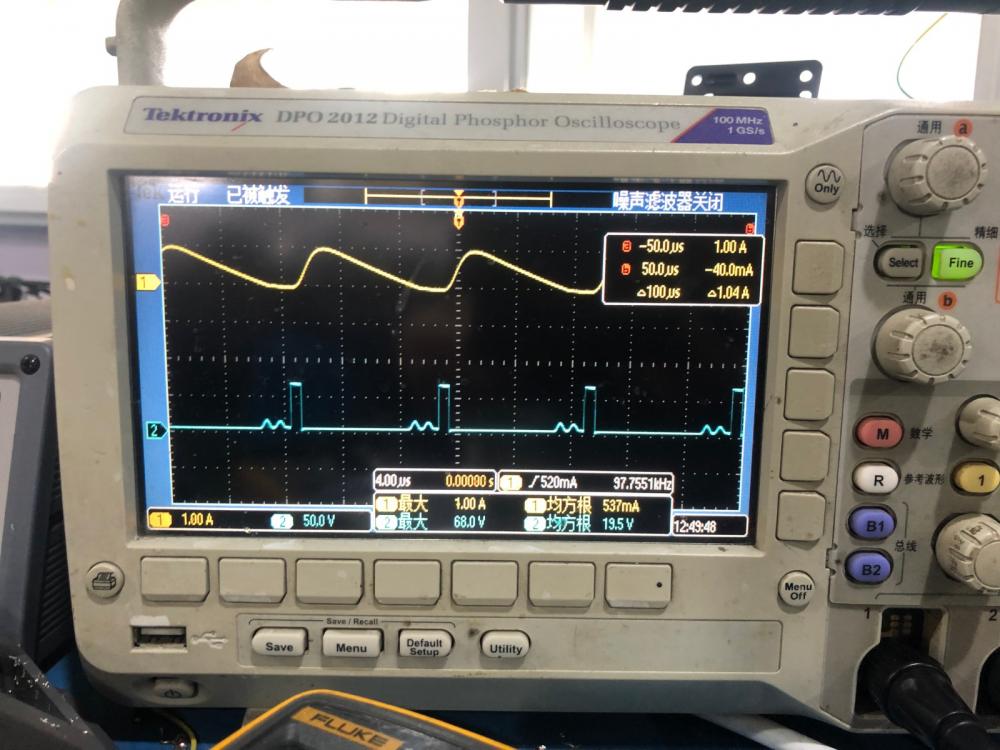

受MOS开关瞬间的影响,自举电容C3会按照开关频率进行充放电,这时会导致BOOT引脚上出现较高电压。根据测试,一般情况下48V输入电压最大值为56V左右,但是偶尔会出现异常过冲,导致瞬态电压峰值达到68V。BS引脚上的电压是由自举电容C3两端的电压加上引脚LX的电压值,因此峰值脉冲最大值出现在5V建立之后。

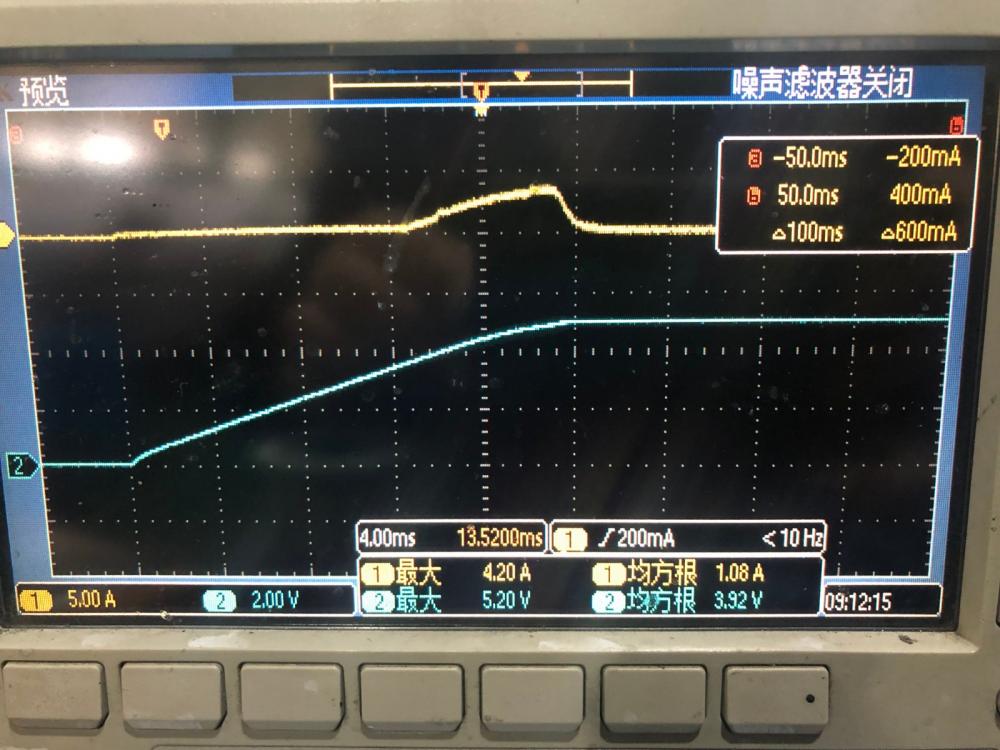

如上图,黄色为SW脚输出电流,蓝色为BOOT脚上电压。

如上图,黄色为SW脚输出电流,蓝色为BOOT脚上电压。

因此猜测,当输出电压加大时,或者输入电压情况复杂时(输入VIN有空开,布板不良有耦合,输入波动较大)自举电容上的R5电阻需加大,以减少BOOT脚尖峰电压,手册电压最大85V,不知实际多少。

已布板,后面样板详细测试。

上图黄色为48V输入时,SW脚输出电流波形,蓝色为VOUT输出电压波形,输出电压上升时间为20mS,带5V 300mA显示屏,

通过分析测试,发现这个电流是由于5V上的220uF 50V铝电解电容C7充电产生的,测试上电瞬间电容引脚上的充电电流,发现和这个电流完全符合。在手册范围内,在5V上电完成后,电容充放电压差减小,充电电流减小。由于我司DCDC主要用于15V上MCU与电机预驱供电应用,使用功率不到100mA,后续将减小输出电容容量,输出电感亦可考虑低温升电流,高饱和电流的高频小功率电感,待布板完成后细测。

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |