作者:Jenson Fang

逐次逼近型(SAR)ADC是在在工业,汽车,通讯行业中应用最广泛的ADC之一,例如电机电流采样,电池电压电流监控,温度监控等等。

通常工程师在设计SAR ADC时,通常需要注意以下三个方面:ADC前端驱动设计,参考电压设计,数字信号输出部分设计。本文将介绍ADC的前端驱动所需要的注意的一些要素。

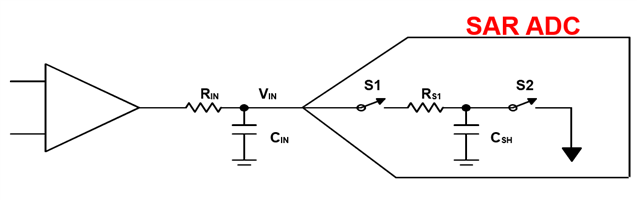

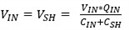

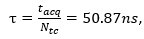

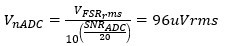

如图所示是一个常见的SAR ADC的驱动电路包括驱动放大器和RC滤波。接下来将从如何设计RC滤波器,以及如何选择合适的运算放大器展开。

图1. SAR ADC驱动电路基本架构

如何设计RC滤波网络

首先我们来看一下RC网络的设置,对于RC网络,它的主要作用分为以下两个方面:

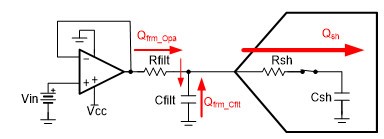

1:对ADC的Csh进行充电,由于ADC采样保持阶段需要输入给采样保持电容Csh充电。如图所示,开始采样时,Csh的电荷由输入部分(Qfrm_opa)和RC滤波电容(Qfrm_cflit)提供,保证在一定时间内达到精度的要求。显然,随着采样精度和采样率的不断提高,驱动ADC的难度加大,因为必须在有限的时间内采样时间(tacq)内将Csh上的电压达到满足精度要求(1/2LSB内)。所以我们在ADC前加入电容,当采样保持阶段时对Csh进行充电,保证采样的精度。电阻则作为隔离作用,避免运放直接驱动容性负载,提升系统的稳定性。

图2. SAR ADC采样保持阶段电流方向

2:RC网络同时也限制了输入信号的带宽,并且降低了运放带来的噪声量,但是于此同时,带宽的限制会使信号的延长建立时间,引起信号的失真

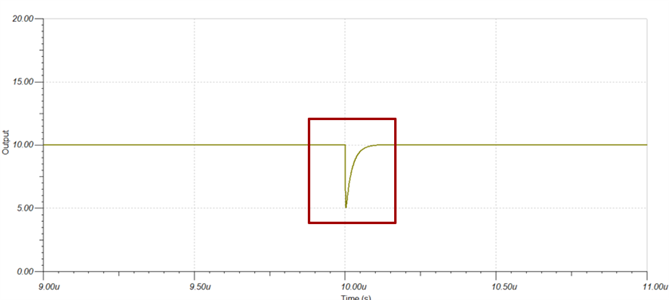

我们设计RC网络的目标就是在有限的时间内采样时间(tacq)内将Csh上的电压达到满足精度要求(1/2LSB内),如果不加入RC或者RC选择不合适,可能出现如图所示的情况(横坐标为时间,纵左边为Vfilt电压,可以看到信号幅值变化大且反向恢复时间长),这是因为运放的带宽不足或者RC电路中电容太小,导致Qfrm_opa与Qfrm_cflit不能在采样时间(tacq)内将电荷转移至Csh中,如果在信号没有达到足够的采样时间内进行采样,就会产生信号失真。

图3. 不合适的RC滤波导致信号幅度变化大且反向恢复时间长

显然,我们无法同一个RC网络使用在不同的SAR ADC的应用中,那么我们要怎么去为SAR ADC设计一个合适的RC滤波网络呢?

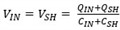

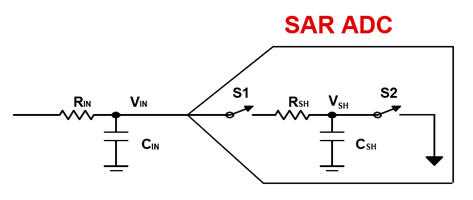

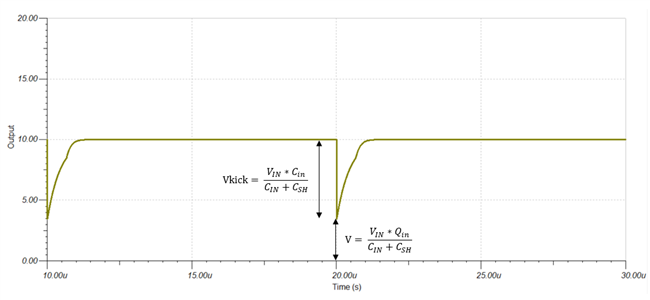

如下图所示为SAR ADC的简化原理图,以最坏的情况,CSH对地放电为例。当开关S1关闭时,开关S2打开时,电容CIN与CSH共享电荷可得出等式 ,由于电容CSH对地放电,则QSH=0,且QIN=VIN*CIN,则可以得出

,由于电容CSH对地放电,则QSH=0,且QIN=VIN*CIN,则可以得出

图4. SAR ADC驱动电路基本架构

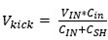

则可以推算出 ,如图所示:

,如图所示:

图5. SAR ADC驱动VIN电压

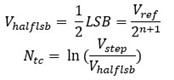

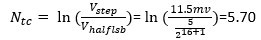

在ADC的采集阶段,ADC建立至1/2LSB所需要的RC时间常数 , 其中tacq为采集时间Ntc为建立所需的时间常数数目。所需的时间常数数目可以通过计算阶跃大小VSTEP与建立误差(本例为1/2LSB)之比的自然对数来获得:

, 其中tacq为采集时间Ntc为建立所需的时间常数数目。所需的时间常数数目可以通过计算阶跃大小VSTEP与建立误差(本例为1/2LSB)之比的自然对数来获得:

由此,我们可以求出RC的时间常数 ,根据

,根据 ,可以得出RC的值以及带宽。

,可以得出RC的值以及带宽。

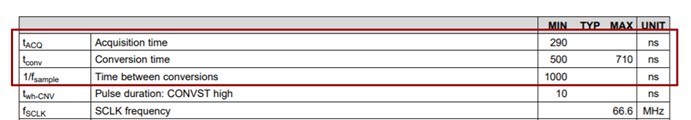

以TI 16位ADC:ADS8860 为例,从数据手册第8页可以得到以下信息:

图6. ADS8860数据手册数据

它的MAX Conversion time为 710ns ,Min Acquisition time 为290ns ,吞吐率为1Msps,假设,参考电压为5V,信号为100kHz的正弦波

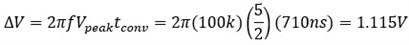

那么在转换时间,信号最大变化量为:

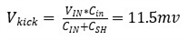

根据ADS8860的CSH=59pF,一般CIN选择CSH的20倍以上,这里取CIN=5.9nF则可以计算出Vkick电压:

接下来计算建立到1/2LSB的时间常数:

则可以得出:

因此选择R=8.6ohm,带宽为3.13MHz

将取值带入仿真后可得图,相对于没有RC滤波的ADC而言,加入合适的RC滤波可以使ADC-Vin电压变化幅度变小,反向建立时间也更短。

图7. 不合适的RC与加入计算后RC的VIN电压波形对比

由我们的公式我们可以知道,当吞吐率越高时,我们对采样保持的时间就相对越短,从而需要更大的RC带宽。所以当随着精度和采样率的不断提高,设计RC的难度会加大,我们需要权衡设计驱动的参数。

如何选择适合的驱动放大器

首先必须说明的是驱动放大电路并不是总是需要的,他的作用通常有以下几个:

用于信号类型的转换,例如单端信号转化为差分信号

以对信号进行调理,例如将信号放大/缩小等

如果输入阻抗小,可以放置运放来增大输入的阻抗,和减少输出阻抗

限制带宽,防止高频信号输入进行干扰

当信号带宽低,信号变化十分缓慢,如气体,温度等,可以直接使用RC进行驱动,降低成本,结构如图所示。

图8. 无运放驱动SAR ADC电路简图

那么在我们选择运放的时候需要注意以下参数:运放的带宽,运放的噪声特性,运放的失真特性等。

运放的带宽:带宽大的运放可以让RC电路更快的进行充电,一般来说,选择运放的带宽为RC滤波器的4倍以上,如果需要运放提供电压增益则需要选择更大带宽的运放。但是同时带宽大的运放往往静态电流和失调/偏置电流会比较大,所以要进行取舍。

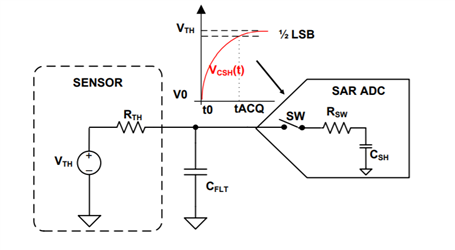

运放的噪声特性:对于运放的噪声特性来说,为了不让运放的噪声对ADC的精度产生影响,一般会使运放的总噪声在ADC噪声的1/5左右。如果,ADC的SNR为86dB,Vref=5V,那么该系统中的总噪声应该小于:

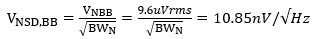

根据计算得出的总噪声,取ADC噪声的1/5,进行计算可以计算出应该选择的运放的1/f噪声和宽带噪声的最大影响值,假设选用的运放有极小的1/f噪声可以忽略不计的话,可以经过以下公式计算,得出结果:

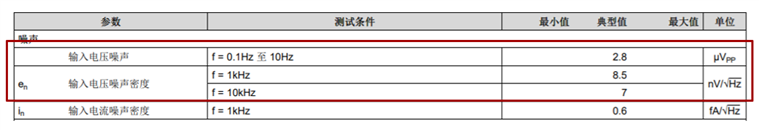

像Ti的产品OPA320,由数据手册第8页中可得,宽带噪声密度为可以满足要求

图9. OPA320数据手册噪声数据

运放的失真特性:对于ADC的驱动运放来说,我们通常需要选择输入输出轨对轨的运放,防止不必要的输出失真,但是通常正负轨对轨的运放价格相对的高,所以通常使用的是单电源输入,单极轨对轨的运放。

参考文献:

TI Precision Labs ADCs video :

https://training.ti.com/ti-precision-labs-adcs

Analog Engineer's Circuit: Data Converters:

https://www.ti.com/lit/an/sbaa375/sbaa375.pdf?ts=1602684911109

https://www.ti.com/lit/an/sbaa256a/sbaa256a.pdf?ts=1602684851397

Design Challenges and Improvement Techniques for SAR ADC Driver Circuit :

http://www.ti.com.cn/cn/lit/an/slaa571a/slaa571a.pdf

我要赚赏金

我要赚赏金