ADC介绍

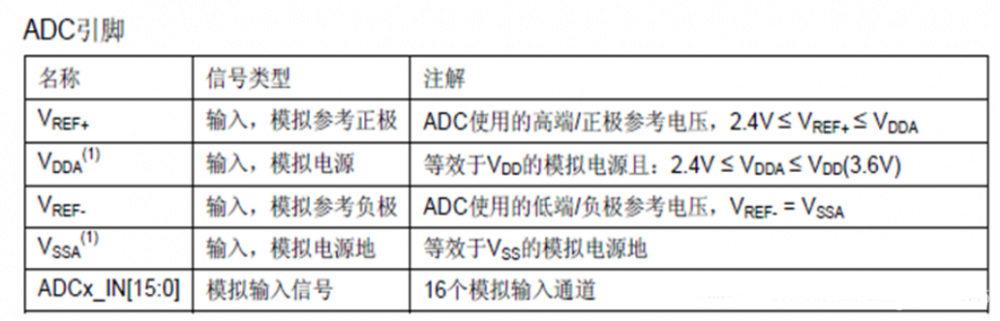

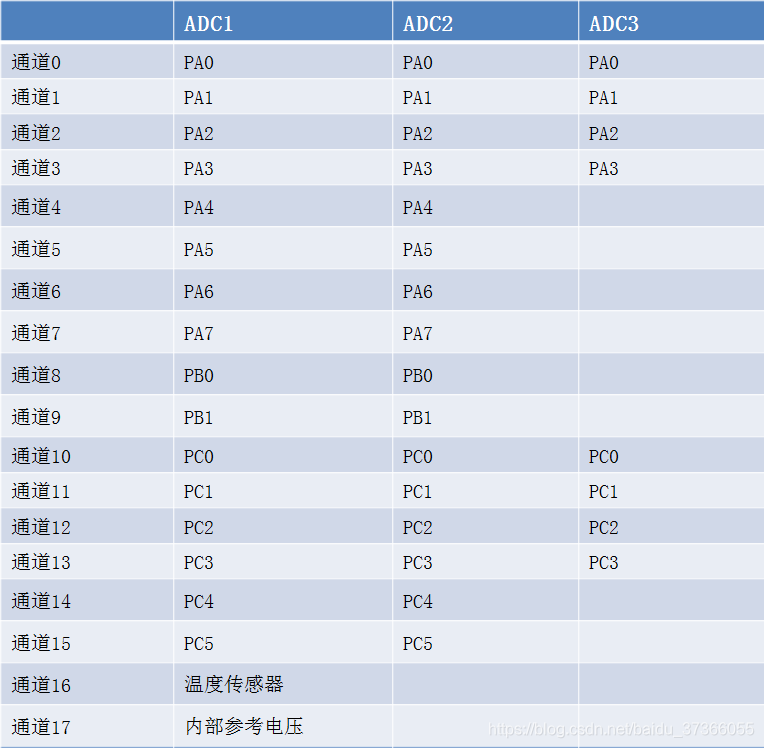

12位ADC是一种逐次逼近型模拟数字转换器。它有多达18个通道,可测量16个外部和2个内部信号源。各通道的A/D转换可以单次、连续、扫描或间断模式执行。ADC的结果可以左对齐或右对齐方式存储在16位数据寄存器中。模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。ADC 的输入时钟不得超过14MHz,它是由PCLK2经分频产生。

ADC主要特征

● 12位分辨率

● 转换结束、注入转换结束和发生模拟看门狗事件时产生中断

● 单次和连续转换模式

● 从通道0到通道n的自动扫描模式

● 间断模式执行

● 自校准

● 带内嵌数据一致性的数据对齐

● 采样间隔可以按通道分别编程

● 规则转换和注入转换均有外部触发选项

● 双重模式(带2个或以上ADC 的器件)

● ADC转换时间:

─ STM32F103xx增强型产品:时钟为56MHz时为1μs

(时钟为72MHz为1.17μs)

─ STM32F101xx基本型产品:时钟为28MHz时为1μs

(时钟为36MHz为1.55μs)

─ STM32F102xxUSB型产品:时钟为48MHz 时为1.2μs

─ STM32F105xx和STM32F107xx产品:时钟为56MHz时为1μs

(时钟为72MHz为1.17μs)

● ADC供电要求:2.4V到3.6V

● ADC输入范围:VREF- ≤ VIN ≤ VREF+

● 规则通道转换期间有DMA请求产生。

通道选择

有16个多路通道。可以把转换组织成两组:规则组和注入组。在任意多个通道上以任意顺序进行的一系列转换构成成组转换。例如,可以如下顺序完成转换:通道3 、通道8 、通道2 、通道2、通道0、通道2、通道2、通道15。

● 规则组由多达16个转换组成。规则通道和它们的转换顺序在ADC_SQRx寄存器中选择。规则组中转换的总数应写入ADC_SQR1寄存器的L[3:0]位中。

● 注入组由多达4个转换组成。注入通道和它们的转换顺序在ADC_JSQR寄存器中选择。注入组里的转换总数目应写入ADC_JSQR寄存器的L[1:0]位中。

如果ADC_SQRx或ADC_JSQR寄存器在转换期间被更改,当前的转换被清除,一个新的启动脉冲将发送到ADC 以转换新选择的组。

温度传感器和通道ADC1_IN16相连接,内部参照电压VREFINT和ADC1_IN17相连接。可以按注入或规则通道对这两个内部通道进行转换。

注意: 温度传感器和VREFINT只能出现在主ADC1 中。

单次转换模式

单次转换模式下,ADC只执行一次转换。该模式既可通过设置ADC_CR2 寄存器的ADON位(只适用于规则通道)启动也可通过外部触发启动(适用于规则通道或注入通道),这时CONT位为0 。

一旦选择通道的转换完成:

● 如果一个规则通道被转换:

─ 转换数据被储存在16位ADC_DR寄存器中

─ EOC(转换结束)标志被设置

─ 如果设置了EOCIE,则产生中断。

● 如果一个注入通道被转换:

─ 转换数据被储存在16位的ADC_DRJ1寄存器中

─ JEOC(注入转换结束)标志被设置

─ 如果设置了JEOCIE位,则产生中断。然后ADC停止。

连续转换模式

在连续转换模式中,当前面ADC转换一结束马上就启动另一次转换。此模式可通过外部触发启动或通过设置ADC_CR2寄存器上的ADON位启动,此时CONT位是1。

每个转换后:

● 如果一个规则通道被转换:

─ 转换数据被储存在16位的ADC_DR寄存器中

─ EOC(转换结束)标志被设置

─ 如果设置了EOCIE,则产生中断。

● 如果一个注入通道被转换:

─ 转换数据被储存在16位的ADC_DRJ1寄存器中

─ JEOC(注入转换结束)标志被设置

─ 如果设置了JEOCIE位,则产生中断。

扫描模式

此模式用来扫描一组模拟通道。

扫描模式可通过设置ADC_CR1寄存器的SCAN位来选择。一旦这个位被设置,ADC扫描所有被ADC_SQRX 寄存器(对规则通道)或ADC_JSQR(对注入通道)选中的所有通道。在每个组的每个通道上执行单次转换。在每个转换结束时,同一组的下一个通道被自动转换。如果设置了CONT位,转换不会在选择组的最后一个通道上停止,而是再次从选择组的第一个通道继续转换。

如果设置了DMA位,在每次EOC后,DMA控制器把规则组通道的转换数据传输到SRAM 中。而注入通道转换的数据总是存储在ADC_JDRx寄存器中。

间断模式

规则组

此模式通过设置ADC_CR1 寄存器上的DISCEN位激活。它可以用来执行一个短序列的n次转换(n<=8),此转换是ADC_SQRx寄存器所选择的转换序列的一部分。数值n由ADC_CR1寄存器的DISCNUM[2:0]位给出。

一个外部触发信号可以启动ADC_SQRx 寄存器中描述的下一轮n次转换,直到此序列所有的转换完成为止。总的序列长度由ADC_SQR1寄存器的L[3:0]定义。

举例: n=3,被转换的通道 = 0 、1、2、3、6、7、9、10

第一次触发:转换的序列为 0 、1、2

第二次触发:转换的序列为 3 、6、7

第三次触发:转换的序列为 9 、10,并产生EOC事件

第四次触发:转换的序列 0 、1、2

注意:

当以间断模式转换一个规则组时,转换序列结束后不自动从头开始。

当所有子组被转换完成,下一次触发启动第一个子组的转换。在上面的例子中,第四次触发重新转换第一子组的通道 0 、1和2。

注入组

此模式通过设置ADC_CR1 寄存器的JDISCEN位激活。在一个外部触发事件后,该模式按通道顺序逐个转换ADC_JSQR寄存器中选择的序列。

一个外部触发信号可以启动ADC_JSQR寄存器选择的下一个通道序列的转换,直到序列中所有的转换完成为止。总的序列长度由ADC_JSQR寄存器的JL[1:0]位定义。

例子: n=1,被转换的通道 = 1 、2、3

第一次触发:通道1被转换

第二次触发:通道2被转换

第三次触发:通道3被转换,并且产生EOC和JEOC事件

第四次触发:通道1被转换

注意:

1 当完成所有注入通道转换,下个触发启动第1个注入通道的转换。

在上述例子中,第四个触发重新转换第1个注入通道1。

2 不能同时使用自动注入和间断模式。

3 必须避免同时为规则和注入组设置间断模式。间断模式只能作用

于一组转换。

ADC时钟配置

void RCC_ADCCLKConfig(uint32_t RCC_PCLK2);

输入参数范围:

#define RCC_PCLK2_Div2 ((uint32_t)0x00000000)

#define RCC_PCLK2_Div4 ((uint32_t)0x00004000)

#define RCC_PCLK2_Div6 ((uint32_t)0x00008000)

#define RCC_PCLK2_Div8 ((uint32_t)0x0000C000)

STM32的ADC最大的转换速率为1Mhz,也就是转换时间为1us(在ADCCLK=14M,采样周期为1.5个ADC时钟下得到),不要让ADC的时钟超过14M,否则将导致结果准确度下降。

ADC的采样时间

可编程的通道采样时间

ADC 使用若干个ADC_CLK 周期对输入电压采样,采样周期数目可以通过ADC_SMPR1 和ADC_SMPR2寄存器中的SMP[2:0]位更改。每个通道可以分别用不同的时间采样。

总转换时间如下计算: TCONV = 采样时间+ 12.5个周期

例如:当ADCCLK=14MHz ,采样时间为1.5周期

TCONV = 1.5 + 12.5 = 14周期 = 1μs

常见的周期有:

1.5周期、7.5周期、13.5周期、28.5周期、41.5周期、55.5周期、71.5周期、239.5周期。

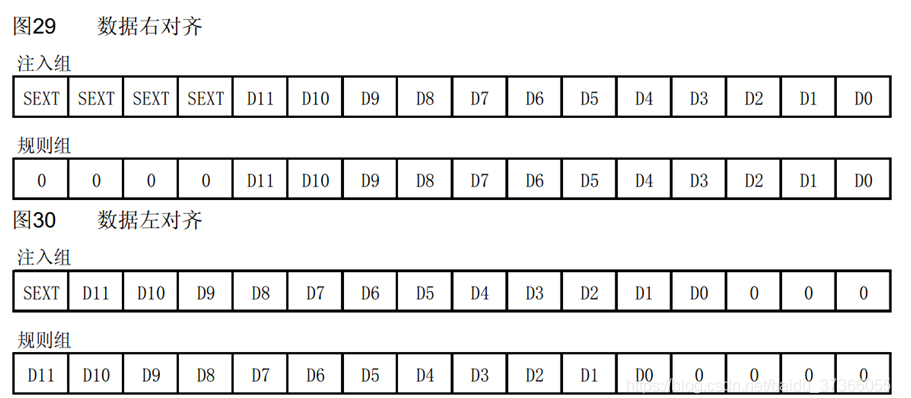

数据对齐

ADC_CR2寄存器中的ALIGN位选择转换后数据储存的对齐方式。数据可以左对齐或右对齐,如图29和图30所示。

注入组通道转换的数据值已经减去了在ADC_JOFRx寄存器中定义的偏移量,因此结果可以是一个负值。SEXT位是扩展的符号值。

对于规则组通道,不需减去偏移值,因此只有12个位有效。

校准

ADC有一个内置自校准模式。校准可大幅减小因内部电容器组的变化而造成的准精度误差。在校准期间,在每个电容器上都会计算出一个误差修正码(数字值),这个码用于消除在随后的转换中每个电容器上产生的误差。

通过设置ADC_CR2寄存器的CAL位启动校准。一旦校准结束,CAL位被硬件复位,可以开始正常转换。建议在上电时执行一次ADC校准。校准阶段结束后,校准码储存在ADC_DR 中。

注意:

1 建议在每次上电后执行一次校准。

2 启动校准前,ADC必须处于关电状态(ADON=’0’)超过至少两个ADC时钟周期。

我要赚赏金

我要赚赏金