时钟树的概念:

我们可以把MCU的运行比作人体的运行一样,人最重要的是什么?是心跳! 心脏的周期性收缩将血液泵向身体各处。心脏对于人体好比时钟对于MCU,微控制器(MCU)的运行要靠周期性的时钟脉冲来驱动,而这个脉冲的始源往往是由外部晶体振荡器提供时钟输入,最终转换为多个外部设备的周期性运作。这种时钟“能量”的传递路径犹如大树的养分由主干流向个分支,因此称为时钟树。

STM32时钟:

在STM32中每个外设都有其单独的时钟,在使用某个外设之前必须打开该外设的时钟 ,为什么要这么麻烦来设置每一个外设的时钟而不是将所有外设的时钟统一打开?因为STM32的外设繁多,外设的运作所需要的最佳时钟各不相同,如果所有时钟同时运行会给MCU带来极大的负载,所以STM32采取自助餐式的时钟管理方式——随用随开。

STM32时钟树系统:

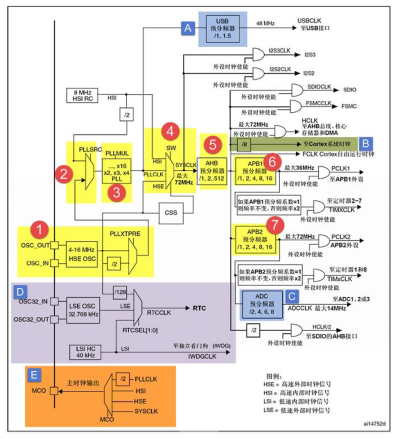

认识STM32的时钟管理方式后就要对其时钟树系统有一个大体的掌握,时钟树系统的结构如下,从图中可以知晓有多少时钟、时钟速度为多少、时钟如何分配等。图看起来很复杂,但我们只需要大体了解其运作流程即可。

各类时钟简括:

1.HSE时钟(高速外部时钟):来源为外部无源晶振,通常速度8M。

由RCC_CR时钟控制寄存器中的16:HSEON控制。

2.HSI时钟(高速内部时钟):来源为芯片内部,大小为8M,当HSE故障时,系统时钟会自动切换到HSI,知道HSE启动成功,相当于HSE的替补。

由RCC_CR时钟控制寄存器的位0:HSION控制。

3.PLLCLK(锁相环时钟):来源为HSI/2、HSE经过倍频所得。

由CFGR(时钟配置寄存器)中PLLXTPRE、PLLMUL控制。

4.SYSCLK(系统时钟):来源为HSI、HSE、PLLCLK,最高速度为72M。

由CFGR中的SW控制。

5.HCLK(AHB高速总线时钟):来源由系统时钟分频得到,速度最高为72M。

由CFGR中的HPRE控制。

6.PCLK1(APB1低总线时钟):来源为HCLK分频得到,速度最高为36M ,为APB1总线上的外设提供时钟。

由RCC_CFGR时钟配置寄存器的PPRE1位控制。

7.PCLK2(APB2高总线时钟):来源为HCLK分频得到,速度最高为72M,为APB2总线上的外设提供时钟。

由RCC_CFGR时钟配置寄存器的PPRE2位控制。

8.RTC时钟:来源为HSE_RTC(HSE分频得到)、LSE、LSI,为芯片内部的RTC外设提供时钟。

由RCC备份域控制寄存器RCC_BDCR中RTCSEL控制。

9.MCO时钟输出 :来源为PLLCLK/2、HSE、HSI、SYSCLK,微控制器时钟输出引脚,由PA8复用所得。

由CRGR中MCO控制。

系统时钟配置流程

结合系统时钟函数进行说明,此处利用HSE作为系统时钟来源,代码源于野火教程,由于此代码是帮助我们熟悉系统时钟配置流程,故不要求可以run

void HSE_SetSysClock(uint32_t pllmul)

2 {

3 __IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;

4

5 // 把 RCC 外设初始化成复位状态

6 RCC_DeInit();

7

8 //使能 HSE,开启外部晶振,野火 STM32F103 系列开发板用的是 8M

9 RCC_HSEConfig(RCC_HSE_ON);

10

11 // 等待 HSE 启动稳定

12 HSEStartUpStatus = RCC_WaitForHSEStartUp();

13

14 // 只有 HSE 稳定之后则继续往下执行

15 if (HSEStartUpStatus == SUCCESS) {

16 //-----------------------------------------------------------------//

17 // 这两句是操作 FLASH 闪存用到的,如果不操作 FLASH,这两个注释掉也没影响

18 // 使能 FLASH 预存取缓冲区

19 FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

20

21 // SYSCLK 周期与闪存访问时间的比例设置,这里统一设置成 2

22 // 设置成 2 的时候, SYSCLK 低于 48M 也可以工作,如果设置成 0 或者 1 的时候,

23 // 如果配置的 SYSCLK 超出了范围的话,则会进入硬件错误,程序就死了

24 // 0: 0 < SYSCLK <= 24M

25 // 1: 24< SYSCLK <= 48M

26 // 2: 48< SYSCLK <= 72M

27 FLASH_SetLatency(FLASH_Latency_2);

28 //-----------------------------------------------------------------//

29

30 // AHB 预分频因子设置为 1 分频, HCLK = SYSCLK

31 RCC_HCLKConfig(RCC_SYSCLK_Div1);

32

33 // APB2 预分频因子设置为 1 分频, PCLK2 = HCLK

34 RCC_PCLK2Config(RCC_HCLK_Div1);

35

36 // APB1 预分频因子设置为 2 分频, PCLK1 = HCLK/2

37 RCC_PCLK1Config(RCC_HCLK_Div2);

38

39 //-----------------设置各种频率主要就是在这里设置-------------------//

40 // 设置 PLL 时钟来源为 HSE,设置 PLL 倍频因子

41 // PLLCLK = 8MHz * pllmul

42 RCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);

43 //-------------------------------------------------------------//零死角玩转 STM32

—基于野火 F103[MINI]开发板

44 //论坛: www.firebbs.cn 138 / 682 淘宝: https://fire-stm32.taobao.com

45 // 开启 PLL

46 RCC_PLLCmd(ENABLE);

47

48 // 等待 PLL 稳定

49 while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) {

50 }

51

52 // 当 PLL 稳定之后,把 PLL 时钟切换为系统时钟 SYSCLK

53 RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

54

55 // 读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

56 while (RCC_GetSYSCLKSource() != 0x08) {

57 }

58 } else {

59 // 如果 HSE 开启失败,那么程序就会来到这里,用户可在这里添加出错的代码处理

60 // 当 HSE 开启失败或者故障的时候,单片机会自动把 HSI 设置为系统时钟,

61 // HSI 是内部的高速时钟, 8MHZ

62 while (1) {

63 }

64 }

65 }

代码步骤 :

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

配置流程图:

图中序号1~7对应着系统设置配置的流程

结语:其实只要掌握了配置流程图中黄色部分的配置流程就已经大半理解STM32的时钟树了,刚开始学有点懵逼,但看多了,在心中排练的多了就会慢慢熟悉的。

我要赚赏金

我要赚赏金