低压差线性稳压器 (LDO) 在电路设计中无处不在。许多只有三个终端;VIN、VOUT 和 GND。什么可能出错?某些 LDO 设计标准已得到充分证明,例如需要观察正确的输出电容和等效串联电阻 (ESR)。现代 LDO 使这变得更加容易,因为它们支持各种输出电容器,包括低 ESR 陶瓷类型。电源抑制 (PSRR) 等 LDO 性能指标也受到关注,因为该指标定义了 LDO 抑制其输入纹波和噪声的效率。

本文介绍了使用 LDO 进行设计的一些鲜为人知的方面。

重复负载瞬态行为

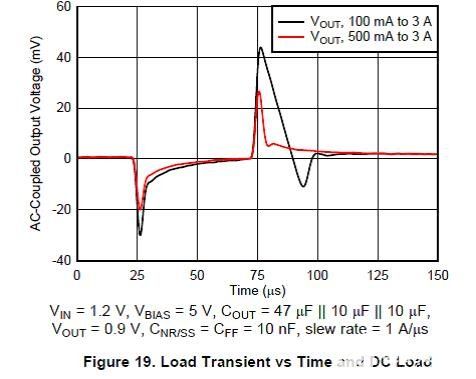

即使使用低 VIN-VOUT 差分,TPS7A84A 低噪声 LDO 也能正常工作。LDO 数据表通常会显示负载瞬态行为的波形。图 1 显示了 TPS7A84A 的示例。阅读数据表时,重要的是要注意获取数据的测试条件。图 1 记录了输出电容、VIN-VOUT 差分、偏置电压、原始负载电流、负载电流瞬态和负载瞬态压摆率。显示了两条曲线,唯一的区别是添加了负载瞬态的原始基本负载。当施加负载瞬态时,输出电压会下降并恢复,因为电流从输出电容器中汲取,并且在 LDO 的控制环路做出反应以打开通路 FET 后的短时间内更难提供增加的负载电流并返回 VOUT为名义上的。

图 1:TPS7A84A 数据表负载瞬态性能

红色曲线适用于 3A-0.5A=2.5A 的负载瞬态,黑色曲线适用于 3A-0.1A=2.9A 的负载瞬态。正如预期的那样,较大的负载瞬态黑色曲线显示出比红色更深的下降,但两者的性能都非常好,VOUT 下降只有 20-30mV。有趣的是,移除负载阶跃时的过冲扰动大于且持续时间长于施加负载阶跃时的扰动。过冲幅度随着原始负载电流的减小而增加。通常,当移除负载时,LDO 会短暂地继续提供其负载电流,为输出电容器充电并导致过冲。不久之后,LDO 中的控制回路做出反应,逐渐关闭其通路 FET,以使输出降至其标称电压。绝大多数 LDO 不能主动吸收负载电流,只能提供负载电流,因此唯一将输出电容器放电至其标称 VOUT 的就是原始负载。在图 1 中,500mA 原始负载(红色曲线)将比 100mA(黑色曲线)更快地对输出电容器放电,并且 VOUT 更快地恢复到其标称电压。

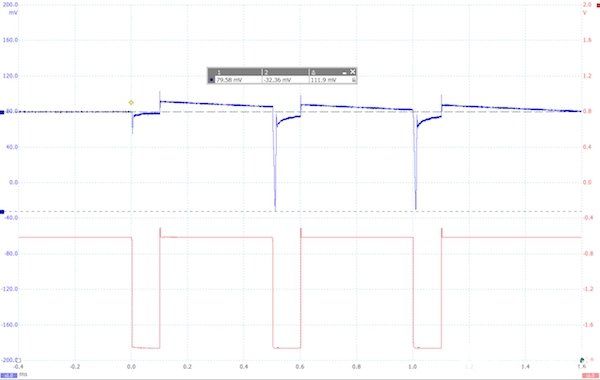

原始负载越低,负载瞬态消除后 LDO 将其 VOUT 恢复到标称值所需的时间就越长。现在,如果负载瞬态是重复的,例如某些 RF 类型负载的情况,那么图 2 的结果显示了 0.56A 的负载以 2kHz 的速率添加/移除到设置为 1.4V o/p 的 LDO . 负载被移除然后重新应用之间的实际时间是 0.4 毫秒。在图 2 中,第一个负载瞬态应用和移除会产生较低的下冲和过冲(VOUT 的下降约为 8.5mV),但第二个、第三个和随后的负载瞬态表现出更差的性能。下降已恶化至 ~112mV,即 VOUT 的 8%。

图 2:蓝色迹线 – LDO 的 VOUT,交流耦合 40mV/div,0.2ms/div。红色迹线 – 负载阶跃(低时增加负载,高时去除负载)。LDO VIN=VBIAS=1.8V。LDO VOUT=1.4V。LDO 输出电容为 47μF + 2x 10μF。LDO 输入电容为 47μF + 2x 10μF

为什么是这样?原因是在第一次和第二次负载瞬态应用和移除之间,VOUT 尚未恢复到其标称电压,因为对输出电容器放电的原始负载电流现在约为 0mA。VOUT 缓慢返回其标称电压。因此,LDO 中的控制环路仍在命令 pass-FET 完全关闭。当第二个负载瞬变发生时,控制环路检测到 VOUT 正在下降,并且必须以相反的方式做出反应,以完全打开其通路 FET,以增加通过它的电流以对其输出电容器进行再充电并支持增加的负载。这需要时间,因此与第一个负载瞬态相比,VOUT 下降得更多。

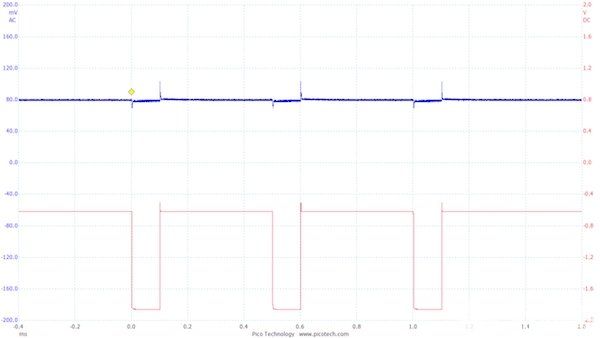

图 3:与图 2 相同的条件,只是在 VOUT 上添加了 10Ω 假负载

LDO 可能比 DC/DC 转换器更嘈杂!?

通常,当需要安静的电源轨时,会使用 LDO。LDO 会比 DC/DC 转换器更嘈杂吗?有可能的用例。LDO 的输出噪声在 LDO 内部产生,主要由其参考电压噪声组成。LDO 的 VIN 上出现的噪声和纹波电压被其 PSRR 抑制,并在 VOUT 上出现衰减。正如我们所见,负载瞬变也会干扰 LDO 的输出电压,其控制环路旨在衰减这种情况。这三种噪声和纹波源也存在于 dc/dc 转换器中,此外,与 LDO 不同,它们的输出端也存在开关噪声和纹波。当需要安静的电源轨时,它们的输出上没有开关噪声和纹波通常使 LDO 成为最佳选择。

对于 LDO,其输出上的负载电流与其输入上出现的负载电流相同。LDO 输出上的 1A 负载瞬态干扰会作为 1A 负载瞬态反映到其输入端,因此也会反映到为 LDO 供电的上游转换器。输入端的 1A 负载瞬变会干扰为 LDO 供电的上游转换器——它还必须响应电流的这种变化。这会在加载负载时导致电压骤降,而在移除负载时会导致过冲。上游转换器输出上的这种噪声源很容易成为其输出中最大的噪声分量,即使它是一个 DC/DC 转换器。如果 dc/dc 转换器输出还为其他更敏感的负载供电,那么它们将暴露于该纹波电压,并且它们可能会以降低的性能运行。如果将 LDO 替换为 dc/dc 转换器,则 dc/dc 转换器的输入电流是其输出电流乘以占空比,D=VOUT/VIN,忽略损耗并在一个开关周期内取平均值。因此,为该 dc/dc 转换器供电的上游 dc/dc 转换器在其输出上经历较低的负载瞬变,并且上游 dc/dc 转换器对其 VOUT 的干扰较小。因此,LDO 可能比 dc/dc 转换器噪声更大,但不是在其输出上,而是在为其供电的上游转换器的输出上。因此,为该 dc/dc 转换器供电的上游 dc/dc 转换器在其输出上经历较低的负载瞬变,并且上游 dc/dc 转换器对其 VOUT 的干扰较小。因此,LDO 可能比 dc/dc 转换器噪声更大,但不是在其输出上,而是在为其供电的上游转换器的输出上。因此,为该 dc/dc 转换器供电的上游 dc/dc 转换器在其输出上经历较低的负载瞬变,并且上游 dc/dc 转换器对其 VOUT 的干扰较小。因此,LDO 可能比 dc/dc 转换器噪声更大,但不是在其输出上,而是在为其供电的上游转换器的输出上。

LDO 对低噪声模拟前端 (AFE) 的热效应

LDO 通常用于为 AFE 提供安静的电源轨。LDO 中的功耗仅由 Iout(VIN-VOUT) 给出,负载电流远大于 LDO 的静态电流。如果负载电流 (Iout) 很大和/或 VIN-VOUT 差异很大,则耗散功率可能很大。随着 IC 封装趋于小型化,LDO 中的温升可能会非常显着,从而导致印刷电路板 (PCB) 上出现热点。热量通过 LDO 封装散热焊盘连接到的接地层从 LDO 扩散到 PCB。AFE 的一个关键性能指标是它们的信噪比(S/N 比)。噪声电压的一个分量是 Johnson/Nyquist 噪声,由 V(rms) = sqrt(4kTBR) 给出,其中 T 是以开尔文为单位的绝对温度,B 是带宽,R 是电阻,k 是玻尔兹曼常数。将热 LDO 靠近 AFE 放置也会使 AFE 的温度升高,增加噪声,降低 S/N,对系统的整体性能有明显的影响。虽然将 LDO 放置在靠近 AFE 的位置很好,但应避免将其放置得太近。对于拥挤的 PCB,还考虑移除一些铜接地层以防止热量传递到 AFE,但要适度,以免干扰从 AFE 到 LDO 的接地返回电流路径。

结论

本文重点介绍了在系统中应用 LDO 时需要注意的三个问题。LDO 仍然是电源转换的绝佳选择,但像往常一样,最好了解并避免此类应用问题。

我要赚赏金

我要赚赏金