旁路电容是关注度低、没有什么魅力的元器件,一般来说,在许多专题特写中不把它作为主题,但是,它对于成功、可靠和无差错的设计是关键。

来自Intersil公司的作者David Ritter和Tamara Schmitz参加了关于该主题的进一步对话。本文是对话的第一部分。Dave和Tamara信仰辩论的价值、教育的价值以及谦虚地深入讨论核心问题的价值。

简而言之,为了获取知识而展开对一个问题的讨论,下面请“聆听”并学习。

David: 有一种观念认为,当我们做旁路设计时,我们对低频成分要采用大电容(微法级),而对高频成分要采用小电容(纳法或皮法级)。

Tamara: 我赞成,那有什么错吗?

David: 那听起来很好并且是有意义的,但是,问题在于当我在实验室中验证那个规则时并未得到我们想要的结果!我要向您发出挑战,Tamara博士。

Tamara: 好啊!我无所畏惧。

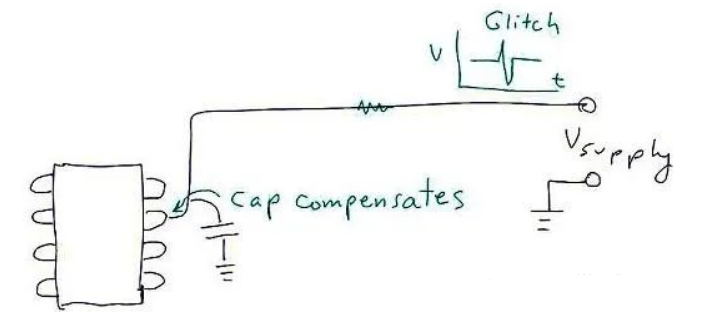

David: 让我们看看,你有一个电压调整器并且它需要电源。电源线具有一些串联阻抗(通常是电感以及电阻),这样对于短路来说,它在瞬间提供的电流就不会出现大变化。它需要有一个局部电容供电,旁路电容功能如下图所示。

Tamara: 我到目前均赞成你的观点。那就是旁路的定义。Dave,接着说吧。

David: 例如,有些人可能用0.1 μF电容进行旁路。他们也可能用一个1000pF的电容紧挨着它以处理更高的频率。如果我们已经采用了一个0.1 μF的电容,那么,紧挨着它加一个1000pF电容就没有意义。它会增加1%的容值,谁会在意?

Tamara: 然而,除了电容值之外,有更多要研究的内容。这两种数值的电容均不理想。

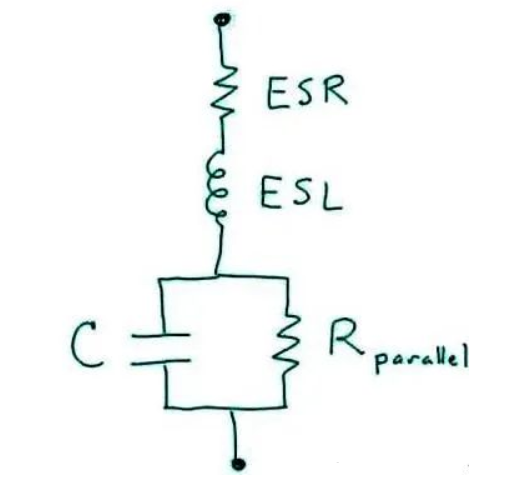

David: 我们必须考察0.1 μF的实际电路;它存在有效串联电阻(ESR)以及有效串联电感(ESL)。

Tamara: 有时候,你还要把介质损耗一项当成一个并联电阻来考虑,旁路电容的模型如下图所示。

David: 现在,当我们遇到具有瞬态特性的这一损耗时,我们假设0.1 μF电容的ESL远远大约1000pF的电容。我们需要某一器件在短期内供电,因ESL的存在而让0.1 μF的电容做不到这一点。假设就在于1000pF的电容具有更低的ESL,因此,能够提供更好的电流。

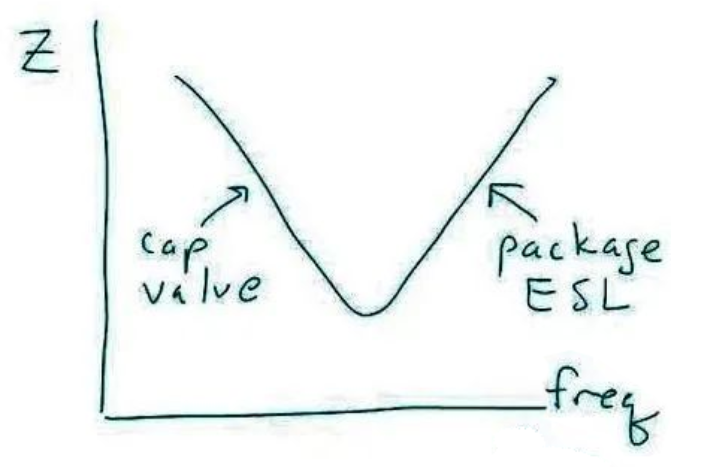

Tamara: ESL与你获得以及封装的电容的类型有关。其数值可能完全独立于电容本身的尺寸和数值,旁路电容的阻抗如下图所示。

David: (显示出对年轻同事所具有的知识的惊讶)

Tamara: 我曾经看到过一些人把100 nF、10 nF和1 nF的电容分级并联起来使用,它们可能均采用相同的封装,例如0402,因为这些电容通常就是采用这种封装形式。然而,每一种0402封装均具有相同的ESL,因为它们具有相同的电感以及相同的高频响应,因此,这么安装电容于事无补。

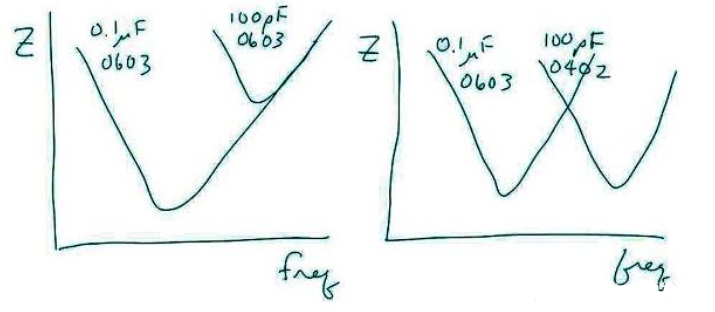

David: 我们在实验室中所发现的问题在于,各种封装均是类似的。我们所采用的大多数陶瓷电容均为面积是0805或0603的电容。我测试发现,把0603 0.1 μF电容挨着0603 100pF电容安装,效果上不如仅仅采用两个0603 0.1 μF的电容。

Tamara: 那是完全有可能。我猜测,你所处的频率范围就是0603 0.1 μF电容被最优化的频率范围。相同尺寸和不同尺寸的电容的阻抗比较如下图所示。

David: 是的,ESR和ESL是原数值的一半且非常管用。在这些应用中,我所研制的开关调整器的工作频率大约为1MHz。

David: 是的,ESR和ESL是原数值的一半且非常管用。在这些应用中,我所研制的开关调整器的工作频率大约为1MHz。

Tamara: 在你的情况下,要调整电容的数值以及封装,以改善对你没有兴趣的那个频率范围的旁路网络。图4假设我们谈论的是相同类型的电容(陶瓷电容)。其它类型的电容—如钽电容—具有更高的ESR,因此,整个曲线突起。另一方面,有时可能全部要采用钽电容。

David: 我们现在讲讲历史。过去,人们采用他们手上能用的一切元器件。那时,你无法获得封装小的100 μF电容,你不得不通过缩短旁路电容器上的引线来改善旁路网络。当今的大电容的尺寸正逐渐缩小类似于较小电容所具有的尺寸。当你开始认真考虑选择一只0.1 μF电容时,你肯定选择0603的封装,并且,最终会选择0402封装的电容(因为我没有看过0402封装的电容,我倾向于不采用那些电容)。

Tamara: 按照分级封装的阶梯电容(stepped capacitor)的确切含义来自于赛灵思公司的讨论。他们的FPGA被用于各种各样的应用之中,并且,他们设法测试了所有的条件。因此,他们在高达5Gsps的宽频带内需要一种低阻抗电容对电源旁路。另一方面,你需要一种较低带宽的解决方案。

David: 我的评论全部来自较之于比赛灵思的速度更低的电源应用。你的辩论非常聪明,因为你指的是封装尺寸,而其他人没有那么深入的思考。他们通常说,高频需要小电容,而低频需要大电容。

Tamara: 啊,真是的,我要脸红了。

David: 我的旁路事业一直是非常令人厌烦的,因为在大多数时间内,规则就是用0.1 μF电容旁路每一个芯片,那就管用了。

Tamara: 那不仅仅与封装有关,而且还与布局有关。

David: 绝对正确!我循着电路板上的电流路线,发现电路板上存在电感。在任何电流路径上的电感与该路径的闭环面积呈正比。因此,当你围绕一个区域对元器件进行布局时,你需要把元器件紧凑地布局。那就是你为什么把元器件保持紧凑布局的原因—保持电感为低。然后,选择具有良好ESL和ESR的电容。我希望对于它有更多的设计艺术,但是,它的确是实用证明正确的少数的简单规则之一。

Tamara: 当然,你可以购买具有较低ESL和ESR的电容,但是,他们通常比标准的陶瓷电容更为昂贵。

David: 在大多数情形下,与每一块芯片尽可能接近的0.1 μF旁路电容仍然非常管用。继续关于排版的讨论 Tamara博士拿着一袋发着沙沙响声的书进入她的办公室,当Dave从旁边走过时她把那袋书扔在了桌子上。Dave: 嗨,Tamara:博士,你往那里扔什么?

Tamara: 那是我们的读者邮件。

Dave: 我们收到邮件?你的意思是喜欢“来自新泽西Fort Lee的Richard Fader写道:这就是我听说的关于电容器的一切抱怨吗?”之类的邮件?

Tamara: 是的,就是那样的信件。

Dave: 关于电容器以及排版吗?

Tamara: 当然!这是一封来自Kyle(所有读者的姓名被改变,以保护他们隐私)。在高幅度射频场中,他惯常于把电容器级联起来以旁路他的电路。

Dave: 正如我们所说的,有时候你需要这么做,但是,许多时间你不需要这么做。

Tamara: 他也问到了耦合电容。看来他们在耦合电容上遇到的问题不如在旁路电容上遇到的问题大。

Dave: 是的,我已经注意到了那个问题,但是,一些人担心采用大的耦合电容,因为它太慢。我认为,他们的思路不正确。

Tamara: 在今后的讨论中我们将着手解决那个问题。这里是Carl的评价。他对我们最近关于接地平面上的电压降问题提出的解决方案感到不确定。他认为,在它(感应作用)周围或者需要磁通,或者它仅仅是一个通常很小的IR降。

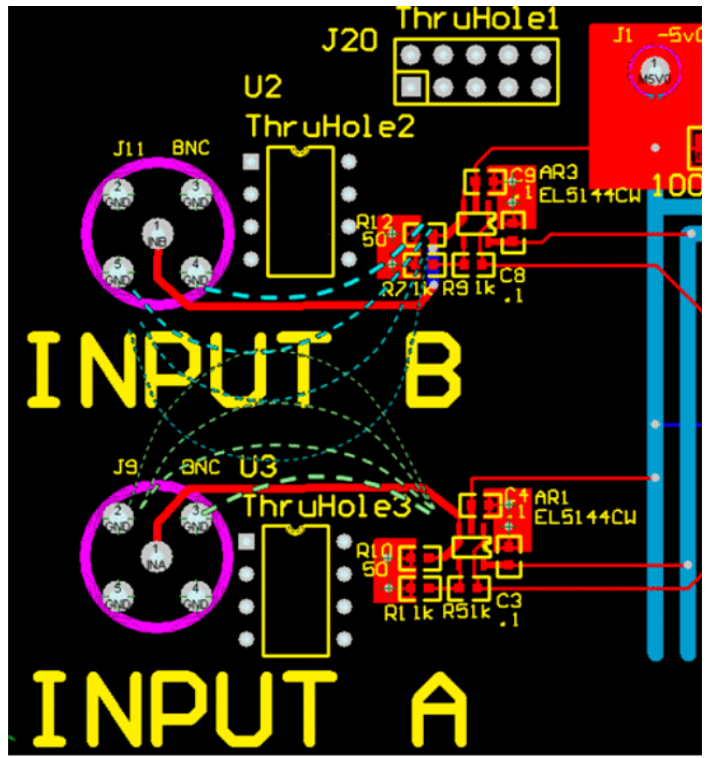

Dave: 是的,我们通常在视频系统中谈到的60dB的串扰非常小,意味着有几个毫伏的有害信号。上次在例子中我们证明了,为了便于描述,我们把电路做了相当多的简化。实际电路在每一个通道具有完整的直流恢复(具有电子机械继电器),并且它是通孔元件。视频混合器的PCB排版图如下。边缘电流线显示出现串扰的可能性;带引脚的元件破坏接地层,并把电流线聚集在一起。可见,当通孔元件或过孔破坏了一个接地层时会发生什么情况。

Tamara: 你的意思是你不用表面贴装元件,因此,接地层上充满了带引脚的元件的通孔?

Dave: 是的,来自输入的大多数回流通过围绕这个电路的窄带之中。与实体接地层相比,电阻要更大。

Tamara: 因此,边缘电路被更多地拥挤在一起。

Dave: 是的。串扰比你想像的要多。表面安装的元件对解决这个问题有很大帮助,因为它们具有更少的通孔,但是,把接地层分开是明智且容易的事情,并且不论你是否拥有大量的过孔它均能消除这个问题。视频混合电路板利用分开的接地层来把串扰最小化,如下图所示。

Tamara: 免费、容易且有效—听起来就像放之四海皆准的惯例。

Dave: 那真是我一直思考的事情。你在哪个领域取得了什么进展?

Tamara: 我已经跟两家电容器公司X2Y以及KEMENT的代表进行了接触。

Dave: 他们怎么想的?

Tamara: 我们在旁路电容上花费了太多的精力,你不知道你怎么想的吗?

Dave: 啊,是的,我的意思是它们仅仅是电容器。

Tamara: 他们说,我们的研究不够。我们仅仅考虑两维。他们甚至要考虑电容器内部的侧景(side view)。

Dave: 他们重视我们建议的那样的电流路径吗?

Tamara: 是的,通过减少他们的电容器的引脚的垂直封装面积,他们把等效串联电感(ESL)的标准数值从大约2nH降低为原来的1/5。

Dave: 因此,即使专业公司也重视该电流(如释重负地叹息)。我们站在可巨人的肩膀上(停顿,心不在焉地凝视远方…)

Tamara: Dave. . . . DAVE. .

Dave: 哦,对不起。那么,现在我们在哪里跟踪电流路径,Tamar博士。

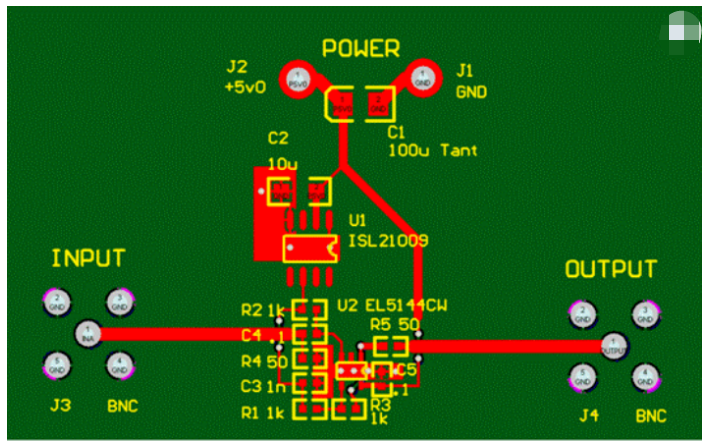

Tamara: 我认为,我们需要做稍微深入的讨论,并通过一个例子分步讨论。我认为,我们的读者了解电流路径对于放置他们的旁路电容是至关重要的,但是,可能需要一个实例。让我们看看在一个简单的电路中,电流是在哪里流过的。让我们看看驱动一个负载的运放的输出。下面是一块简单的电路和电路板。

Dave: 好,让我们把讨论做的有趣一些。对于输入偏置级的电压参考来说,怎么样?

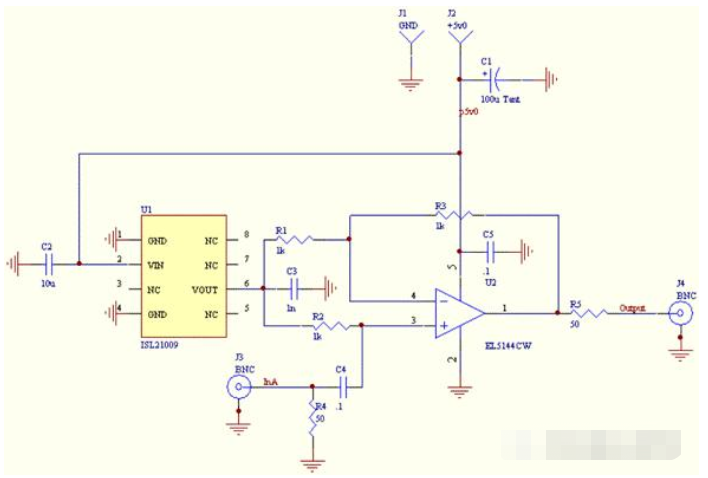

Tamara: 简单的运算放大器以及电压参考电路,如下图所示,为具有增益为2的单电源运放配置。

Dave: 电压参考偏置均以电源电压的一半来输入以获得最佳的输入范围。

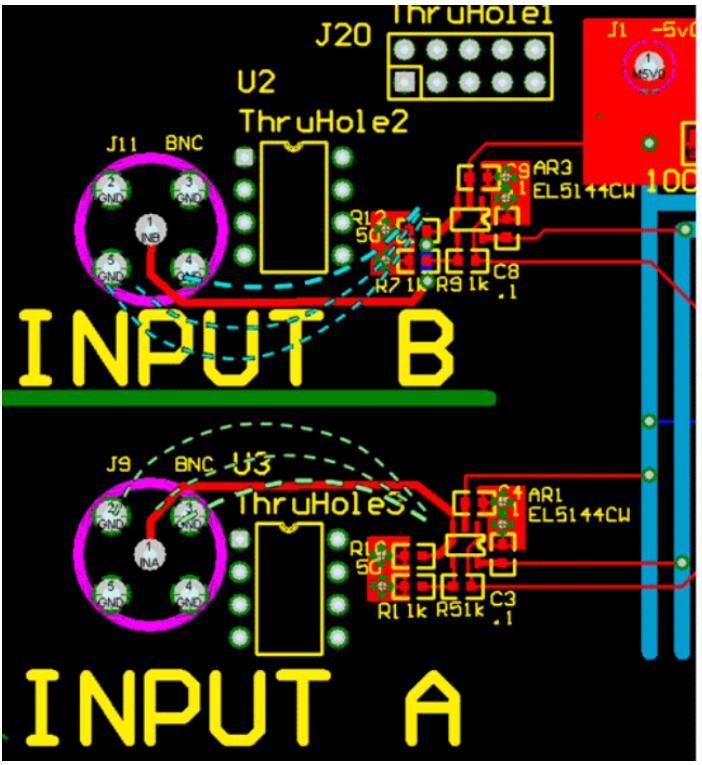

Tamara: 这次我们为排版选择采用双层电路板(上次那块板子采用四层板)。第二层几乎是完整的接地层,在输入和输出线上是两条跳线,单运放及其电压参考电路的印刷电路板排版如下图所示。

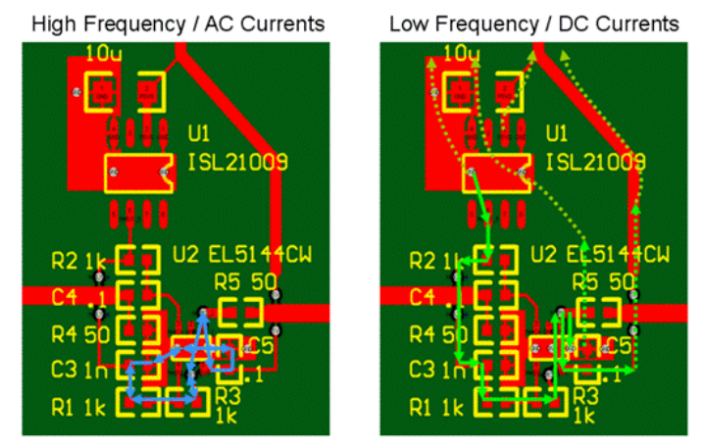

Dave: 让我们跟踪电流的路径,在参考电压中的交流以及直流路径分别如下左右两图。

Tamara: 工程师们有时会混淆交流以及直流路径,因此,让我们把交流高频路径标记为蓝色,而把直流路径标记为绿色。

Dave: 我要深入探讨一下。我用实线把驱动电路标出,因为它们的电流大多数在顶层流动并且回路用虚线表示,因为它们在接地层上的流动占突出地位。

Tamara: 你真厉害!

Dave: 你可能认为,参考电源仅仅是直流电源,但是,它也是放大器中交流电路的一部分。要核查在参考电路中的高频电流路径。

Tamara: 我特别想知道,无源元件的堆叠如何让你干净地引入输入线并在U2、R4、C3和C5之间共享一小块接地焊盘。

Dave: 那并没有阻止我构建一条从R3至那个输入网络的紧凑(布局很好)的反馈路径。

Tamara: 高频路径是短且紧凑的,其环路通过输出旁路电容器C5以及参考旁路电容器C3。我猜测那就是为什么你把C3放在放大器U2附近,而不是放在上面的参考芯片U1旁边。在顶层上它们甚至共享额外的接地连接。

Dave: 没错。我们想要高频电流包含小的闭合面积,这意味着电感小。为了形成对照,请参见直流电流的回路。

Tamara: 它们在整块板子上展开并且甚至似乎离开电路板的顶层。

Dave: 是!直流电流必须来自电源,那意味着它进入并离开连接器或找到它流去本地电源调整器的途径。在任一情形下,路径的面积均大。

Tamara: 那就是为什么我们在第一个地方采用旁路电容器:把高频电流保持在本地,并分流会引起大量不希望出现的电压降的感性以及阻性路径。

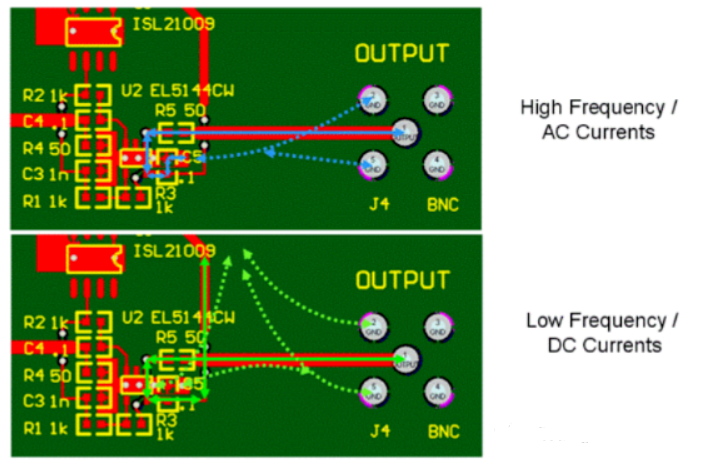

Dave: 现在,请看以下放大器的输出电流,在在运放中的交流以及直流路径分别如下两图所示。

Tamara: 再看看在电路板顶层上展开的直流电流(在连接电源的地方),但是,在紧凑的环路中交流电流非常接近输出放大器。

Dave: 交流回路除非在接地层上展开,否则不会依靠自己或跨越它自己构成回路。那就是最小化串扰的良好实践。

Tamara: 这一次在你的接地层上没有出现你的著名的切割,为什么没有?

Dave: 那个信号的确没有机会相互作用。信号流直接从左边流向右边—输入至输出。我们没有画出输入电流路径,这留给读者做练习。

Tamara: 然而,如图2所示的接地层切割在把信号线围起来并防止边缘电流相互作用上最为有用。

Dave: 绝对正确。可是,不要忘记这整个对话是从旁路电容器开始讨论的。

Tamara: 是的,的确如此。我们能够选择正确的电容器的尺寸、类型和封装,然而,如果我们不对排版进行最优化的话,那也不会有效。

Dave: 那可能是我们能够说的最重要的事情:关于放置旁路电容器的问题几乎总是可以通过跟踪电流的路径并最小化电流的环路面积来回答。除此之外,没有更多的其它问题。

我要赚赏金

我要赚赏金