那么,是否能首先进行输出纹波电压相关的说明?因为流过的电流与输入不同,如果能像介绍输入电容器时那样,从输出电容器流过的电流开始说明的话,更容易理解。以降压转换器为例。首先请看电源电路与纹波的波形成分示意图。通过输出段晶体管开关产生三角波的电感电流,标为DC的电感平均电流通往输出,其三角波部分作为AC流过输出电容器。其下面的波形图表示三角波的电容器电流受电容器的寄生成分ESL和ESR、以及电容成分影响产生了怎样的电压。 三角波的电容器电流受ESL影响产生矩形波电压。有些ESR产生符合欧姆定律的三角波电压,有些电容容量具有时间常数。最终形成这3种成分的合成波。简而言之,急剧上升是ESL产生的,带有斜率的变动是ESR产生的,并分别根据电容容量而产生二次曲线变化。下面的波形图是实际的纹波电压波形。从波形的形态可以看出哪个部分受什么影响较大。这是为了改善此类纹波所需要了解的技术知识,所以要记住。

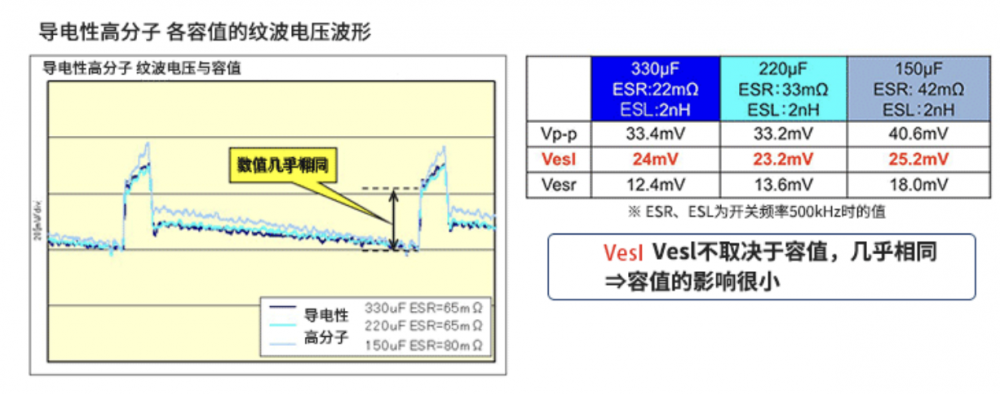

三角波的电容器电流受ESL影响产生矩形波电压。有些ESR产生符合欧姆定律的三角波电压,有些电容容量具有时间常数。最终形成这3种成分的合成波。简而言之,急剧上升是ESL产生的,带有斜率的变动是ESR产生的,并分别根据电容容量而产生二次曲线变化。下面的波形图是实际的纹波电压波形。从波形的形态可以看出哪个部分受什么影响较大。这是为了改善此类纹波所需要了解的技术知识,所以要记住。 上方的波形是电感电流,下方的波形是输出产生的纹波电压。急剧上升的部分是由ESL产生的Vesl。之后的增量部分是由ESR所产生的Vesr。其合计是纹波电压的峰值Vp-p。此时的输出电容器是导电性高分子型,容值是330µF。ESR是22mΩ,ESL是2nH,二者都是开关频率为500kHz时的值。另外,表格中是实际的电压变动值。如红色值所示,Vesl是Vesr的近2倍,占了整个纹波电压Vp-p的2/3。由于这些数值会随频率等条件而改变,所以请理解为仅仅是一个例子。ESL的影响更大吗?经常听说由于输出电压的纹波取决于ESR,所以要使用ESR较低的输出电容器。这是正确的理解。在该例中,ESR也产生了Vesr。但是,在一些条件下,Vesl所占纹波电压的比例会变大。以上了解了ESR与ESL的影响,电容容量是如何影响的呢?这是表示电容容量与纹波电压关系的数据。电容器是导电性高分子型,容值是330µF、220µF、150µF。从波形图和表格可以看出,几乎没有出现Vesl的变化。这表明Vesl几乎不取决于容量。

上方的波形是电感电流,下方的波形是输出产生的纹波电压。急剧上升的部分是由ESL产生的Vesl。之后的增量部分是由ESR所产生的Vesr。其合计是纹波电压的峰值Vp-p。此时的输出电容器是导电性高分子型,容值是330µF。ESR是22mΩ,ESL是2nH,二者都是开关频率为500kHz时的值。另外,表格中是实际的电压变动值。如红色值所示,Vesl是Vesr的近2倍,占了整个纹波电压Vp-p的2/3。由于这些数值会随频率等条件而改变,所以请理解为仅仅是一个例子。ESL的影响更大吗?经常听说由于输出电压的纹波取决于ESR,所以要使用ESR较低的输出电容器。这是正确的理解。在该例中,ESR也产生了Vesr。但是,在一些条件下,Vesl所占纹波电压的比例会变大。以上了解了ESR与ESL的影响,电容容量是如何影响的呢?这是表示电容容量与纹波电压关系的数据。电容器是导电性高分子型,容值是330µF、220µF、150µF。从波形图和表格可以看出,几乎没有出现Vesl的变化。这表明Vesl几乎不取决于容量。 也就是说,基本上要使用ESR和ESL较小的电容器吧。的确如此。前面已经介绍过叠层陶瓷电容器的特征,低ESR、低ESL的MLCC-叠层陶瓷电容器对降低纹波电压非常有效。这是近年来叠层陶瓷电容器作为主要的输入输出电容器使用不断增长的原因。下面的波形图是导电性高分子电容器与叠层陶瓷电容器的纹波电压比较和阻抗特性上叠加了电感电流的频谱示意图。

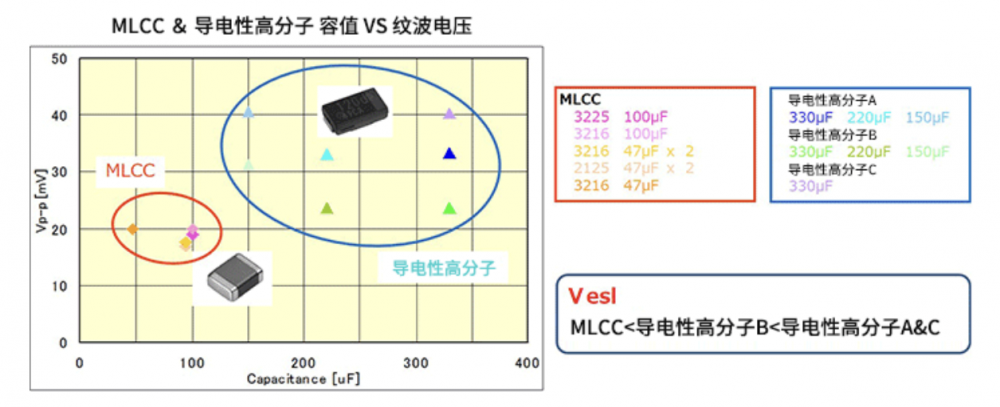

也就是说,基本上要使用ESR和ESL较小的电容器吧。的确如此。前面已经介绍过叠层陶瓷电容器的特征,低ESR、低ESL的MLCC-叠层陶瓷电容器对降低纹波电压非常有效。这是近年来叠层陶瓷电容器作为主要的输入输出电容器使用不断增长的原因。下面的波形图是导电性高分子电容器与叠层陶瓷电容器的纹波电压比较和阻抗特性上叠加了电感电流的频谱示意图。 纹波电压波形中可以看出,粉色系所示的叠层陶瓷电容器的Vesl明显很低,Vesr的梯度也较小。当然,如阻抗特性图与表格数值所示,ESR和ESL也较小。阻抗特性图中,细线表示ESR。该例中由于开关频率是500kHz,可以知道电感电流的频谱里存在从500kHz的基本波到高次谐波。由于其范围是高于谐振点的频率,所以可以理解ESL的影响较大的原因。另外,下面用映射图表示其与电容容量的关系。

纹波电压波形中可以看出,粉色系所示的叠层陶瓷电容器的Vesl明显很低,Vesr的梯度也较小。当然,如阻抗特性图与表格数值所示,ESR和ESL也较小。阻抗特性图中,细线表示ESR。该例中由于开关频率是500kHz,可以知道电感电流的频谱里存在从500kHz的基本波到高次谐波。由于其范围是高于谐振点的频率,所以可以理解ESL的影响较大的原因。另外,下面用映射图表示其与电容容量的关系。 从该映射图可以知道,MLCC-叠层陶瓷电容器非常有助于降低纹波电压Vp-p,容量与Vesl几乎不存在依存性。顺便说一句,导电性高分子型在代表性的3个品牌中,几乎没有由容量产生的Vesl差异,而不同品牌的ESL有差异。看了该比较后注意到,也就是说如果用叠层陶瓷电容器替换导电性高分子电容器,不需要相同容值是吗?这是非常重要的要点。从纹波电压的角度看,由于叠层陶瓷电容器的ESR、ESL都很小,对于原来的导电性高分子型可以用更低的容量来替换。容量不仅影响尺寸,还会影响成本。在一些条件下,通过使用叠层陶瓷电容器,减小纹波的同时还可以实现小型化并降低成本。

从该映射图可以知道,MLCC-叠层陶瓷电容器非常有助于降低纹波电压Vp-p,容量与Vesl几乎不存在依存性。顺便说一句,导电性高分子型在代表性的3个品牌中,几乎没有由容量产生的Vesl差异,而不同品牌的ESL有差异。看了该比较后注意到,也就是说如果用叠层陶瓷电容器替换导电性高分子电容器,不需要相同容值是吗?这是非常重要的要点。从纹波电压的角度看,由于叠层陶瓷电容器的ESR、ESL都很小,对于原来的导电性高分子型可以用更低的容量来替换。容量不仅影响尺寸,还会影响成本。在一些条件下,通过使用叠层陶瓷电容器,减小纹波的同时还可以实现小型化并降低成本。

共10条

1/1 1 跳转至页

输出纹波评估要注意输出电容器的ESL

开关电源电路中,不言而喻输出电容器也和前面提到的输入电容器一样,也是必须有的部件。和输入电容器的思路相同,也需要考虑静电电容以及ESR和ESL这样的寄生成分的影响。但是,和输入相比,由于有施加电流波形和负载等不同点,因此所发生的电压变动和现象也不同。不管怎样,如何将输出所产生的电压变动抑制在最小是要解决的课题。具体而言,需要着眼于输出纹波电压与负载瞬态响应。

关键词: 输出 纹波 评估

共10条

1/1 1 跳转至页

我要赚赏金

我要赚赏金