作者:Michael Peffers

欢迎阅读《模拟线路》(Analog Wire) 上《获得连接》博客系列的第四篇文章!我们在上篇博客中探讨了一些随机抖动的测量技术以及实验室中确定性抖动的组成部分。在这篇博客中,我们将讨论 MLVDS、类似标准,并将介绍一种实用 MLVDS 应用。

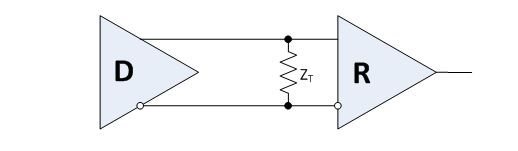

我们在考虑通信链路中的合理架构时,会想到三种拓扑:点对点、多支路和多点。创建 TIA/EIA-644 或 LVDS 的目的是为点对点拓扑中的驱动器和接收器提供通用电气层规范。点对点拓扑是一种半双工链路,包含支持差分端接的单个驱动器及接收器。下图 1 是一个点对点配置:

图 1:点对点

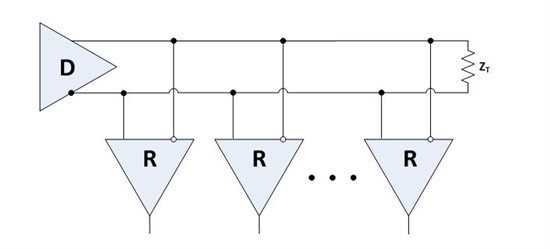

下一种架构是多支路拓扑。LVDS 标准在开发时并没有考虑多支路拓扑,因此 TIA/EIA-644 标准在 2001 年进行了升级,可在 TIA/EIA-644-A(LVDS、REV-A)标准中支持多支路。升级版 TIA/EIA-644-A 针对驱动器要求进行了标准化,将 LVDS 接收器的差分输入漏电流限制在 6uA。多支路半双工链路包含一个单驱动器,可通过远离驱动器、位于链路远端的一个端接电阻器与多个接收器通信。下图 2 是多支路配置:

图 2:多支路

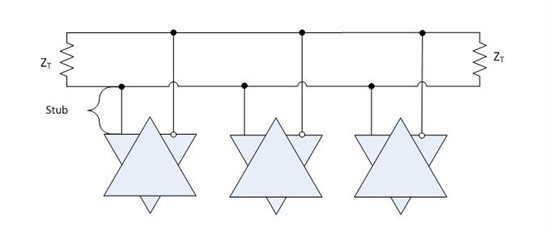

第三种架构是多点拓扑,其需要一个已制定的 TIA/EIA-899 (MLVDS) 标准。多点架构是半双工链路,在相同总线中包含多个驱动器与多个接收器,端接电阻器位于总线的两端。在该拓扑中必须采用双端接,以支持位于整个传输线路中不同点的多个驱动器。由于这两个端接电阻以并联形式连接,因此多点驱动器所能看到的有效电阻仅为 50Ω,而 LVDS 应用中使用的则是 100Ω。算上共享一个总线的多个收发器的附加负载,驱动器负载可能只有 30Ω。由于降低了负载,MLVDS 驱动器可提供 565mV 的典型差分输出电压,大于 LVDS 驱动器所应支持的最大差分电压,而且它们可将 24mA 至 43mA 的短路电流提高近一倍。由于有的周期内总线部分没有活动驱动器,因此电路的共模电压由附加组件来控制,而附加组件会在共模失调电压中引起大于正常值的移位。MLVDS 标准支持 ±1V 的接地噪声失调,允许 MLVDS 电路的共模电压变化范围在 -1V 至 3.4V 之间,而非 LVDS 电路中所支持的共模电压的 0–2.4V。

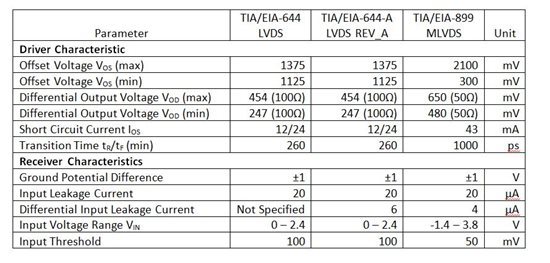

多点应用中另一个需要考虑的问题是主传输线所产生的较长残段,其可为设计人员带来严重的信号完整性问题。一般建议尽量保持较少的残段,确切来说就是建议使残段保持在信号传输时间的 30%。为达到该标准,MLVDS 允许进行边缘速率控制,将最短传输时间规定在 1ns 内。1ns 传输时间意味着 MLVDS 系统中预期的最大信号速率是 500Mbps,但残段可能会达到几乎两英寸,不违反 30% 的指导要求。下图 3 是多点配置,下表 1 总结了上述 LVDS 与 MLVDS 之间的区别:

图 3:多点配置

表 1

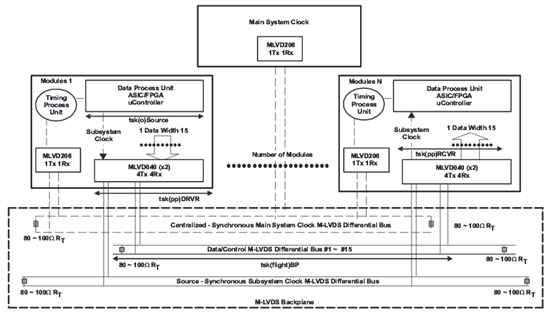

SN65MLVD206 和 SN65MLVD040 均为半双工 MLVDS 收发器,支持 30Ω 至 55Ω 负载范围,信号传输速率分别高达 200Mbps 和 250Mbps。下图 4 是使用 MLVDS 的典型应用。在该方案中,SN65MLVD206 用来通过系统基架将来自主系统时钟的同步时钟分配给 NPU、ASIC 以及 FPGA 等。两个 SN65MLVD040 器件可用于每个线卡,以处理通过基架与系统中另一个点进行通信的 16 位宽数据总线。这很容易明白为什么要制定 TIA/EIA-899 标准、为什么 MLVDS 适合下图 4 中这样的应用:

图 4:典型 MLVDS 应用

原文请参见:

http://e2e.ti.com/blogs_/b/analogwire/archive/2014/04/16/get-connected-lvds-for-multipoint-applications.aspx

我要赚赏金

我要赚赏金