在DC-DC芯片的应用设计中,PCB布板是否合理对于芯片能否表现出其最优性能有着至关重要的影响。不合理的PCB布板会造成芯片性能变差如线性度下降(包括输入线性度以及输出线性度)、带载能力下降、工作不稳定、EMI辐射增加、输出噪声增加等,更严重的可能会直接造成芯片损坏。

一般DC-DC芯片的使用手册中都会有其对应的PCB布板设计要求以及布板示意图,本次我们就以同步BUCK芯片为例简单讲一讲关于DC-DC芯片应用设计中的PCB Layout设计要点。

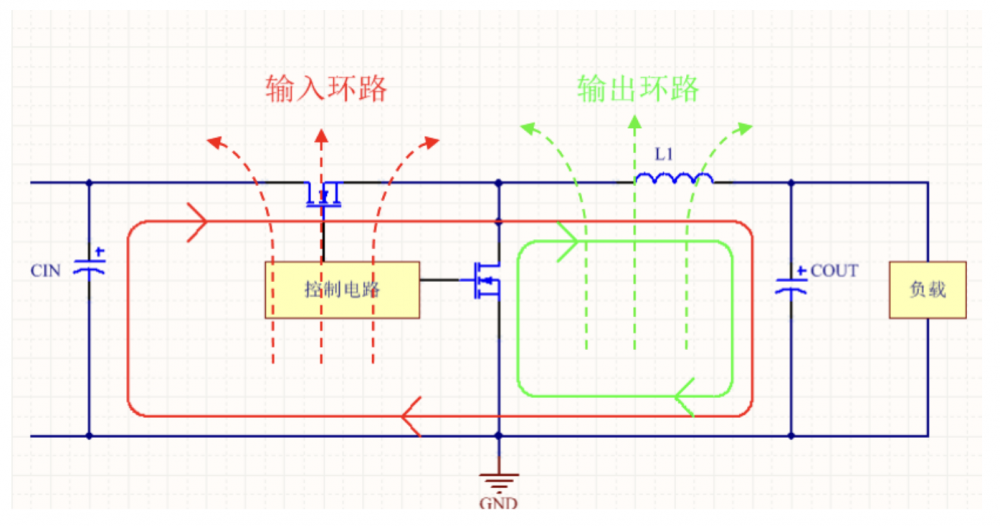

1 关注芯片工作的大电流路径 DC-DC芯片布板需遵循一个非常重要的原则,即开关大电流环路面积尽可能小。下图所示的BUCK拓补结构中可以看到芯片开关过程中存在两个大电流环路。红色为输入环路,绿色为输出环路。每一个电流环都可看作是一个环路天线,会对外辐射能量,引起EMI问题,辐射的大小与环路面积呈正比。 注意:当芯片引脚设置不足以让我们同时兼顾输入环路与输出环路最小时,对于BUCK而言,应优先考虑输入部分回路布线最优化。因为输出回路中电流是连续的,而输入回路中电流是跳变的,会产生较大的di/dt,会引起EMI问题的可能性更高。如果是BOOST芯片,则应优先考虑输出回路布线最优化。2 输入电容的配置

注意:当芯片引脚设置不足以让我们同时兼顾输入环路与输出环路最小时,对于BUCK而言,应优先考虑输入部分回路布线最优化。因为输出回路中电流是连续的,而输入回路中电流是跳变的,会产生较大的di/dt,会引起EMI问题的可能性更高。如果是BOOST芯片,则应优先考虑输出回路布线最优化。2 输入电容的配置

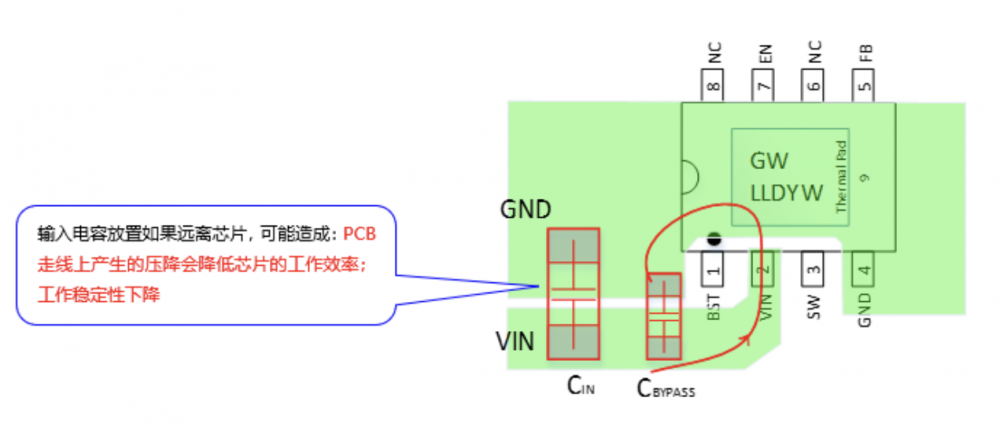

- 对于BUCK芯片而言,要想使输入环路尽可能小,输入电容应尽可能靠近芯片引脚放置

- 为了让电容滤波效果更好,让电源先经过输入电容,再进入芯片内部

- CIN 使用的大容量电容器,一般情况下频率特性差,所以要与 CIN 并联频率特性好的高频率去耦电容器 CBYPASS

- 电流容量小的电源(IO≤1A)场合,容量值也变小,所以有时可用1个陶瓷电容器兼具CIN 和 CBYPASS 功能

3 电感的配置

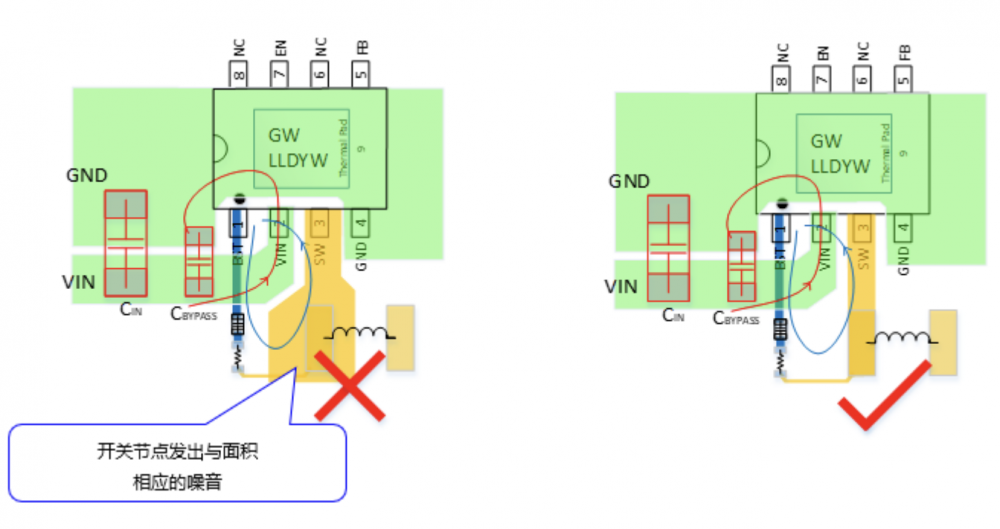

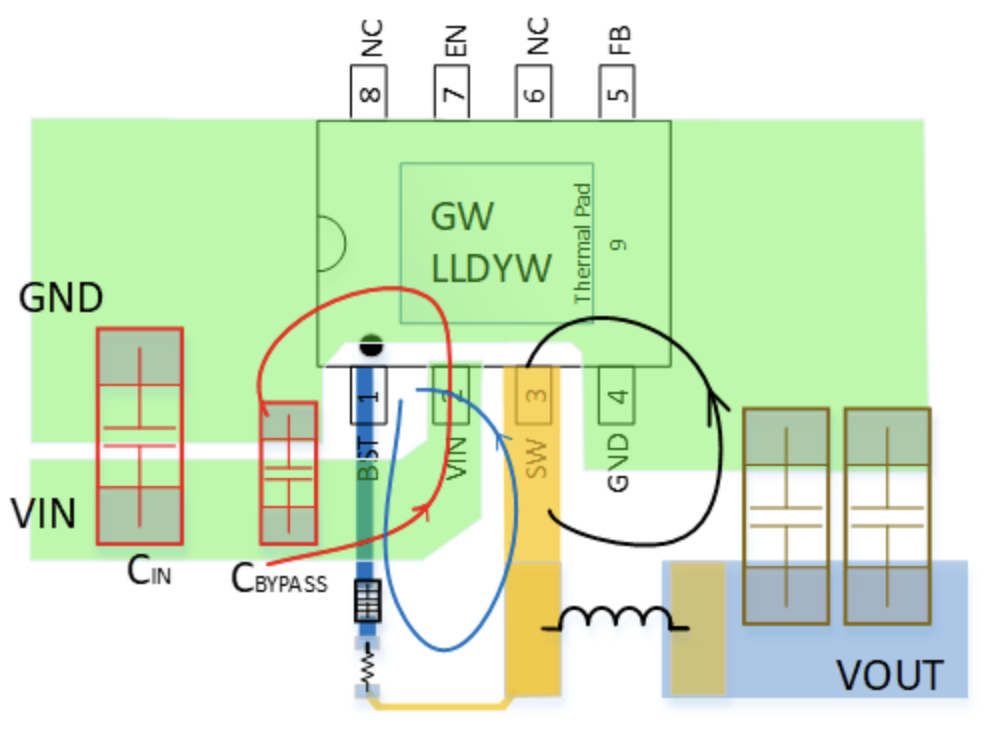

3 电感的配置- 对于BUCK芯片而言,要想使输入环路尽可能小,电感要靠近芯片SW引脚放置

- 以覆铜方式走线减小寄生电感、电阻

- SW节点要以最小面积处理大电流,防止铜箔面积变大会起到天线的作用,使 EMI 增加

- 电感附近不要走敏感信号线

- 自举电路这一块,自举电路要尽量去靠近 SW pin 脚来缩短整个高频的流通路径

附上温升10℃时,PCB板的线宽、覆铜厚度与通过电流的对应关系供参考。

附上温升10℃时,PCB板的线宽、覆铜厚度与通过电流的对应关系供参考。

- 降压转换器中,由于向输出串联接入电感器,所以输出电流平滑

- 输出电容靠近电感放置

- 通常FB反馈网络处的分压电阻都采用K级,10K级或上百K的阻值,阻值越大,越容易受干扰,应远离各种噪声源如电感、SW、续流二极管等

- FB、COMP脚的信号地尽可能地与走大电流的功率地隔离开,然后进行单点相连,尽量不要让大电流信号的地 去干扰到小信号电流的地

- FB的分压电阻要从VOUT上进行采样,采样点要靠近输出电容处才能获得更准确的实际输出电压值

我要赚赏金

我要赚赏金