在进行电子产品整体设计过程中,因为本身具有很高的复杂性且包含了许多专业技术,所以在电子产品“可组装性设计”是必不可少的一部分。

可组装性需要结合制造工艺的因素考虑,准确掌握电子产品设计时可能造成的可组装性影响,因此需在设计端提前对可组装性做分析,避免后期制造端存在无法组装等问题。

在设计时进行可组装性分析可以有效落实电子产品的预期效果,让生产的电子产品可以更好的满足人们的要求,可以让电子企业在竞争热烈的市场上站稳脚跟,从而促进企业的长期发展。

组装分析是面向装配的设计,英文(Design for assembly)简称DFA,是指在产品设计阶段设计的产品具有良好的可装配性,确保装配工序简单、装配效率高、装配质量高、装配不良率低和装配成本低。

“华秋DFM”的组装分析设置功能是协助EDA电路设计元件清单的整理,快速的匹配Bill of Materials(BOM)的元器件,能大大提高整理Bill of Materials(BOM)的工作效率。

当然,“华秋DFM”不仅仅是整理Bill of Materials(BOM)那么简单。主要的功能提供了组装分析,支持检查元器件组装时存在的隐患,提前分析检查可避免组装过程中因设计带来不必要的损失。

DFM组装分析检查项案例分享

华秋DFM的组装分析设置,针对PCBA组装的分析项开发了10大项,234细项检查规则,检查规则基本可涵盖所有可能发生的组装性问题。以下为大家介绍几个组装分析帮用户解决问题的经典案例。

(一)

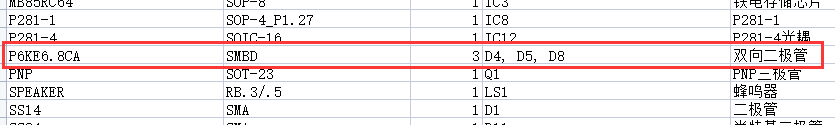

BOM跟封装不匹配,用户的BOM表里面的型号是P6KE6.8CA,位号D4、D5、D8设计的PCB封装是DFN1610贴片二极管封装,BOM表里面的型号P6KE6.8CA实际是插件双向二极管封装,因此设计的封装无法使用采购的元器件。如果是PCB封装设计错误,生产出来的板子无法使用也没有办法补救。

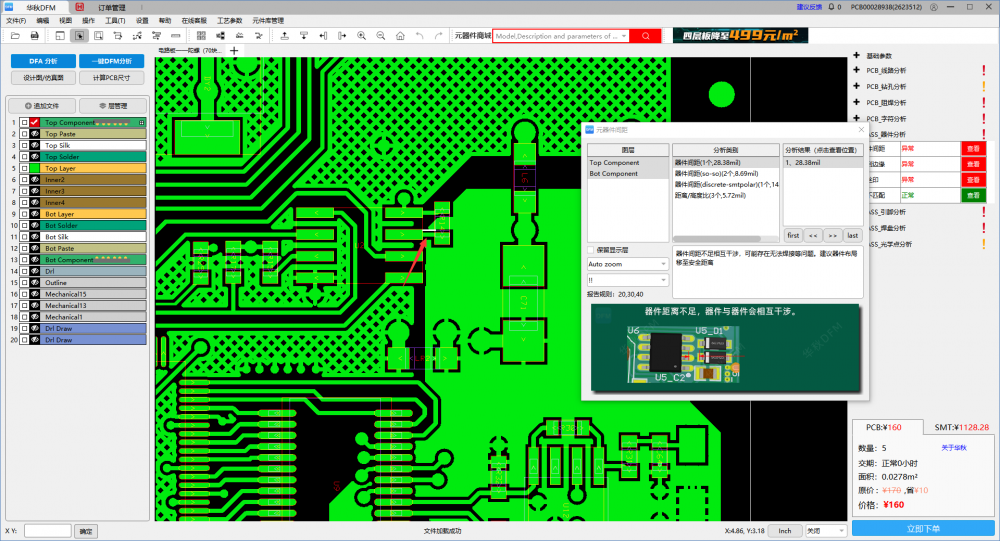

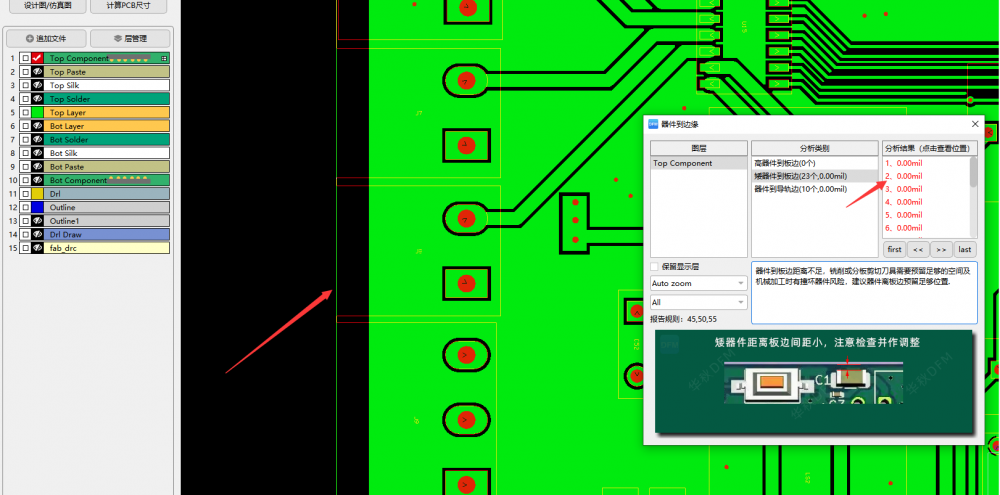

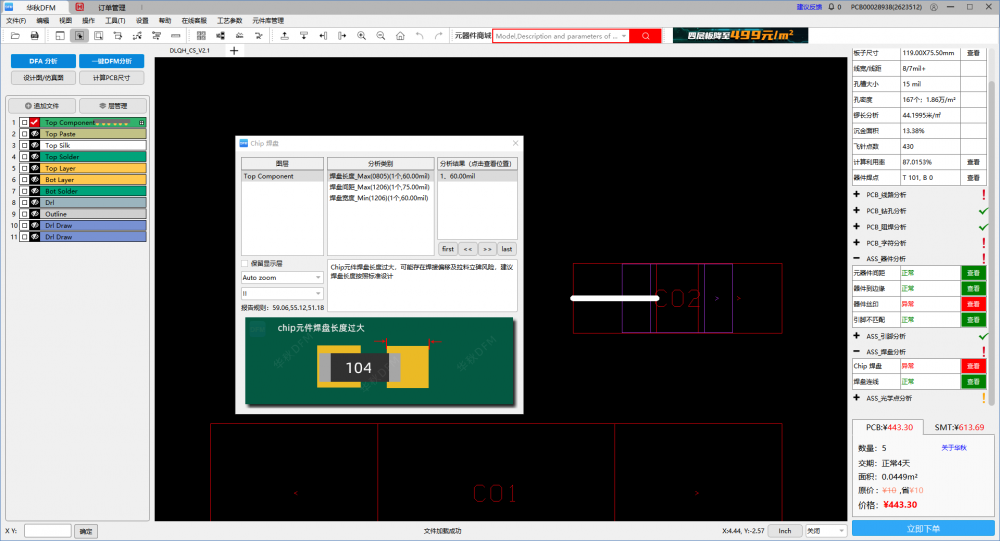

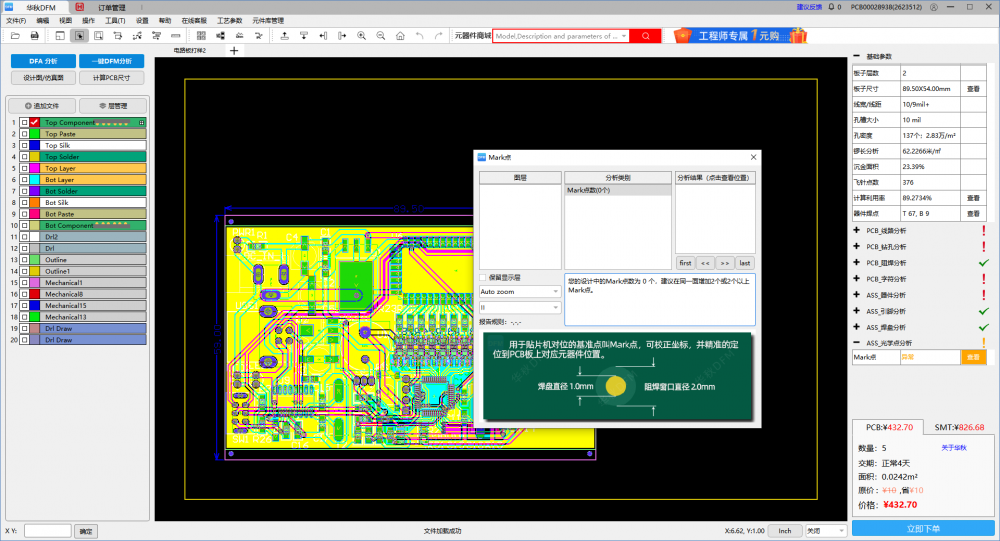

(二) 器件间距,PCB布局时没有考虑是否能够组装,生产出来的板子组装时器件距离不足,则会导致生产困难,或者无法组装。器件的间距不足即便是能组装,以后也不方便返修。PCB布局时需考虑器件与器件的间距。 器件到板边,元器件到板边的安全距离不够,在组装过贴片机器时会撞坏板边的器件,拼版生产的板子在过V-CUT机器时会导致板边的器件焊盘被割小,组装时器件无法贴片。因此PCB设计时需留足器件到板边的安全距离。 CHIP焊盘过长,PCB的元器件焊盘设计是一个重点,最终产品的质量都在于焊点的质量。因此,焊盘设计是否科学合理,至关重要。当CHIP焊盘设计过长或焊盘大小不一致时,焊接器件可能会拉偏,或者导致器件立碑。 无mark点,线路板做好后,需要贴装元器件,现在元器件的贴装都是通过机器来完成的(SMT)。SMT中会用到mark点,mark点用于自动贴片机上的位置识别点。无mark点则导致贴片不方便。

组装分析功能介绍

01器件分析

元器件间距:器件间距不足相互干涉,可能存在器件焊接困难或无法返修。器件与器件的高比,超出一定范围存在热风波不均,可能存在焊接不良,焊接后无法返修。

器件到边缘:器件到板边距离不足,铣削或分板剪切刀具需要预留足够的空间及机械加工时有撞坏器件风险。器件到导轨距离不足,SMT加工时可能存设备导轨撞飞器件无法焊接的风险。

元器件丝印:器件接触字符,可能存在字符被器件遮挡,给焊接、返修等造成不便。字符离器件太远,无法识别对应元件位号,可能存在焊接贴错元器件风险。

02引脚分析

引脚数差异:贴片器件引脚数不一致,会导致无法焊接,需确认型号或封装是否用错封装。插件器件引脚数不一致,会导致无法焊接,需确认是否用错封装。

位号长度:位号字节数长度,≥5位数部分设备识别不到较长的位号。

贴片引脚:脚趾到焊盘边缘的距离不足,可能存在上锡量不足虚焊或焊接不牢的风险。器件引脚到盘宽度边缘距离不足,可能存在上锡量不足虚焊或焊接不牢的风险。

通孔引脚:插件引脚孔为NPTH属性,器件引脚存在焊接不良及非单层板电气无法导通风险。THT引脚无通孔,无法插件焊接。卧式安装的轴向器件Pitch比本体小,器件无法放入。

按压引脚:通孔与压接引脚的直径比过小,无法插件压接。通孔与压接引脚的直径比过大,可能存在元件松动不易焊接。

03焊盘分析

Chip 焊盘:chip元件焊盘内间距过小,可能存在焊接连锡短路。chip元件焊盘内间距过大,可能存在接触面小焊接不上的风险。

chip元件焊盘长度不足,可能存在焊接面小上锡量不足。chip元件焊盘长度过大,可能存在焊接偏移及拉料立碑风险。

焊盘连线:封装的焊盘大部分都是有电气网络连接,如焊盘无线相连,则有可能存在设计失误的开路。

Mark点数:mark点是电路板设计中PCB应用于自动贴片机上的位置识别点。mark点的选用直接影响到自动贴片机的贴片效率。

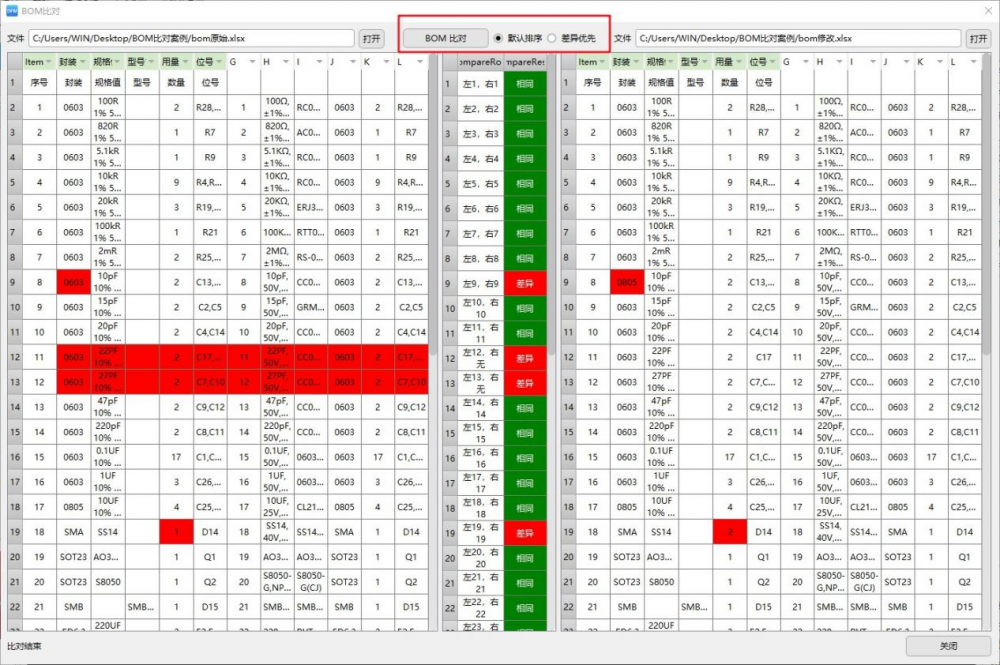

BOM分析配单

BOM表检查:(一)

核对bom文档修改的前后差异。帮助用户检测BOM表的正确性。

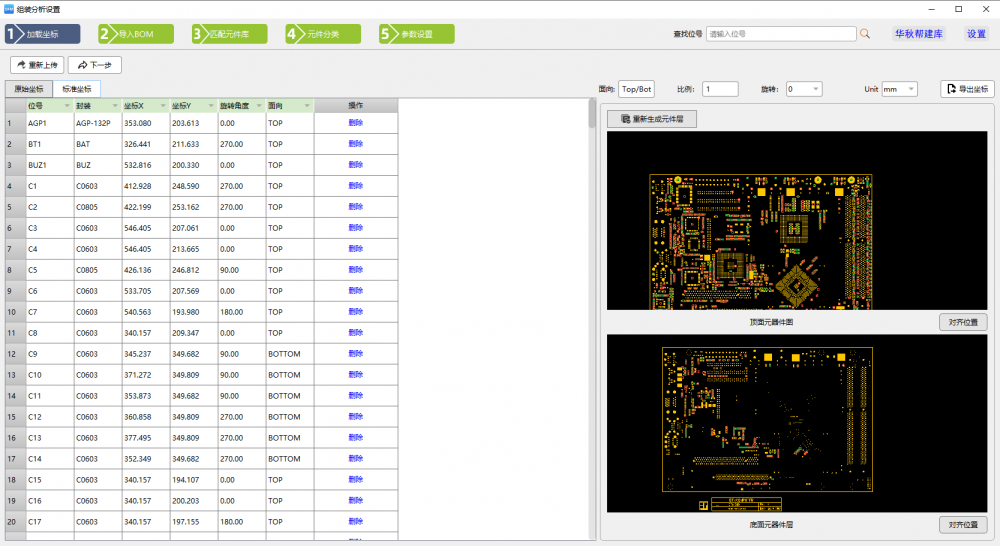

坐标整理:(二)Gerber文件无坐标,首先需加载坐标文件才能识别器件焊接的位置,当坐标文件有异常不规范时,整理坐标帮助用户能使用正确的坐标贴元器件。

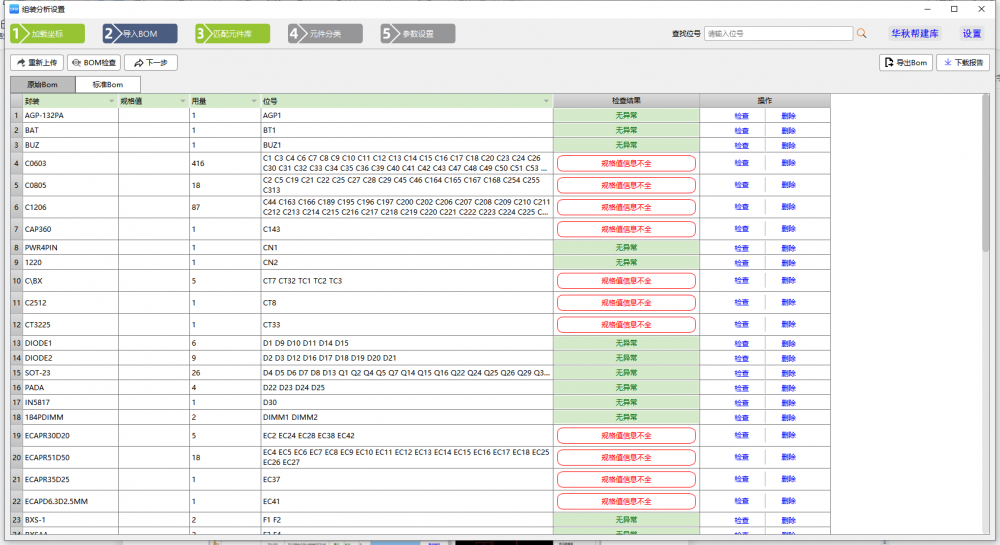

BOM整理:(三)

当BOM表里面的数据不正确或表头错误,通过整理BOM把错误的数据提示出来,修改成正确的BOM数据进行元器件配单。

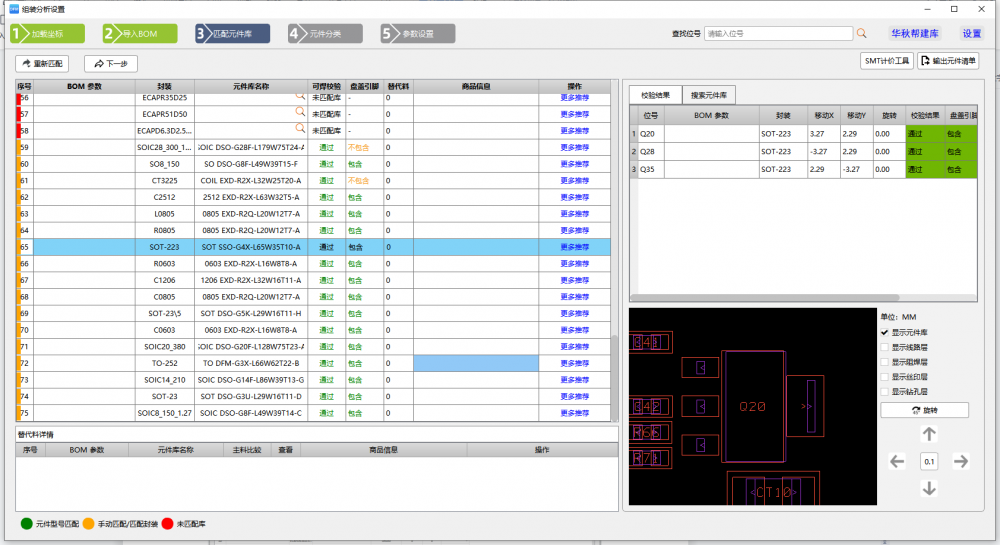

匹配元件库:(四)

根据华秋所建的元件库匹配BOM数据,当匹配不通过时可进行调整,选择其他器件或调整元件库,当未匹配库则是无对应的元件库,可向华秋提建库需求。

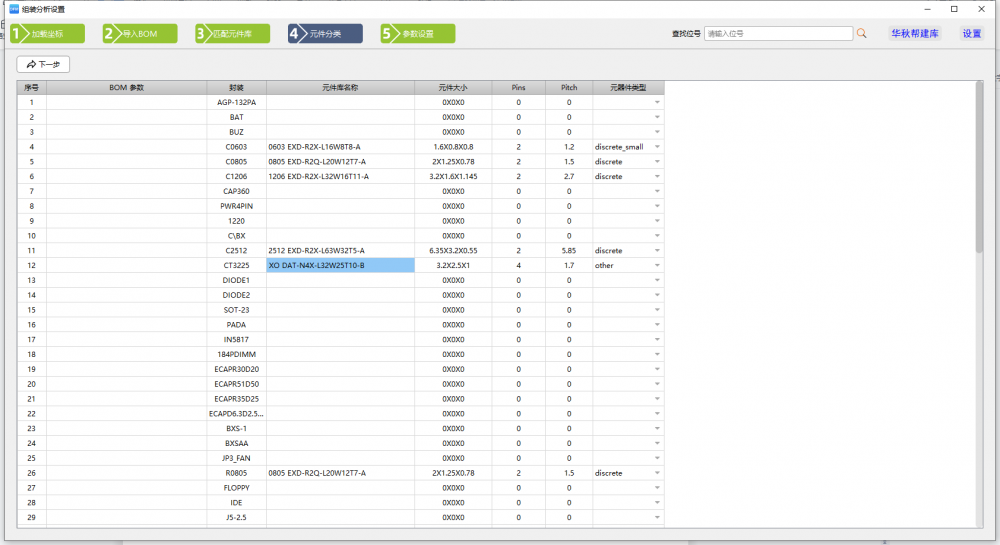

元件分类:(五)

已匹配元件库的器件封装对应一个属性,并储存类型。下次同样数据时可直接按此类型分配,如改物料封装对应的类型被修改,储存以最后一次为准。

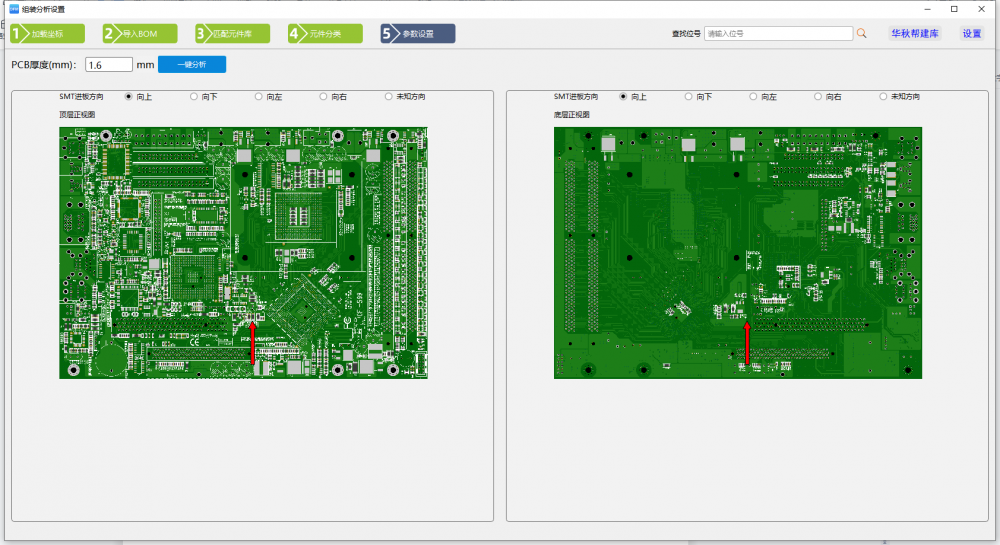

参数设置:(六)

标识SMT贴片的进板方向,自动贴片机需注意进板方向,如高器件在前面会挡住小器件上锡,导致焊接不良。

我要赚赏金

我要赚赏金