我们都知道,一般的IC元器件通常只有两个电源引脚,一个是Vcc或Vdd,另一个是Gnd或Vss。但是,现在的MCU通常却有多组电源引脚,这是什么原因呢?

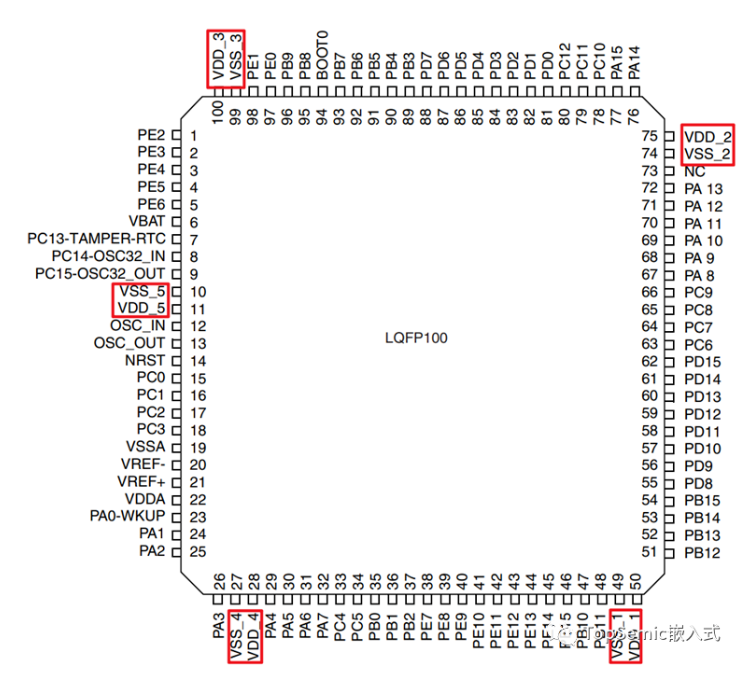

以某款100脚MCU为例,如下图所示,我们可以看到它有5组VDD/VSS,并且会要求每一组VDD/VSS都要接上。实际上,这多组VDD内部是互相连接在一起的,既然这样,那么芯片厂家为什么不只留一组出来呢?或者说虽然留了多组出来,能不能外面只接一组呢?如果能这样既节约引脚,外面连接走线也更少。

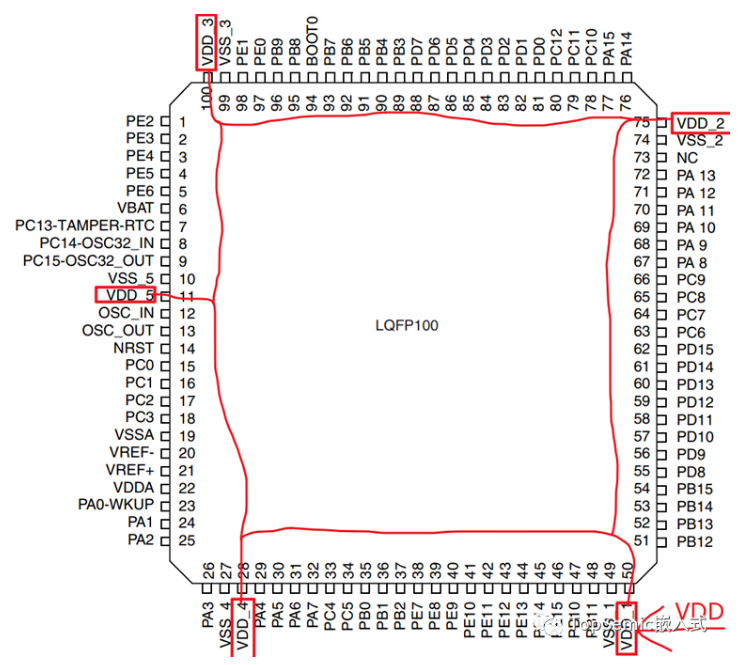

如果外面只接一组VDD的话,电流在芯片内部经过的路径相对较长,如下图红色的线条。

对于频率高的电路,VDD电流会在高频突变(因为频率越高,需要的电流越大),这时候路径上产生的感抗会阻碍电流的变化。路径越长,感抗越大,从而对电流的阻碍作用就会更明显,进而导致芯片网络中的电压变化,这样就会影响MCU系统的正常工作。

对于低频或者直流电路,路径长其影响不大。所以,早期的低频MCU只有一个VDD,而多组VDD可以减少电感效应(电感并联总电感变小,路径变短电感也越小)。

可以把上述芯片供电的过程,想象成给一块田地灌溉的过程,如果只有一个进水口,肯定不如多个进水口一起进水好。

除此之外,再补充几点:

1)MCU的模拟外设比如ADC通常是独立的电源VDDA,这是因为ADC需要尽可能干净的电源以保证转换结果的准确性,独立一路可以避免受到其他电源噪声的干扰。

2)多种电压要求。有时,芯片的不同部分会以不同的电压运行。一个典型的例子是低压内核和高压 I/O。内核使用较低的电压来降低功耗而 I/O 以更高的电压运行,以便更好地与外部电路连接。这时也需要分出来多组供电,常见的是复杂的SOC芯片。

3)多组VDD相比单个VDD,一个VDD引脚上经过的电流会减小,这样引脚不必承受过高的电流,增强可靠性。

我要赚赏金

我要赚赏金