想要引起EMC问题,需要有辐射源,耦合路径以及接收器。

电磁兼容性问题的潜在辐射源包括无线电****机、高频电路线,电力线等使用或者产生电磁场的物体;接收器,则包括无线电接收器、电子电路等几乎任何使用或者能够探测到电磁能量的设备。

而耦合路径,则包括传导和辐射。

所谓传导干扰,是指电子设备产生的干扰信号通过导线或公共电源线互相产生干扰,是低频干扰,频率最高到30MHz。

所谓辐射干扰,是指电子设备产生的干扰信号通过空间耦合干扰其他设备,是高频干扰。

辐射又分磁场耦合,电场耦合以及电磁场耦合。耦合路径通常是这些耦合方式的组合,而且衰减其中一条路径的同时,可能会使另一条耦合路径增强。

每个EMC问题,对存在辐射源、耦合路径以及接收端。解决EMC问题,就是找出这些因素,针对这些因素做出改进。

这些改进措施,笼统地讲,包括:

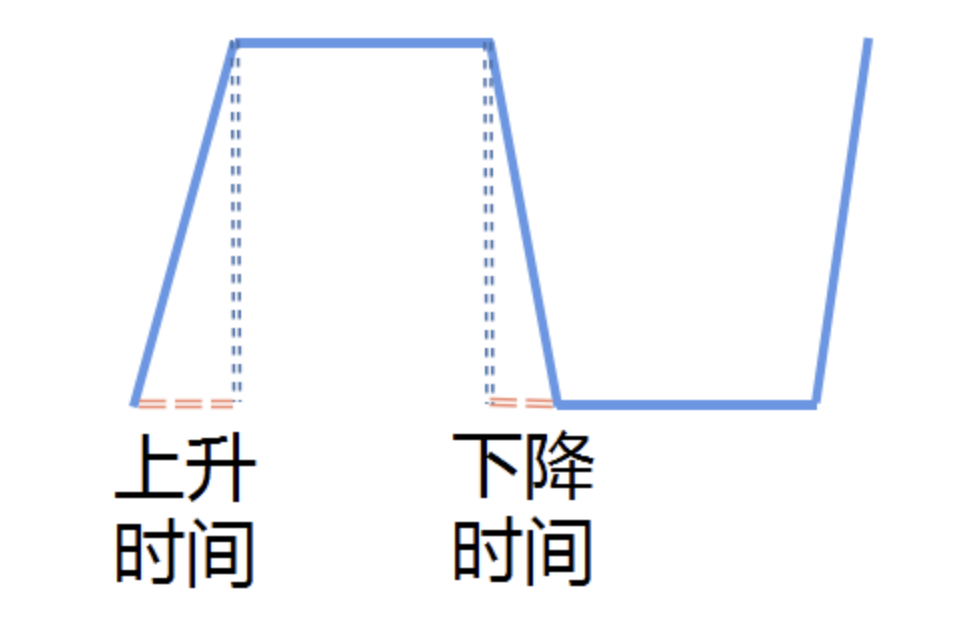

1 降低源端的干扰信号

比如说,数字信号的上升/下降时间越短,其所包含的高频频谱越多;一般来说,频率越高,越容易耦合到接收端。如果我们想降低数字信号所引起的干扰的话,可以拉长数字信号的上升/下降时间。但前提是,需要保证接收该数字信号的器件的正常工作。

2 切断耦合路径

比如说,在接收器外面罩上屏蔽罩,则是切断耦合路径的一种方法。但是这种方法,有时候成本高,而且并不能达到理想的性能。

3 降低接收端对干扰的敏感度

这个往往比较难,因为降低对干扰的敏感度的同时,可能会影响其对有用信号的接收。

很多时候,产品最后调着调着,就卡在EMC上了,比如我现在所处的状态。现在在看我的PCB布局,就觉得当时有些线考虑不周。

PCB的不良布局,是EMC的一个主要来源。

在对PCB进行布局时,我们需要从以下四个方面做一个预判:

1 电路中有哪些辐射源

电路中比较常见的辐射源包括:时钟,数字信号,DC-DC转换,直流电源线以及低速线。

时钟:周期变化,会产生谐波;

数字信号:虽然不是周期变化,但是也会产生比较大的噪声;

直流电源线以及低速线:虽然这些线本来的目的,是走电源或者低速信号。但是可能会有高速信号反串到这些线中,造成干扰。所以,如果一个IC内部有高速电路,那做PCB设计时,把与其连接的每根线都当成高速信号线小心对待。

2 电路中关键的回流路径

首先,需要知道,电流是一个环路,有多少过去,就有多少回来。

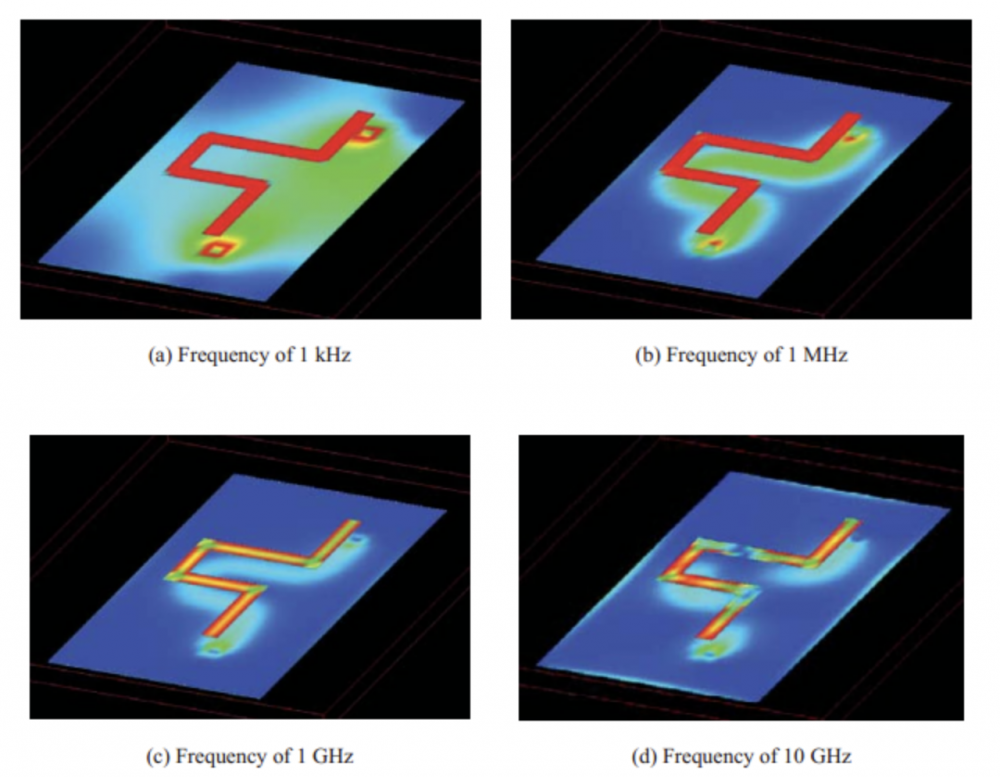

再者,电流是追寻最小阻抗,Z=R+jwL。所以当频率低的时候,是找电阻最小的路径;而频率高的时候,则是找电感最小的路径。从下图中,可以看到,当频率为1KHz时,回流路径则选择两点最短的路径;当频率〉1MHz时,回流路径则选择最小感抗的路径。

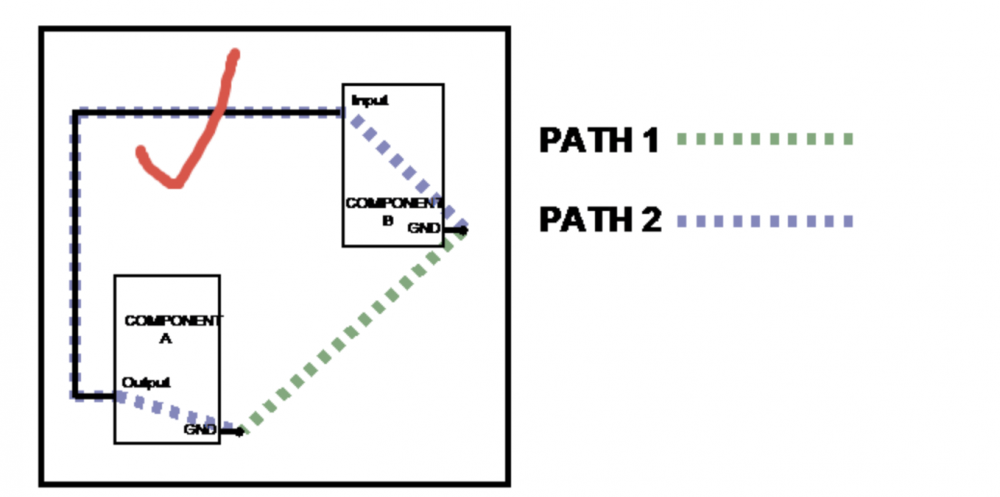

所以,假设有两个器件,从器件A有一50MHz的信号到器件B,则其回流路径则为PATH2,而非PATH1。回流从器件B的GND管脚流出,经过50MHz高速线的下方,回到器件A的GND管脚。

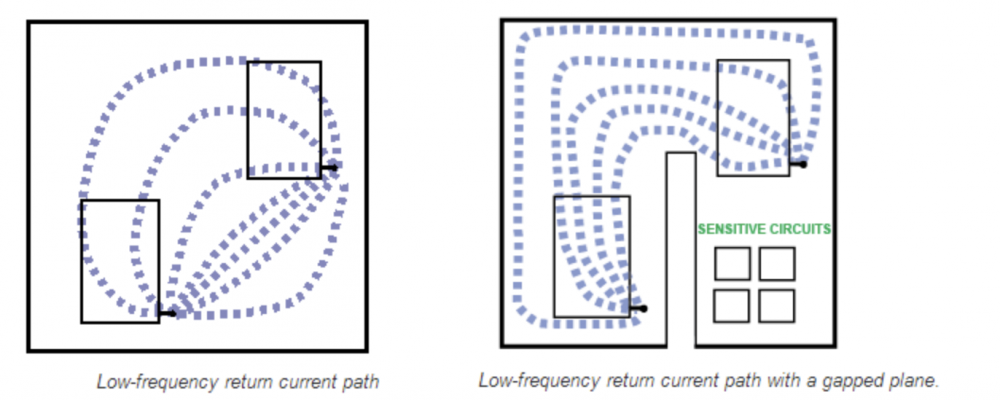

如果信号频率在KHz以下,那么回流会散到大部分的电路板上,因为要沿着最小电阻走嘛,散的开,截面积就大,电阻就小。如果板上有敏感的模拟信号,可能会有问题。这个时候,可以在地上割个缝隙,如下图所示。

3 板子上是否有天线形成

有时候画板子的时候,不小心就形成一个天线。

PCB板上不小心形成的天线,一般都满足下面三个条件:

天线包含两个部分

两个部分都不是电小尺寸(就是说,天线的尺寸要和波长能够在同一数量级)

两个部分之间存在感应电压

对于小于100MHz的低频信号,对应波长为3m;一般的PCB板,都远小于这个值。所以,在这个频率以下,一般会发生天线效应的,可能就是电缆或者金属机壳了。只要避免电缆之间产生电压,则会减小发生天线效应的可能性。这可以通过将接插件放置在PCB板的同一侧实现。

在PCB中,像散热器,电源层,高器件等都可能具有天线效应,因为其一部分是PCB上的金属平面,而另外一部分,这远离该金属平面。

4 找一下可能的耦合路径

耦合路径有传导,电场耦合,磁场耦合和电磁场耦合。

我要赚赏金

我要赚赏金