本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用。话不多说,上货。

IP CORE 之 ROM设计

本篇实现基于叁芯智能科技的SANXIN -B01 FPGA开发板,以下为配套的教程,如有入手开发板,可以登录官方淘宝店购买,还有配套的学习视频。

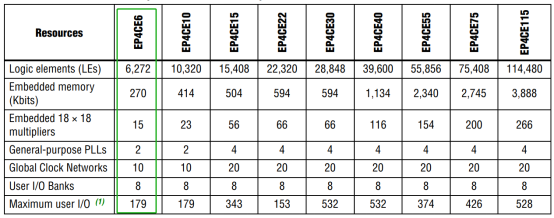

CYCLONE IV系列器件采用嵌入式内存结构,用以满足设计时需要芯片上内存的需求。嵌入式内存结构由M9K内存块组成,在FPGA中按照列状排列。设计者可以配置这些内存块成为各种内存功能,如:RAM、移位寄存器、ROM和FIFO缓冲区等。

SANXIN-B01的FPGA为EP4CE6E22C8, 此款FPGA共包含270K bit的内存。

M9K的内存块支持以下特性:

片内的M9K内存块是由RAM构成,掉电丢失。

· 设计要求

在FPGA内部构建深度为256,宽度为8的ROM。在不同的地址中放入与地址值大小相等的数据,即:0地址放0,1地址放1······

· 设计原理

ROM(read only memory)只读存储器,此种存储器不支持写操作,只支持读操作。在存储器建造时,将数据刻录进去。ROM能够实现掉电不丢失。

本次设计ROM是利用FPGA片内嵌入的M9K构成的,所以不能够实现掉电不丢失。

由于设计ROM深度为256,故而地址的宽度为8位。

本次构建为ROM,所以在构建ROM之前应当首先设计好初始化文件(mif文件)。

ROM工作原理为,在时钟上升沿采样到rden为1时,将addr所指示的存储空间的数据进行输出。

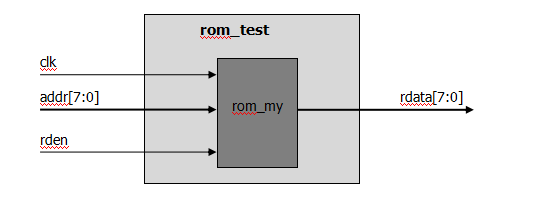

· 设计架构和信号说明

本模块命名为rom_test。

建立工程后,在qprj文件中,建立ipcore文件夹,在ipcore文件夹中建立rom_my文件夹。

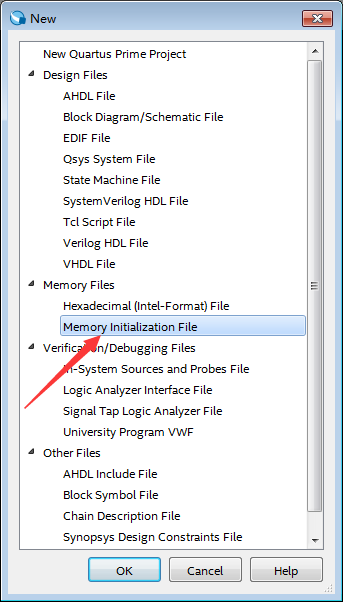

新建mif文件。

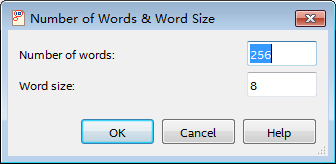

点击OK,输入深度256,宽度为8。

点击OK。然后将点击另存为,将文件保存至qprj -> ipcore -> rom_my -> rom_my.mif。

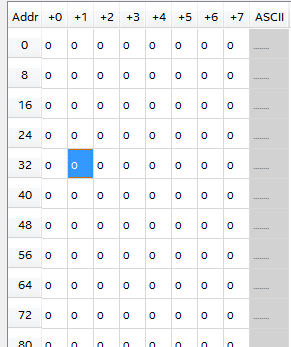

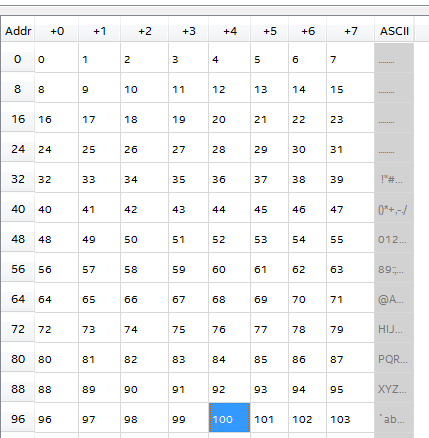

这里的每一个小方格都是一个存储空间。排列方式按照基地址加偏移地址的方式分布。例如:图中选中的蓝色方格的地址为32+1。

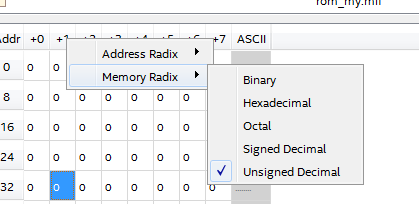

在基地址或者偏移地址上,右击可以更改地址的进制和存储空间存储数据的进制。

将地址和数据的进制都设置为无符号位十进制。选中一个单元,可以直接进行数据的输入。由于存储单元有256个,每个存储单元都进行手动更改的话,确实比较累人。

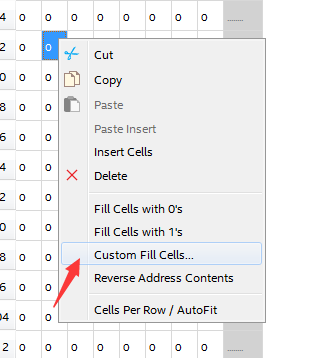

在存储单元格上右击。选择custom fill cells···

这个工具是quartus 软件为方便用户有规律填充存储单元的快捷工具。

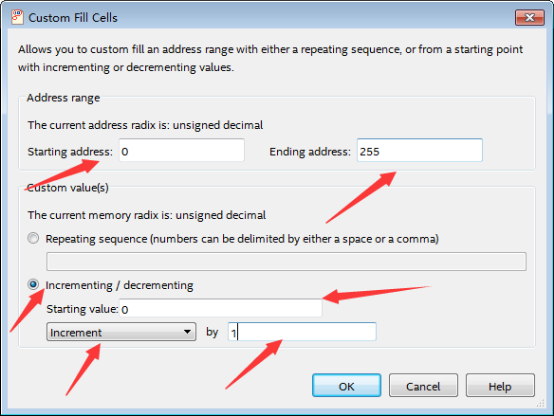

初始地址填写为0,结束地址填写为255。

选择递增或者递减,初值填写为0,选择递增,步进为1。

点击Ok后,就可以看到,每个地址里面都会填写如与地址值大小相等的值。

点击保存,mif文件就已经制作完成。

· 调用ip core之 rom

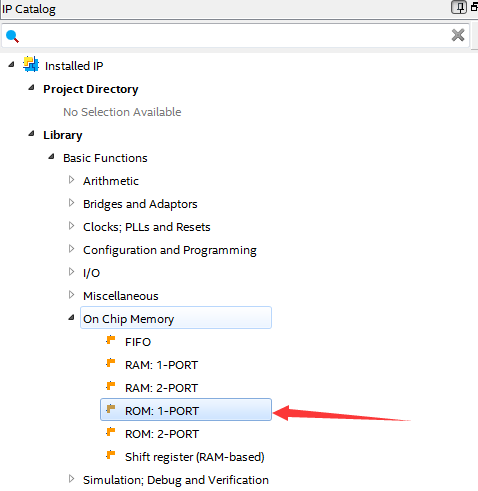

选择tools -> ip catalog。

ROM分为单端口(1-port)和双端口(2-port)。ROM是一个只读存储器,通过给予地址和读使能,就可以得出对应的地址的数据。在FPGA中,ROM可是配置两套端口,这两套端口相同,都可以通过给予地址和读使能,得出对应的地址的数据,并且相互独立,但是共用同一段存储空间。

在此选择ROM :1-port。

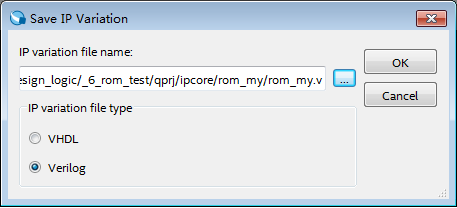

选择verilog,路径为qprj -> ipcore -> rom_my,名字为rom_my。然后点击ok。

选择深度为256,宽度为8。

选择时钟方式为单时钟。点击Next。

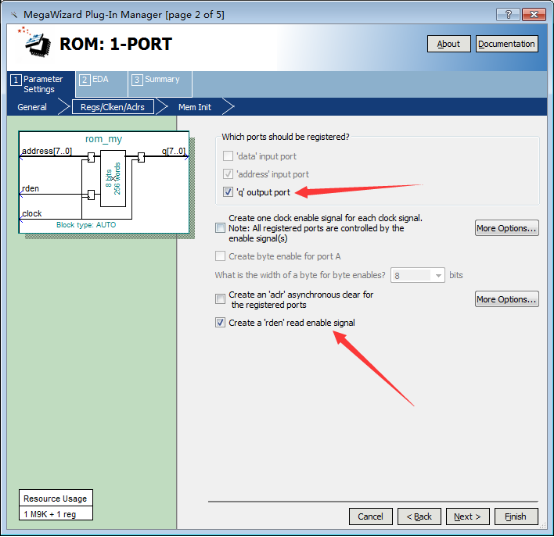

选择 q out registered(即经过寄存后,输出q)。

选择读使能。若不选择读使能,则读使能一直为被使能。点击Next。

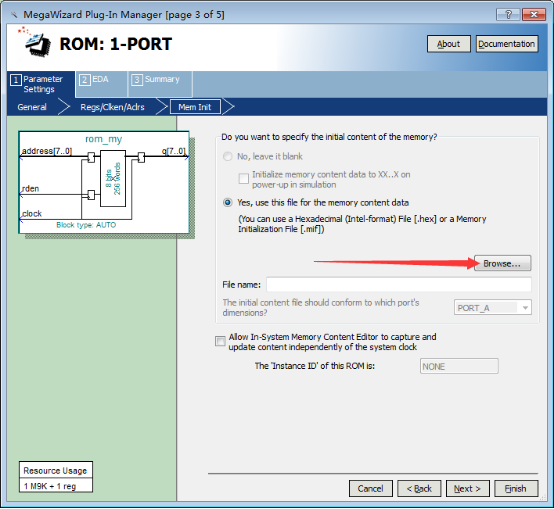

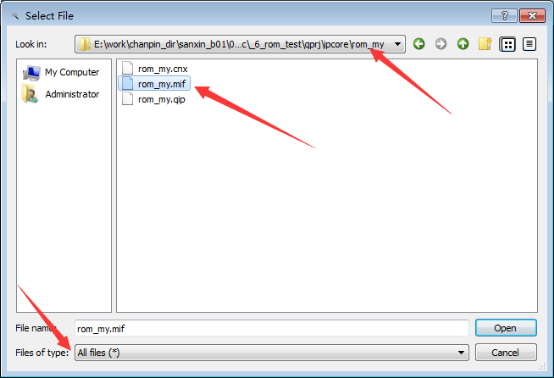

选择browse···,找到qprj -> ipcore -> rom_my -> rom_my.mif。

在此文件中,找不到该mif文件。因为寻找文件的类型不对,将type of file 修改为 all files。

找到mif,点击open。

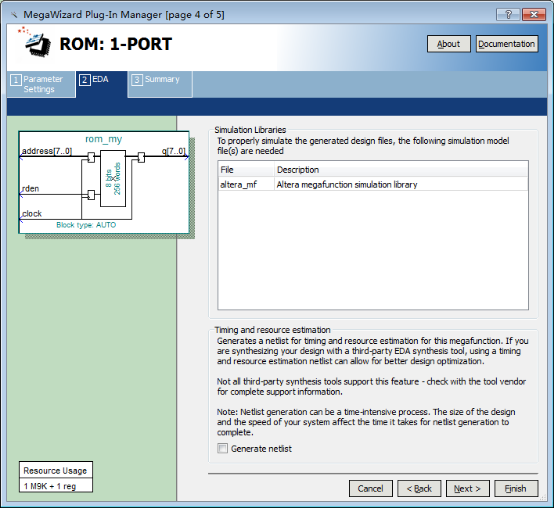

点击Next。

点击Next。

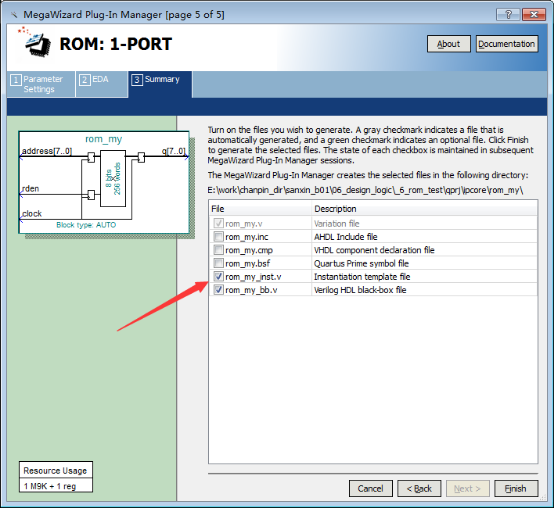

选择上rom_my_inst,点击finish。

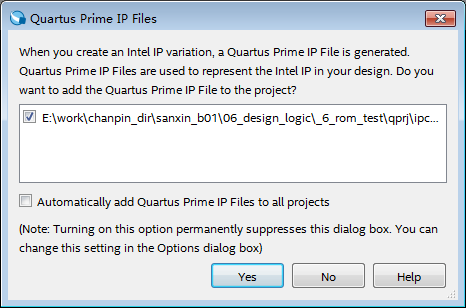

把这个ip core添加进工程,点击Yes。

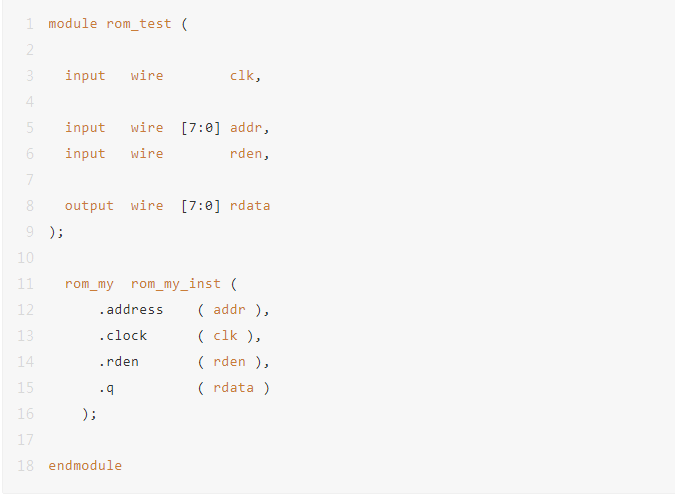

· 编写设计顶层

顶层模块负责例化rom_my。rom_my的例化代码在ipcore -> rom_my -> rom_my_inst.v中。

设计代码为:

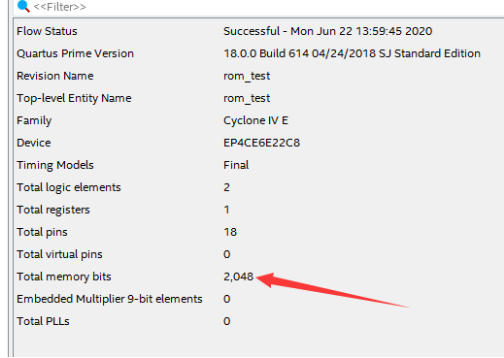

分析综合后,使用2048bit的存储器。报告如下:

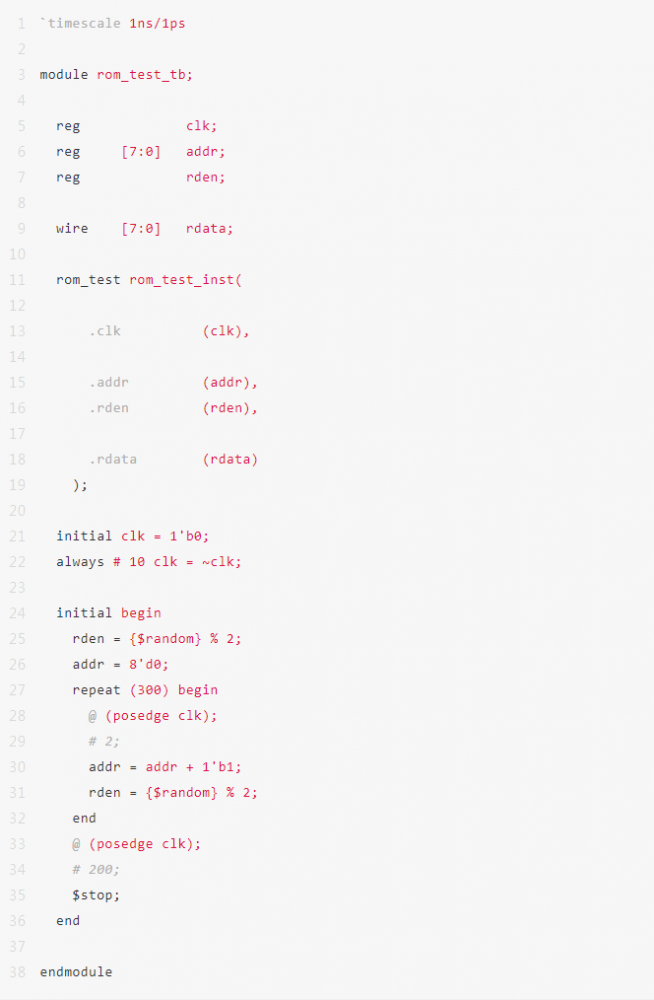

设计仿真文件时,将所有的地址轮询一遍,查看输出的数据是否正确,rden信号设置为随机值,在不同的地址随机决定是否读出。

仿真代码为:

repeat语句为重复语句,相当于把begin end中间的语句重复执行N次。

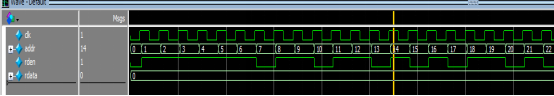

设置testbench后,进行RTL仿真。

从波形图中可以看出,无论地址为多少,rden是否为1,rdata始终为0。

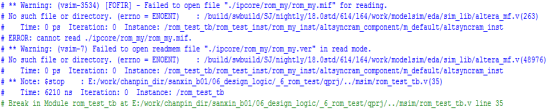

打开modelsim的transcript窗口,就可以发现原因。

modelsim的软件打不开(找不到)初始化的mif文件。

出现此种错误的原因为,modelsim和quartus的有很多文件在进行关联是都是使用相对路径,为的是方便工程的移植。而在仿真时,两个modelsim软件认为的基本路径和quartus软件认为的基本路径不相同,所以导致出此错误。此时,笔者建议大家直接打开ipcore -> rom_my -> rom_my.v,进行修改初始化文件,将相对路径直接修改为绝对路径。

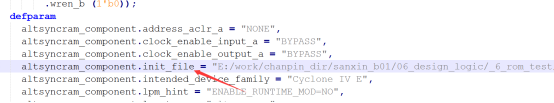

将altsyncram.component.init_file=“”,双引号中的文件前面的路径修改从盘符开始的路径。切记:路径的下一级标识为“/”。

修改后,此工程在已经移植时,就会报错。因为此路径已经不合法,所以在进行移植时,请对应修改此路径。

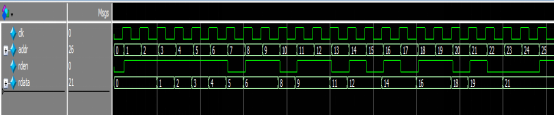

保存过后,重新进行分析综合。然后再次打开modelsim,就可以看到正确的波形了。

在波形中可以看到,当rden为高时,rdata能够延迟两拍后,输出对应的数据(当地址为1、2、3时)。当rden为低时,rdata保持上一个值不变(当地址为7时)。其他地址设计者可以自动对应。

将ROM设置为双端口时,addr、rden和rdata会多出一套,操作时序和方法是相同的。

我要赚赏金

我要赚赏金