RISC-V中断优先级

这些机器级的中断寄存器处理了一些根中断源,为了简单起见,这些中断被分配了固定的中断复位优先级。外部中断控制器可以基于中断组,实现复杂的中断优先级方案,混合这些中断源之后输入到 CPU 中。

多个中断在 M 模式下同时产生时,会按照以下顺序递减优先级:MEI, MSI, MTI, SEI, SSI, STI。

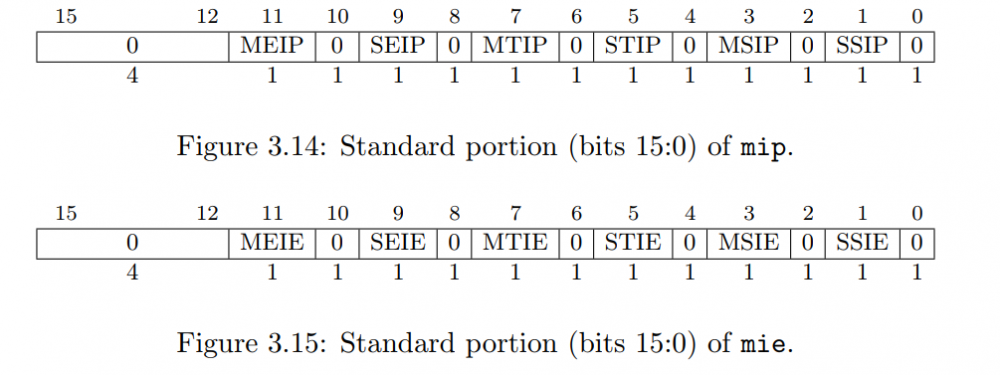

下图是 6 种中断的中断标志寄存器 mip 和中断使能寄存器 mie。 各个位代表的中断如下表所示:

各个位代表的中断如下表所示:

寄存器位 含义

MEI 机器模式外部中断

SEI 监管者模式外部中断

MTI 机器模式定时器中断

STI 监管者模式定时器中断

MSI 机器模式软中断

SSI 监管者模式软中断

高级别的特权模式中断 一定比 低级别特权模式中断 优先级高。

mip 和 mie 寄存器 15:0 是标准的寄存器中断,在 16 位及以上的平台特定的机器级中断源具有平台特定的优先级,但是通常选择最高的服务优先级来支持非常快的本地中断向量。

外部中断在内部(定时器/软件)中断之前处理,因为产生的外部中断的设备,通常需要较少的中断服务次数。

软件中断在内部定时器中断之前处理,因为内部定时器中断通常用于时间片,其中时间精度不太重要,而软件中断用于处理器间消息传递。当需要高精度定时器时,可以避免软中断,或者将高精度定时器的中断路由到其他路径上,来保证高精度定时器的准确。软件中断位于 mip 的最低四位,因为这些位经常被软件写入,并且该位置允许使用单个五位立即数的 CSR 指令进行读写。

以上是在寄存器级别的分析。

共3条

1/1 1 跳转至页

RISC-V中断优先级

关键词: RISC-V 中断 优先级

共3条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |