一件器材的输出阻抗和所连接的负载阻抗之间所应满足的某种关系,以免接上负载后对器材本身的工作状态产生明显的影响。什么是阻抗 在电学中,常把对电路中电流所起的阻碍作用叫做阻抗。阻抗单位为欧姆,常用Z表示,是一个复数:Z= R+i( ωL–1/(ωC)) 具体说来阻抗可分为两个部分,电阻(实部)和电抗(虚部)。 其中电抗又包括容抗和感抗,由电容引起的电流阻碍称为容抗,由电感引起的电流阻碍称为感抗。阻抗匹配的理想模型 信号源与传输线之间匹配,分为两种情况:

- 使信号源无反射,方法是接入信号源与传输线之间接入匹配装置

- 信号源共轭匹配,方法是信号源与被匹配电路之间接入匹配装置,这种情况下多属于有源电路设计

射频工程师大都遇到过匹配阻抗的问题,通俗的讲,阻抗匹配的目的是确保能实现信号或能量从“信号源”到“负载”的有效传送。

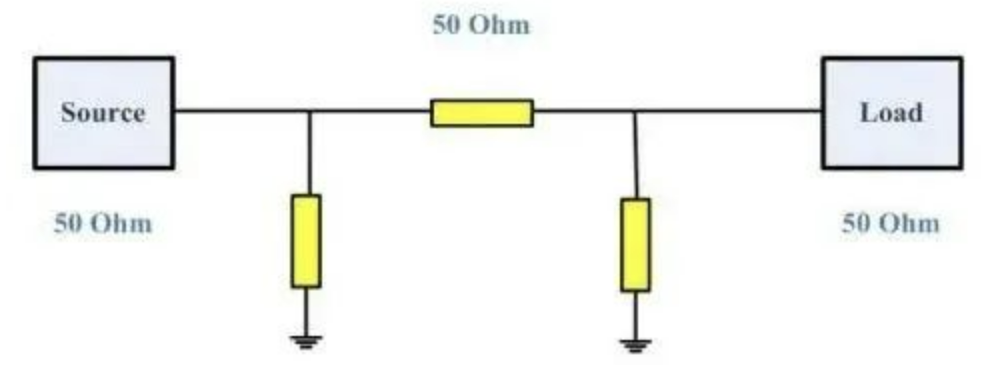

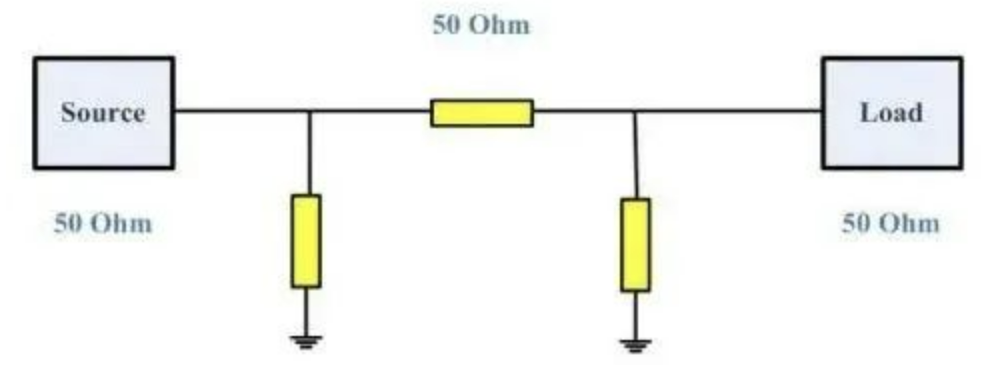

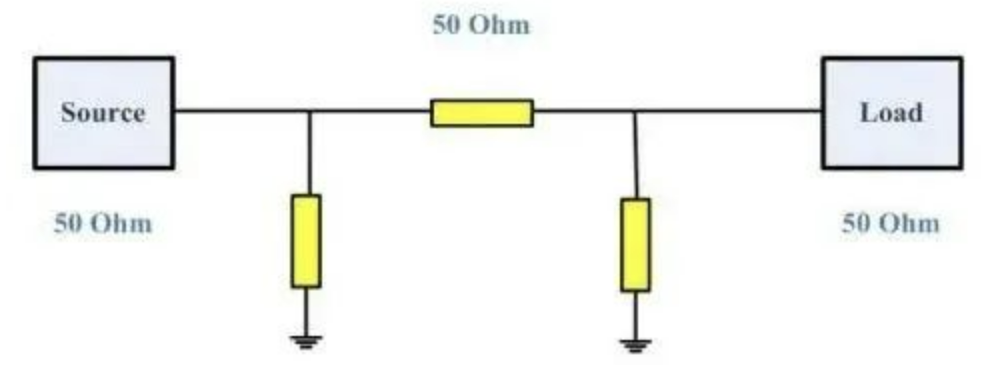

如下图所示,其最最理想模型当然是希望信号源Source端的输出阻抗为50欧姆,传输线的阻抗为50欧姆,负载Load端的输入阻抗也是50欧姆,一路50欧姆下去,这是最理想的模型。

然而实际情况是:源端阻抗不会是50ohm,负载端阻抗也不会是50ohm,这个时候就需要若干个阻抗匹配电路。 而匹配电路就是由电感和电容所构成,这个时候我们就需要使用电容和电感来进行阻抗匹配电路调试,以达到RF性能最优。阻抗匹配的方法 阻抗匹配的方法主要有两个,一是改变阻抗力,二是调整传输线。 改变阻抗力就是通过电容、电感与负载的串并联调整负载阻抗值,以达到源和负载阻抗匹配。 调整传输线是加长源和负载间的距离,配合电容和电感把阻抗力调整为零。 此时信号不会发生****,能量都能被负载吸收。 高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆。一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为85-100欧姆。 阻抗匹配(Impedance matching)其实是微波电子学里的一部分,主要用于传输线上,是为了达到所有高频微波信号都能传至负载点的目的,不会有信号反射回源点。 大体上,阻抗匹配有两种:

- 一种是通过改变阻抗力(lumped-circuit matching)

- 调整传输线(transmission line matching)

要匹配一组线路,首先把负载点的阻抗值除以传输线的特性阻抗值来归一化,然后把数值划在史密夫图表上。改变阻抗力 把电容或电感与负载串联起来,即可增加或减少负载的阻抗值,在图表上的点会沿著代表实数电阻的圆圈走动。如果把电容或电感接地,首先图表上的点会以图中心旋转180度,然后才沿电阻圈走动,再沿中心旋转180度。重复以上方法直至电阻值变成1,即可直接把阻抗力变为零完成匹配。调整传输线 由负载点至来源点加长传输线,在图表上的圆点会沿著图中心以逆时针方向走动,直至走到电阻值为1的圆圈上,即可加电容或电感把阻抗力调整为零,完成匹配。 阻抗匹配则传输功率大,对于一个电源来讲,当它的内阻等于负载时,输出功率最大,此时阻抗匹配。最大功率传输定理,如果是高频的话,就是无反射波。对于普通的宽频放大器,输出阻抗50Ω,功率传输电路中需要考虑阻抗匹配,可是如果信号波长远远大于电缆长度,即缆长可以忽略的话,就无须考虑阻抗匹配了。阻抗匹配是指在能量传输时,要求负载阻抗要和传输线的特征阻抗相等,此时的传输不会产生反射,这表明所有能量都被负载吸收了。反之则在传输中有能量损失。高速PCB布线时,为了防止信号的反射,要求是线路的阻抗为50欧姆。这是个大约的数字,一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线则为 100欧姆,只是取个整而已,为了匹配方便。

我要赚赏金打赏帖

我要赚赏金打赏帖