1、MAC速率逐级扩展

1、MAC速率逐级扩展 从MAC发送侧到SERDES发送侧入口,会导致数据量增加的模块有64B/66B编码,FEC RS编码,AM码插入,其中AM码插入是在数据中额外插入一些对齐标识,插入的AM码会把数据往后挤,并不会改变速率。因此,导致速率增加的因素只有64B/66B编码和FEC的RS编码。

从MAC发送侧到SERDES发送侧入口,会导致数据量增加的模块有64B/66B编码,FEC RS编码,AM码插入,其中AM码插入是在数据中额外插入一些对齐标识,插入的AM码会把数据往后挤,并不会改变速率。因此,导致速率增加的因素只有64B/66B编码和FEC的RS编码。

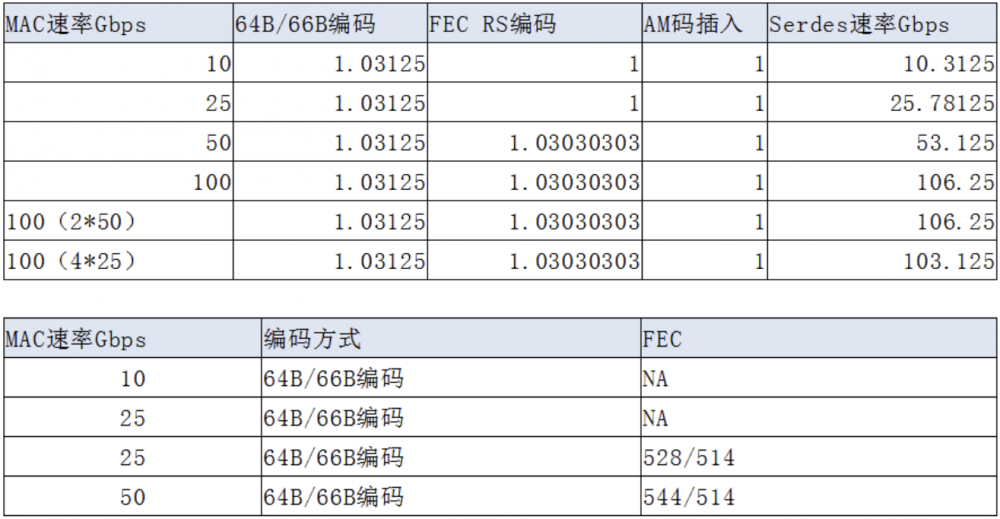

64B/66B编码会将64bit数据编码成66bit,速率扩展比例为66/64=1.03125。

FEC RS编码根据编码类型不同扩展比例不一致,RS(528,514)编码没有速率增加,因此25G no-fec模式和fec模式在serdes速率是一样的,都是25.78125Gbps。而RS(544,514)编码速率增加比例为544/528=1.03030303,因此50G的MAC速率在serdes上是50*1.03125*1.03030303*1=53.125。

2、同一个MAC速率可以具有不同的serdes速率

以100G速率为例,如果是2lane*50G模式传输,或者单lane 100G模式传输,serdes处的速率都是106.25G,如果以4lane*25G模式传输,serdes处的速率都是103.125。

我要赚赏金

我要赚赏金