MOSFET 寄生电容的影响

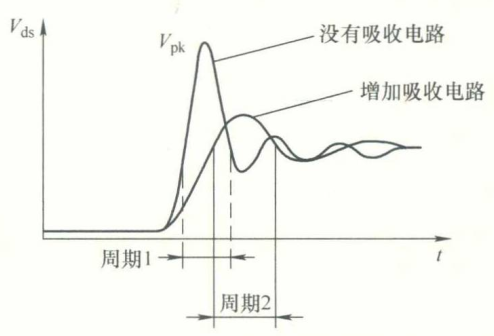

对比我们常用的平面MOSFET和Co0IMOS可知,标称同样是12A/650V的开关管,平面MOSFET的EMI是比较容易通过的,而CoolMOS的EMI相对来说不是特别容易通过,需要通过再次的整改之后才能顺利通过,也就是我们常说的结电容大小导致,这里所说的结电容通常指 MOSFET的输出电容 C.=C+C可以经常看到在MOSFET上并一个10~100pF的高压贴片电容来针对整改辐射超标部分。缓冲吸收网络的作用如图 所示.

缓冲吸收网络的作用:

MOSFET寄生电容是指MOSFET裸片结构中,由于结构中的各种器件和材料的非完美性,导致源、漏和栅与基板之间形成的电容。这种寄生电容对MOSFET的性能、速度和功耗等方面具有显著的影响。以下是MOSFET寄生电容的主要影响:

漏电流增加:寄生电容的存在会导致漏电流的增加,特别是在高频工作条件下。这会影响MOSFET的功耗和效率。

响应时间缩短:寄生电容会储存电荷,这可能导致MOSFET的响应时间缩短。虽然这在一定程度上可以提高器件的速度,但也可能导致信号延迟增加和输出波形失真等问题。

功耗增加:由于寄生电容会储存电荷并在切换过程中释放,这会导致MOSFET的功耗增加。特别是在高频应用中,这种功耗增加可能更加明显。

信号延迟增加:寄生电容的存在会导致信号在MOSFET中的传输延迟增加。这可能会影响电路的整体性能和稳定性。

输出波形失真:在高频应用中,寄生电容可能导致MOSFET的输出波形失真。这种失真可能会降低电路的性能和可靠性。

工作频率的选择:

对于单级PFC来说,满载工作情况下随着输人电压的升高,工作频率也随之升高,这里在第1章有具体的测试体现,一般我们选择比较常见的是最低输入电压和最大输出负载时刻的频率为50~130kHz。建议工作频率为60kHz左右,这样的好处是在第一个工作频率时刻,EMI已经是往下的趋势,2倍频率的时候为120kHz左右,3倍频率时候是180kHz,躲过150kHz的界限,剩下的由工作频率引起的干扰已经大幅度减小,这样传导就比较容易处理了。

选择的频率过低,在最低电压并且满足设定的最大磁通量的情况下,需要更多的圈数才能满足要求,需要比较大的磁心骨架才能满足基本的设计要求,较低频率的时候需要更大的 EMI滤波器才能压制相同能量带来的EMI问题,同时带来的后果是成本高、体积大,与现在市场追求的小型化和高集成度相悖。

选择的频率过高,则与上述相反,但由于大部分单级PFC的芯片内部有最高频率限制(基本在130kHz左右)的机制,对于高出限制频率的范围,全部通过芯片内部限制,如此会造成能量的亏损,芯片温升高,不利于电源整体的稳定性,频率过高也不利于EMI的处理。所以市场上基本上大多数的设计,最低工作频率一般在50~130kHz之间,但会避开75kHz这个频率,因为其2倍频为150kHz,而150kHz正处在传导限值的转换点。

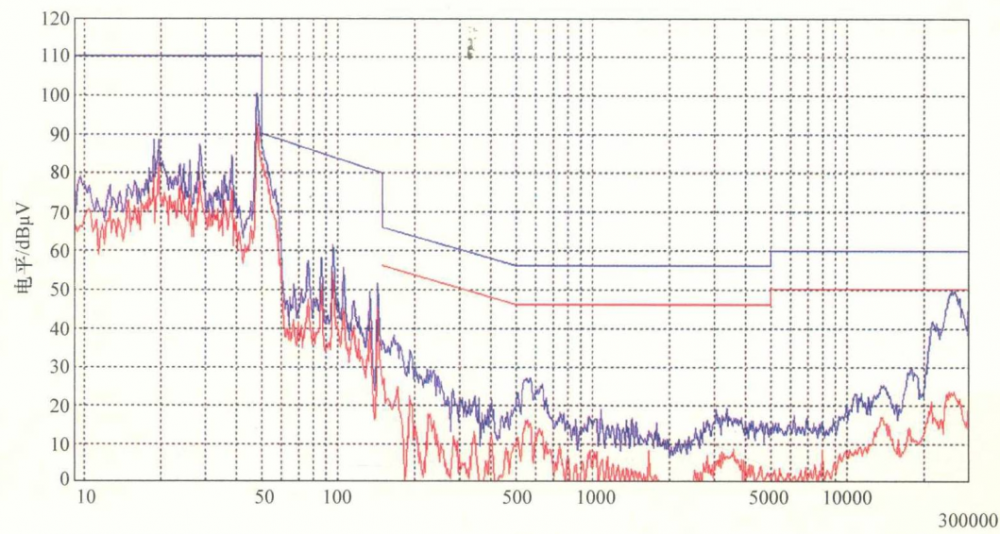

对于两级方案来说(OR-Boost加DC-DC),一般最低输人情况下频率设置范围在35~70kHz左右,跟单级PFC类似,Boost的工作频率也会随着输入电压的升高而升高,而后级的 DC-DC因为 Boost的前级,所以 DC-DC的输入电压为固定值。Boost在波谷周围的时候频率非常高,而且此时的工作模式为DCM 模式,震荡较多,所带来的EMI成分更大,在两级方案的EMI处理中,一般重点处理Boost级。图4-40的波形为最低电压输人,满载输出的情况下的EMI曲线。可以从图4-40上看到,现在的工作频率接近 40kHz,刚好完美的“躲”过限值,如果再往前一点,可能需要通过其他的方式去压制EMI曲线,所以我们可以选择在35kHz或者60kHz左右。35kHz的3倍频仍小于150kHz,可以轻松“躲”过这个限值,而60kHz的2倍频小于150kHz,同样也可以作为可选方案。同时,我们需要考虑的是 Boost磁心的尺寸,在不同的使用环境和项目要求中,我们需要综合考虑。

开关频率的选择可以避免在低频段超标:

前面频率的选择只是说了对于传导的部分,接着我们说下辐射的部分。频率的高低对于辐射的影响更明显,dv/dt、di/dt越大,会导致 EMI成分越多,第 4.5.5 节中讲述的慢开快关就是类似的原理,都是为了保证 EMI能顺利通过。慢开快关跟频率的高低有类似关系,在相同的时间内,频率高的开关次数更多,带来的EMI成分更多,若在最低输入情况下采用了比较高的频率,在最高输入的情况下就会有非常高的频率这样将导致辐射量提升,增加了EMI整改的难度。通常对于PFC电感,我们都会选择外包“十字架”闭合铜箔屏蔽到对应的地,横向和纵向的磁力线全部被隔开并导人地,降低辐射干扰。

选择过低的工作频率,需要更大的EMI器件,变换器发热量大、效率低,辐射比较容易通过;选择过高的工作频率,需要的EMI器件较小,驱动开关损耗和反向恢复的损耗增加,效率低,辐射难通过。选择频率的高低各有优缺点,需要折中考虑当然这里说的频率高低都只针对变频 DCM/OR 和定频CCM 这三种情况,若是全程软开关状态的拓扑不考虑在列,已超出本书的范围,这里不再赘述。

为了减小MOSFET寄生电容的影响,可以采取一些措施,如:

减小器件尺寸:器件规模越小,其寄生电容通常会越小。因此,采用更小的MOSFET器件可以降低寄生电容的影响。

优化材料和制造工艺:通过优化MOSFET的材料和制造工艺,可以降低寄生电容的大小和数量。

采用驱动电缆技术:在电路中采用双层屏蔽电缆和驱动放大器等技术,可以减小寄生电容的影响。

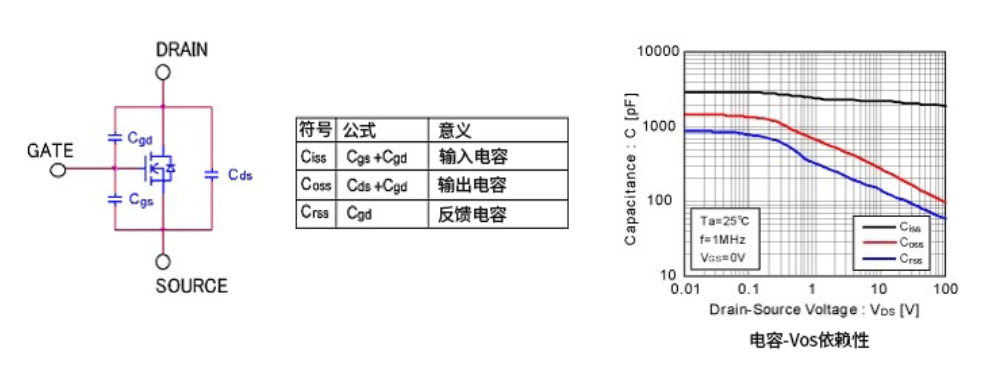

MOSFET在结构上存在下图所示的寄生电容。下图为N-ch MOSFET的例子,与P-ch的思路相同。这里谈的处理大功率的功率MOSFET,需要理解为限制使用频率和开关速度的参数。

MOSFET的栅极、漏极及源极通过栅极氧化膜被绝缘。另外,漏极-源极间借助衬底(Body/PCB板)形成PN结,存在寄生(Body)二极管

下图的栅极-源极间电容Cgs及栅极-漏极间电容Cgd取决于栅极氧化膜的静电电容。另外,漏极-源极间电容Cds是寄生二极管的结电容.

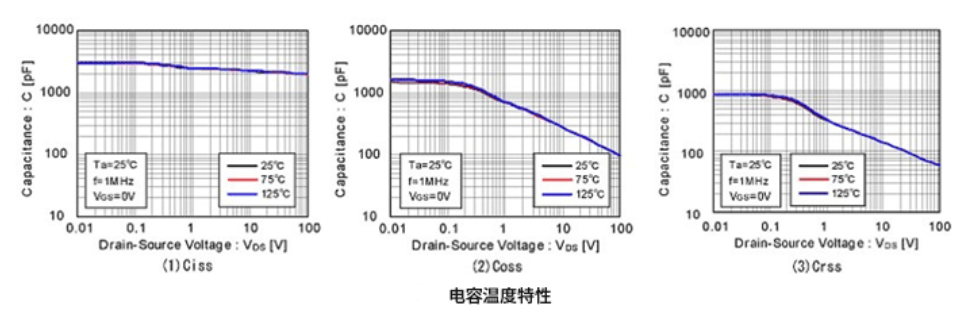

MOSFET寄生电容的温度特性

Ciss、Coss、Crss对于温度影响几乎没有变化。因此,可以说开关特性几乎不受温度变化的影响。下面是实测例。

寄生电容是MOSFET设计中不可避免的问题,但通过合理的设计和优化措施,可以将其影响降低到可接受的范围内。

我要赚赏金

我要赚赏金