今天给大侠简单带来FPGA verilog HDL实现中值滤波,话不多说,上货。一、实现步骤:

1、查看了中值滤波实现相关的网站和paper;

2、按照某篇paper的设计思想进行编程实现;

3、对各个模块进行语法检查、波形仿真、时序设计、调试验证;

4、与matlab的中值滤波结果进行比较。

二、实现过程:

1、查看了中值滤波实现相关的网站和paper;

在网上看了很多中值滤波的设计,也有一些代码可以下载,也有一片讲解的,只是感觉讲解的比较模糊而且不完整,最后看了几篇硕士论文,论文竟然主要做了中值滤波的工作,发现了一些设计思路,然后就按照自己的想法进行设计。

2、按照某篇paper的设计思想进行编程实现;

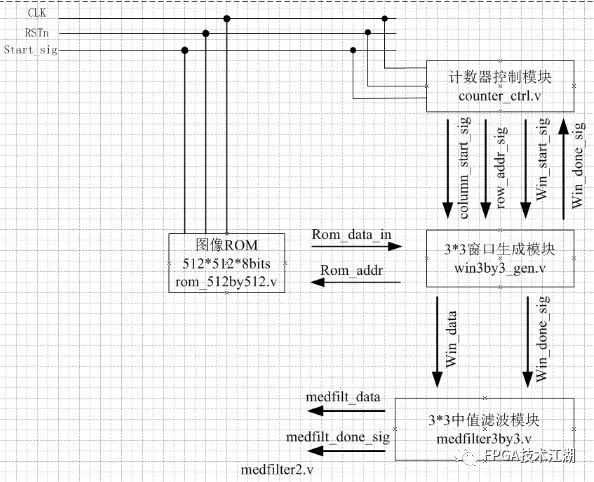

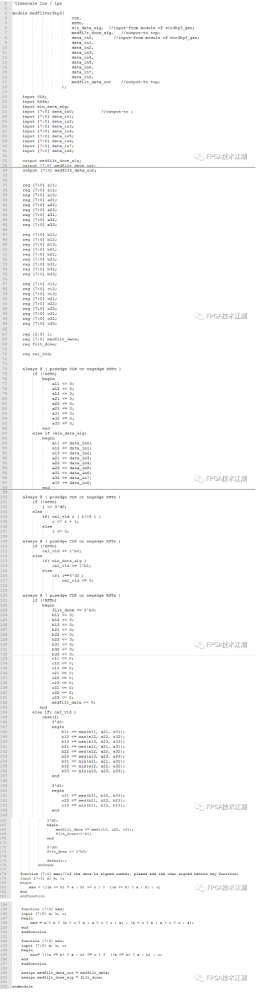

整个中值滤波模块分为几个小的模块:3*3窗口生成模块、计数器控制模块、3*3中值滤波模块、顶层模块以及最后的测试模块testbench的编写。整个框架的设计如下图所示(使用visio画的框架图):

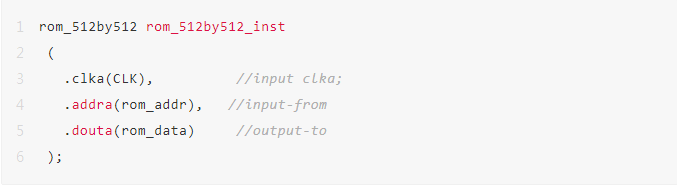

各个模块的设计:1)ROM IP核的生成,用于存储原始灰度图像的数据。

使用matlab生成.coe图像数据文件,然后使用Xilinx ISE工具将.coe文件添加到ROM核进行数据初始化,按步骤得到ROM模块,参考生成的.v文件在顶层模块直接调用即可。

注意ROM的存储空间的大小;

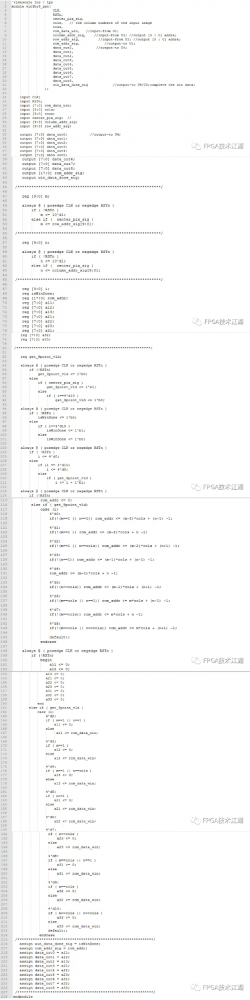

2)3*3窗口生成模块,用于生成滤波的滑动窗口,得到窗口内的所有元素数据。

功能:

(1)根据中心像素点得到所在其所在的行、列位置;

(2)根据该模块的开始信号设计得到获取数据的有效时间序列;

(3)在读取数据的有效时序内,得到窗口内的所有元素数据;

(4)窗口数据的获取按照一定的时序顺序来获得,类似于黑金推荐的“仿顺序操作”,这个比较适合my style;不过后来发现调试的过程中被项目组的硬件人员改动了一些,甚至说不好,感觉可能是本人还没有理解掌握吃透“仿顺序操作”的精髓吧。

(5)根据中心像素点的行、列位置信息得到每个窗口元素的ROM地址,根据某一时刻ROM地址,下一时刻调用ROM模块得到对应的元素数据,下一时刻将数据锁存,然后再读取该地址的数据;所以要注意地址和数据的获取不是在同一时刻,而是需要延迟两个时刻;

(6)还需要注意的是图像的边界问题的特殊化处理;一般图像处理都会遇到边界问题,这个需要谨慎;

(7)对matlab的中值滤波函数medfilt2原理的深入掌握对我们编写这一模块非常重要。matlab并没有主要过程的代码,看注释默认情况下边界元素设置为0,这也可以通过结果反推回去发现的。

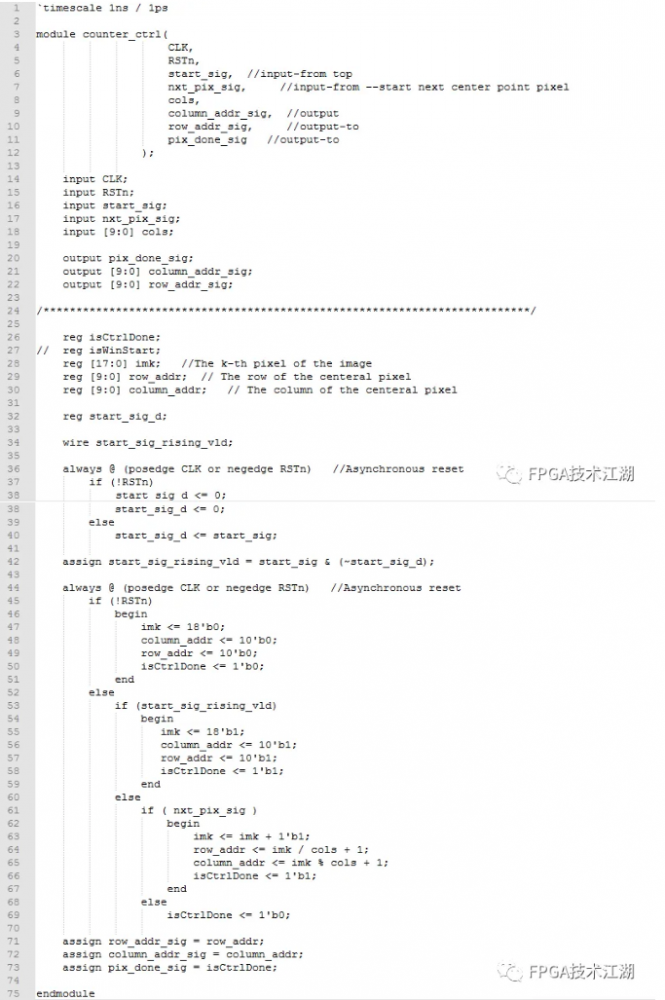

3)计数器控制模块,主要用于获得中心像素点的地址信息。

(1)系统模块开始信号之后开始获取第一个中心像素点,注意初始化信号值和系统开始的信号值的区别;

(2)该时刻得到的的数据将在下一个时刻产生结果,该时刻的数据并没有改变;

(3)注意中心像素点的行、列位置信息的计算;

4) 3*3中值滤波模块

功能:得到某一中心像素点的3*3滑窗区域的灰度值的中值,作为中心像素点的值;

中值滤波原理,网上有很多,大家可以查看一下。

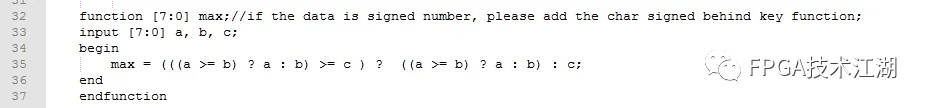

本项目采用的是快速中值滤波的方法。

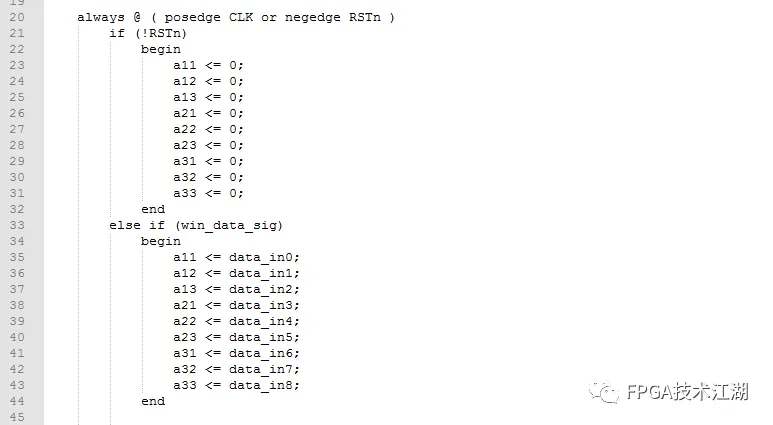

(1)若是3*3窗口生成模块完成之后就计算下一个中心像素点,需要将该中心像素点的窗口元素锁存起来,以防计算过程中将这些元素掩盖,不能正确进行中值滤波的计算;

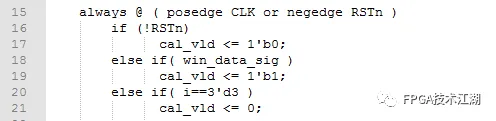

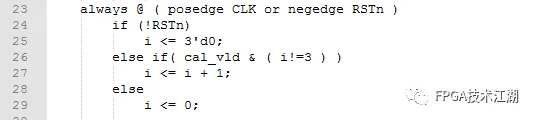

(2)需要在时序的有效区域内进行计算,怎么设计信号的有效性;

(3)仿顺序操作可以分开进行;每一个时刻只进行一个操作,这样可能更明了(代码中没有这样做);

(4)verilog编程调用函数的方法,指出输入信号,函数内可以使用其他定义声明的信号,最后的输出信号作为调用函数的结果(突然想起来,如果输出信号有多个元素呢,又该怎么办呢?大家可以想想);

该模块的代码:

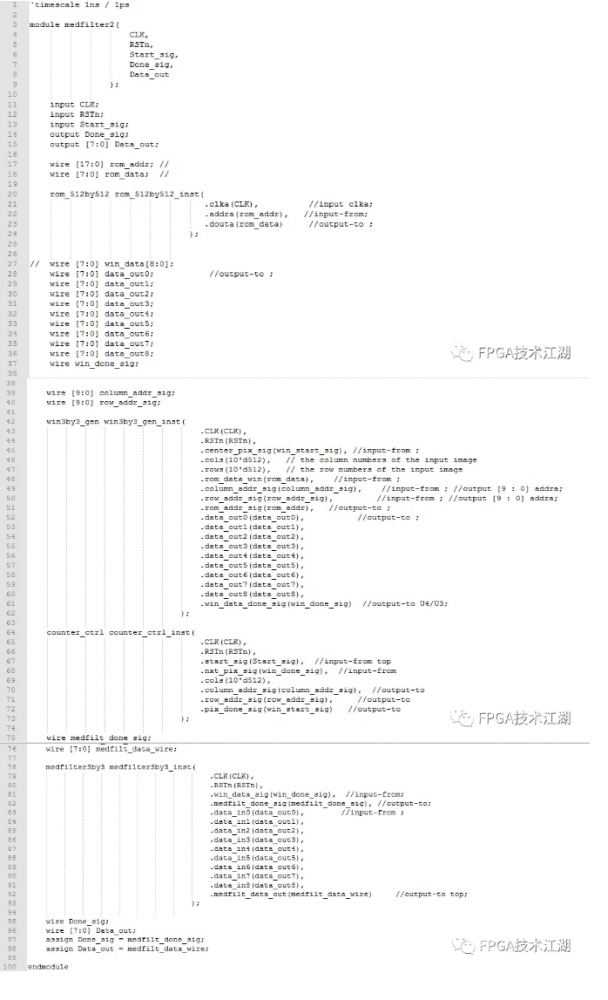

5)顶层模块

用于将低层的各个功能/控制模块衔接起来,得到结果;注意输入输出信号,以及不同模块之间是如何进行连线的。信号的名称尽量有其特别的意义,不要重复使用同一个信号名称,容易造成混乱;

区别wire和reg类型数据的使用情况;

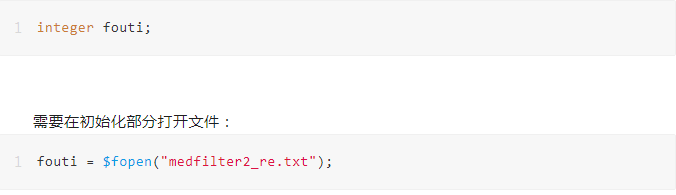

6)测试模块

如何将数据写入文件,需要定义文件的名称和类型;

代码如下:

整体的代码就是这样的。

3、对各个模块进行语法检查、波形仿真、时序设计、调试验证;

本人觉得原理清楚之后按部就班的编写代码还好,只是刚接触波形仿真和调试的时候是真心不顺心,还好有其他人帮忙调试;在调试的过程中其实会学习到很多东西,很多经验,以及很简单的但你之前就是不知道的知识,这就是一个实践的过程,有时候你根本不知道错误在哪里,这怎么会是错误的呢,为什么不可以这样写,我觉得这样写才是正确的,这些就是在调试过程中本人的真实心情写照呀。可是,没有那么多为什么,verilog就是这样编程的,只是你不知道而已!这才是最伤人的,因为你不知道!

仿真调试的过程中遇到的问题以及解决方法有空专门写一篇,调试的过程中最好是一个一个模块的测试,特别是关键信号的数值,最好搞懂整体模块和各个模块的时序设计过程,推荐使用TimeDesigner进行波形的设计;另外还需要有关联的两个甚至多个不同模块信号的交叉仿真验证。

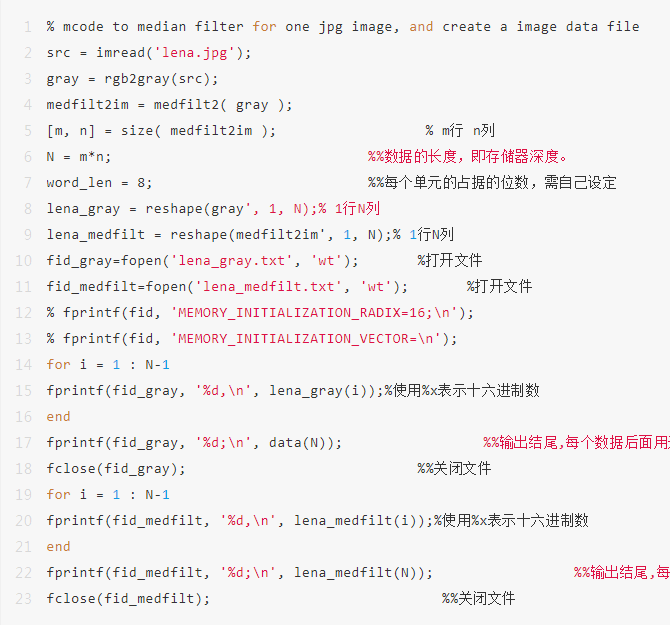

4、与matlab的中值滤波结果进行比较

使用matlab编程基于自带的中值滤波函数得到处理之后的图像与数据,并将verilog得到的滤波数据转换为图像,将二者进行比较

使用matlab自带的中值滤波函数medfilt2生成原图像的灰度图像的滤波数据;

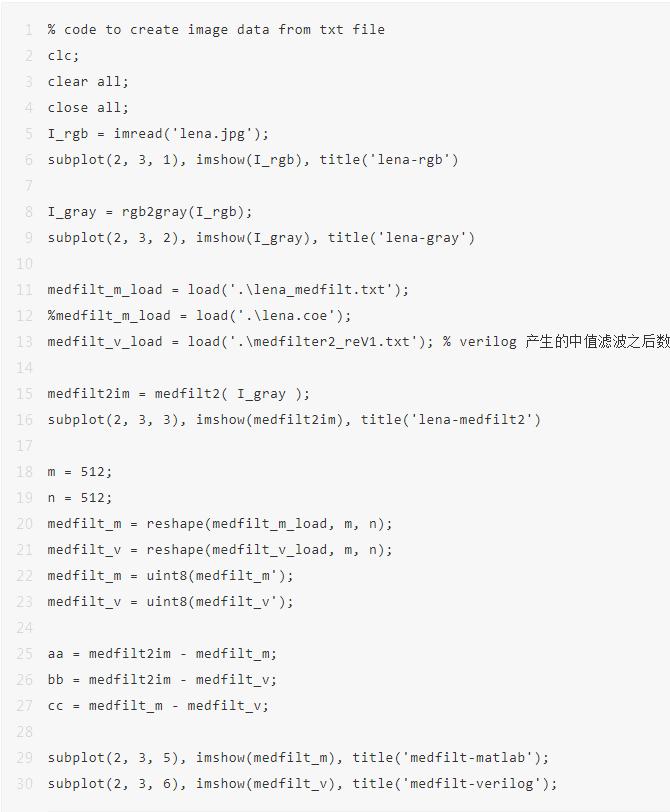

将medfilt2函数和verilog产生的滤波数据转换为图像,并与matlab直接产生的滤波图像进行对比,代码如下:

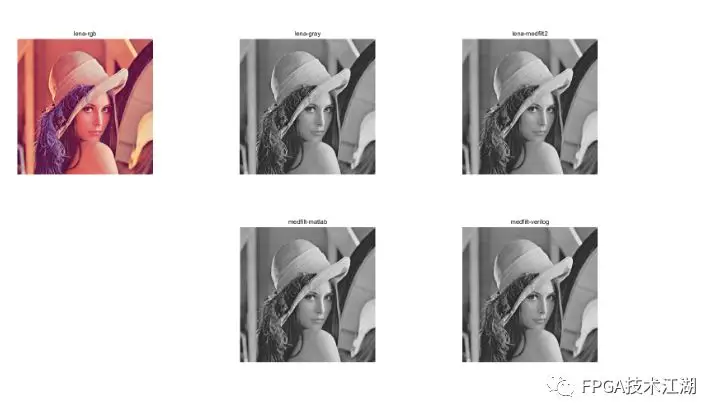

显示的结果如下图所示:

结果:两种滤波产生的图像数据完全一致,不过感觉函数直接产生的图像颜色更深一些,不知道为什么。

这里需要了解一下medfilt2这个函数的原理。结果数据表明,默认情况下该函数对图像边界采用的是补0的方法进行处理的。

结论

中值滤波终于告一段落了!简单的问题还是需要深入进去研究的,实践的过程中你才会发现自己之前了解的东西是多么的浅薄,对已知的知识掌握的是多么的流于表面!最后结果的数据还是很让人开心的!

我要赚赏金

我要赚赏金