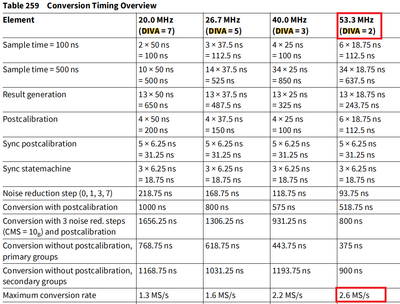

如用户手册中的下表所示,对于我使用的TC357TA评估 COOLDIM_PRG_BOARD ,最大采样率应为 2.6 MHz:

但我无法达到这个速度。

我遇到的第一个问题是,使用 iLLD API,无法将 DIVA 配置为 2,因为在 " ifxevadc_initializeFADCI

" 函数中,最大模拟频率受到 IFXEVADC_ANALOG_FREQUENCY_MAX 的限制,即 20 MHz。 我能否安全地将

IFXEVADC_ANALOG_FREQUENCY_MAX 更改为 53333333,这样模拟频率就能达到上表所示的 53.3 MHz?

我要赚赏金

我要赚赏金