IC 的 ESD 损坏可发生在任何时候,从装配到板级焊接,再到终端用户人机互动。

三个不同的器件级模型进行模拟:人体模型 (HBM)、机器模型 (MM) 和带电器件模型(CDM)。

HBM 用于模拟用户操作引起的 ESD 事件,MM 用于模拟自动操作引起的 ESD 事件,而 CDM则模拟产品充电/放电所引起的 ESD 事件。这些模型都用于制造环境下的测试。

器件级 HBM、MM和CDM 测试的目的都是保证 IC 在制造过程中不受损坏;IEC 61000-4-2规定的系统级测试用于模拟现实世界中的终端用户ESD事件。

IEC规定了两种系统级测试:接触放电和非接触放电。使用接触放电方法时,测试模拟器电极与受测器件(DUT) 保持接触。非接触放电时,模拟器的带电电极靠近 DUT,同 DUT 之间产生的火花促使放电。

IEC规定了两种系统级测试:接触放电和非接触放电。使用接触放电方法时,测试模拟器电极与受测器件(DUT) 保持接触。非接触放电时,模拟器的带电电极靠近 DUT,同 DUT 之间产生的火花促使放电。

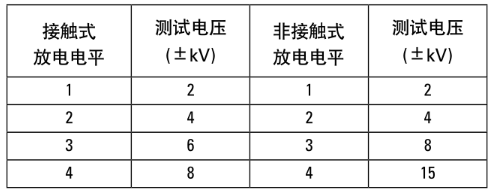

表 1 列出了 IEC 61000-4-2 标准规定的每种方法的测试级别范围。

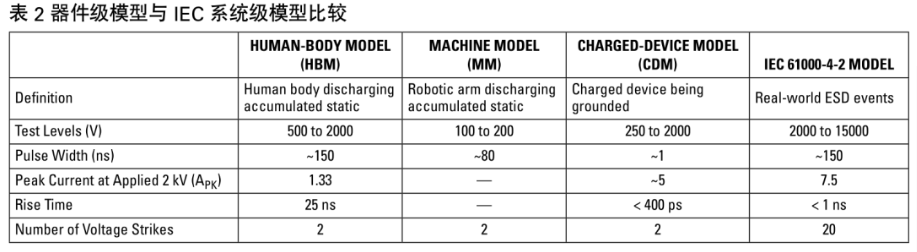

器件级模型和系统级模型有一些明显的区别,表 2 列出了这些区别。

表 2 中最后三个参数(电流、上升时间和电击次数)需特别注意:

a、电流差对于 ESD 敏感型器件是否能够承受一次 ESD 事件至关重要。

b、另一个差异存在于电压尖峰上升时间。HBM 的规定上升时间为 25ns。IEC 模型脉冲上升时间小于1ns,其在最初 3ns 消耗掉大部分能量。如果 HBM 额定的器件需 25ns 来做出响应,则在其保护电路激活以前器件就已被损坏。

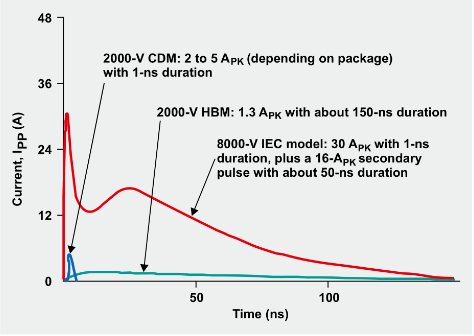

c、两种模型在测试期间所用的电击次数不同。HBM仅要求测试一次正电击和一次负电击,而 IEC 模型却要求 10 次正电击和 10 次负电击。可能出现的情况是,器件能够承受第一次电击,但由于初次电击带来的损坏仍然存在,其会在后续电击中失效。图 1 显示了 CDM、HBM 和 IEC 模型的 ESD 波形举例。很明显,相比所有器件级模型的脉冲,IEC 模型的脉冲携带了更多的能量。

我要赚赏金

我要赚赏金