在产品的设计过程中,等长匹配是需要关注的一项工作。串行信号常见的规则为+/-5mil,有的资料会给出<1ps的匹配要求。并行信号的规则就比较复杂一点。下面以常见的DDR为例,来进行相关的说明。

在芯片设计规范中,会给出很多相关信息,作为系统端设计的相关规范,关于等长匹配部分,我们需要关注的信息:

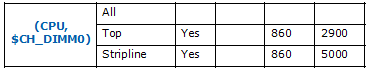

信号最大线长的要求:

关注最大线长,是因为layout工程师进行等长匹配的时候,一般以最长且不可缩短的线为基准,以此来进行等长匹配的工作,如果最大线长已经超过相关标准,就需要移动相关器件重新布局来解决问题。当然,这是一种特殊情况。

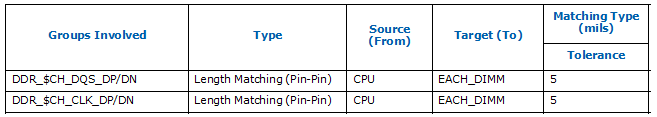

长度匹配的要求:

一个通道之间的长度匹配要求:

在等长匹配的工作中,有一个误区,就是以为长度差符合要求就可以了。下面还是以DDR并行信号为例,来解释说明一下为什么等长匹配不仅仅是等长。

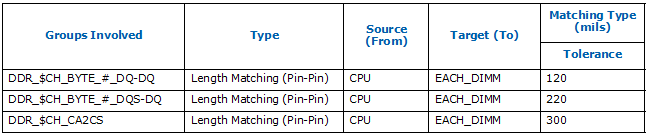

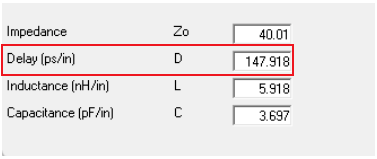

DDR单端常见的阻抗为40 ohm,表层相关的叠层信息如下图所示:

本例中,为了方便计算,介电常数设为4,信号的速率大约为6in/ns,计算得出时延是167 ps/in,而软件给出的时延是148 ps/in ,相关信息如下图所示:

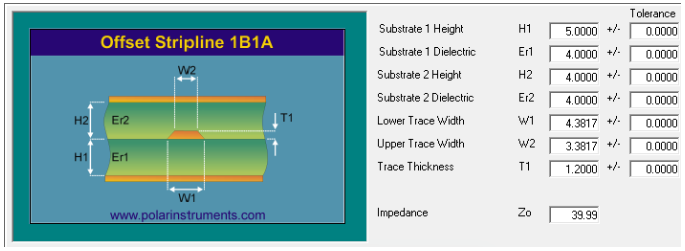

为了保证对比性和直观性,还是将介电常数设为4,内层信号层阻抗还是40 ohm,相关信息如下:

软件给出内层的是时延是169 ps/in:

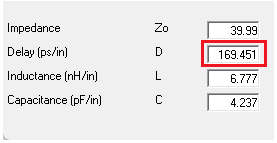

同样介电常数为4,delay延迟的数据是不同的,表层为148 ps/in,内层为169 ps/in,这说明信号在表层和内层的传输速率是不一样的,即使在表层和内层的长度完全一致,还是存在传输时延。

为了直观体现信号等长但时延差别的情况,搭建相关的电路来进行仿真验证,相关电路如下:

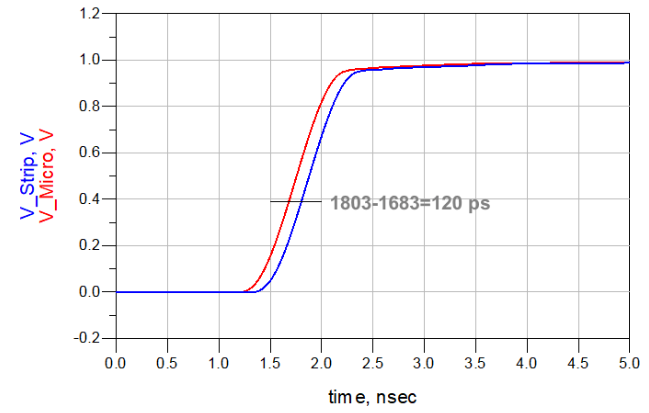

仿真得出的曲线如下:

本例取设计规范给出的最大长度5000 mil,波形可以看出即使长度匹配一样,由于信号走线层数不同,造成信号延迟的不同,竟然相差0.12 ns,以6in/ns的经验数值得出,长度匹配差值竟然达到720 mil。

实际上,等长的匹配是为了等时。芯片设计规范给出的是具体长度要求,这是因为这样可以让layout工程师在设计工作中更直观了解要求,物理规则更符合常规操作。

我们在考虑等长匹配的时候,更应该考虑的是等时,除了文中所说的线号走线层面的问题,还有玻纤效应引起的skew的问题,也是需要注意的。

等长就是为了等时,这是长度匹配的最终目的。当然,随着速率提高,要求越来越严,为了满足等时的要求,也就有了动态匹配的规则,这个要求需要参考相关的设计规范。

我要赚赏金

我要赚赏金