PN结的反向耐压是甚么回事?

少数载流子是自家的载流子吗?

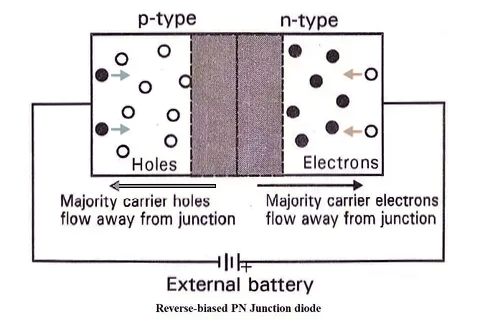

题头图中,有四颗以箭头标示,紧挨着二极体端子的载流子,

这四颗载流子的属性跟电源极性脗合,可穿越物理结面「环游世界」,

P型半导体不含电子,N型半导体没有空穴,所以,这四颗载流子实际上不是少数,而是根本就不该存在 (亦无法从电源直接注入) !!

不过,一旦有合适的环境条件,少数载流子就可出现,在二极体跟其端子之间加插外延层,就能为少数载流子提供跳板,

因为,外延层的型别跟电源极性正好是适配的,所以,少数载流子就能从外延层源源不断的发射出来,如果外延层跟物理结面的距离小于射程范围,少数载流子就能轻松地穿越结区漂向彼岸,

PN结势垒不是一扇门或一堵墙,而是一道斜坡或阶梯,对少数载流子而言反而是下坡路 (这就是我对 漂移比扩散更容易 的理解)。

硅,掺杂了才有PN之分,掺杂了才能成为可控导体,

杂质是死的,载流子是活的,不管正向反向都能动,都可通,但真个要跑起来,却得让PN结正偏才行,

图中这二极体,N正P负,PN结是反偏的,自身的载流子是「静止」的,如果我在两端都敷设外延层,这货就成了 肖克利二极管,而且是正常馈电!

对此二极体而言,外延层不是自家人,但它跟电源的关系,却是正偏,层中的载流子是能走出去的,由于外延层的型别跟宿主相反,所以这些「客席载流子」甫一出门,是以 少数载流子 的身份登场的,

外延层,相当于真空管发射电子束的灯丝,而空乏区和那些动弹不得的本地载流子,对客席 (少数) 载流子而言,相当于管内的超高真空世界,少子身处其中,根本不会受到甚么 反向阻断,而是仿如活在良导体里,完全是无障碍通行!

PN结,是紧挨物理结面的小区域,但是,PN结是不允许直接使用的,必须以足够的空间作「大后方」为辅佐,才能造成二极管,

二极体的反向耐压,就是由空乏区与大后方里的本地载流子 合力营造的,只要本地载流子没被清空,阻断能力就永远存在 (对客席载流子无效),

当电源电压超过PN结的耐压,PN结就以「击穿」的形式导通,如果把电流限制住,则二极体不会因击穿而损坏,並且一直保持等于耐压的压降,这效果正正就是 稳压管稳压作用的来由,

击穿、光电、光伏,其实都是 复合的逆过程,这逆过程是发生于空乏区内的,当电源电压超过PN结的耐压时,空乏区内就凭空冒出大量泡泡,仿如开了瓶的炭酸饮料那样,

击穿后形成的电流,就是由这些「泡泡」搭载的,电子空穴对的发生机制,有 雪崩及齐纳 两种,书本写的老师教的,对我而言不好懂,以我的理解,雪崩相当于「压碎」,齐纳则相当于「撕裂」。