解压后,点击文件中的KEIL文件

用KEIL调试

注意:

的路径为你的电脑实际的路径

效果说明:

示例摘要

切换配置为高阻态和板上LED的GPIO。

逻辑低电平被主动强制,但逻辑高电平将引脚设置为高阻态。

此特性对于开漏数字输入/输出应用非常有用。

此示例需要外部上拉电阻,但也可以使用内部上拉电阻。

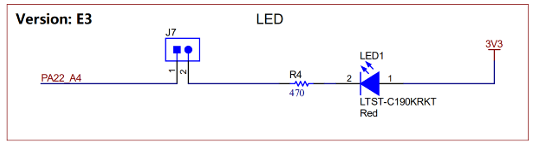

注意:示例需要MSPM0C1104 LaunchPad的E3版本或更高版本。

外围设备和引脚分配

| 外围设备 | 引脚 | 功能 |

| --- | --- | --- |

| GPIOA | PA22 | 标准输出 |

| GPIOA | PA2 | 标准输出 |

| SYSCTL | | |

| EVENT | | |

| DEBUGSS | PA20 | 调试时钟 |

| DEBUGSS | PA19 | 调试数据输入/输出 |

## BoosterPacks、板资源和跳线设置

访问[LP_MSPM0C1104](https://www.ti.com/tool/LP-MSPM0C1104)以获取LaunchPad信息,包括用户指南和硬件文件。

| 引脚 | 外围设备 | 功能 | LaunchPad引脚 | LaunchPad设置 |

| --- | --- | --- | --- | --- |

| PA22 | GPIOA | PA22 | J1_8 | N/A |

| PA2 | GPIOA | PA2 | J2_13 | <ul><li>此引脚可用于boosterpack连接器中的测试目的<ul><li>可根据需要重新配置为通用目的</ul></ul> |

| PA20 | DEBUGSS | SWCLK | J2_11 | <ul><li>PA20在调试期间由SWD使用<br><ul><li>`J101 13:14 ON` 在调试时连接到XDS-110 SWCLK<br><li>`J101 13:14 OFF` 如果在使用该引脚的应用中,则从XDS-110 SWCLK断开</ul></ul> |

| PA19 | DEBUGSS | SWDIO | J2_17 | <ul><li>PA19在调试期间由SWD使用<br><ul><li>`J101 11:12 ON` 在调试时连接到XDS-110 SWDIO<br><li>`J101 11:12 OFF` 如果在使用该引脚的应用中,则从XDS-110 SWDIO断开</ul></ul> |

设备迁移建议

该项目是为包含在LP_MSPM0C1104 LaunchPad中的超集设备开发的。请

访问[CCS用户指南](https://software-dl.ti.com/msp430/esd/MSPM0-SDK/latest/docs/english/tools/ccs_ide_guide/doc_guide/doc_guide-srcs/ccs_ide_guide.html#sysconfig-project-migration)

了解有关迁移到其他MSPM0设备的信息。

低功耗建议

TI推荐通过设置相应功能为

GPIO并将引脚配置为输出低电平或带有内部

上拉/下拉电阻的输入来终止未使用的引脚。

SysConfig允许开发人员通过选择Board→Configure Unused Pins轻松配置未使用的引脚。

有关使用

MSPM0 LaunchPad实现低功耗的跳线配置更多信息,请访问[LP-MSPM0C1104用户指南](https://www.ti.com/lit/slau908)。

示例用法

连接外部上拉电阻到引脚。

编译、加载并运行示例。

检查引脚的输出。注意,如果没有上拉电阻,当高电平时引脚将处于高阻态。

效果图片:

Debug ->Run

LED1闪烁

根据原理图:

PA22外接数码管闪烁。

编译中,如果报错,

添加:

压缩文件中已修改。

我要赚赏金

我要赚赏金