人体和衣服一天可存储 500 V 至 2,500 V 静电电荷,但是人类只能感受到 3,000 至 4,000 V 的 ESD 脉冲。这远高于电子电路受损的水平,即使人类无法检测到。

设计人员必须从多方面解决 ESD 问题,对组件制造商来说,是在其设计阶段和设计工作结束之时。简而言之,ESD 保护需要一种多层面方案。

通常,集成电路 (IC) 制造商按照 ESD 行业标准设计、测试和验证其 IC。这可防止在 IC 生产或在 PC 板上组装时出现物理损坏。针对 ESD,通常进行的两种测试包括:

● 人体模型 (HBM)。这种测试模拟人体通过接触 IC 释放所积累的静电的 ESD 事件。采用一个带电的 100 pF 电容和一个 1.5 kΩ 放电电阻进行模拟。

● 带电设备模型 (CDM)。这种测试模拟在生产设备和工艺中发生的充电和放电事件。设备在一些摩擦工艺中或静电感应过程中获得电荷,然后突然接触到一个接地物体或表面。

虽然设备级测试有助于衡量 IC 的 ESD 稳健性,但系统级测试可衡量现场的电子设备保护(即原始设备制造商 [OEM] 设备或终端产品)。

为了更好地了解最终产品所需的 ESD 保护,OEM 应采用系统级 ESD 方法进行设计,然后按照国际电工委员会 (IEC) ESD 标准 61000-4-2 测试最终产品。IEC 61000-4-2 被视为终端产品 ESD 测试和评级的行业标准。该测试可确定系统对现场外部 ESD 事件的易损性。

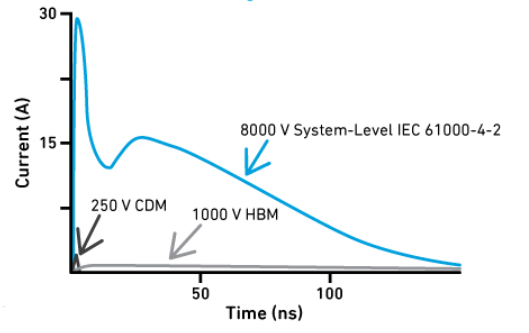

下图比较了三种脉冲的能量和峰值电流:

系统级 IEC 61000-4-2

设备级 HBM

设备级 CDM

IEC ESD 事件脉冲显然更强,因此系统中的设备更加难以通过。尽管设备级测试(HBM 和 CDM)比较有用,且可提供 ESD 稳健性的基准,但在系统级 IEC 测试期间并不总是能够确定生存性。

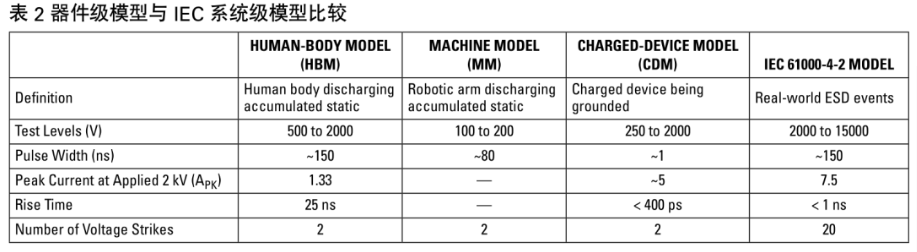

浪拓公司提供的下表显示了组件测试和系统级 IEC 测试之间的差异。大家可以看到,差异很大,系统应力水平更高。总而言之:较之于设备级设计,系统设计必须满足更严苛的要求。

我要赚赏金

我要赚赏金