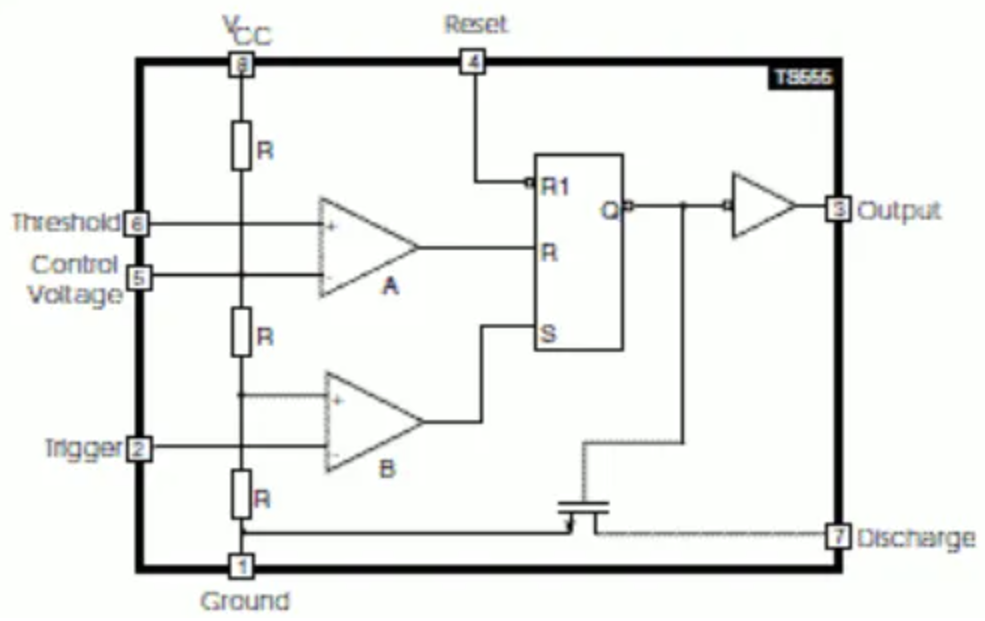

从图1的框图(取自ST的TS555低功耗单CMOS计时器的数据表)中,我们可以看到放电引脚(pin7)与输出引脚(pin3)重复。实际上,它们只同时处于“低”(Low)状态。而在“高”(High)状态下,输出引脚可以产生源电流,而放电引脚则是漏极开路(Open Drain)状态,或旧式555的开集极电路(Open Collector)状态。 图1:TS555低功耗单CMOS计时器框图(来源:STMicroelectronics)图2中的电路结合了输出和放电引脚的灌电流,使我们可以将输出电流增加一倍。电阻器R3和R4是负载的一部份,它们将灌电流限制在安全值以内。

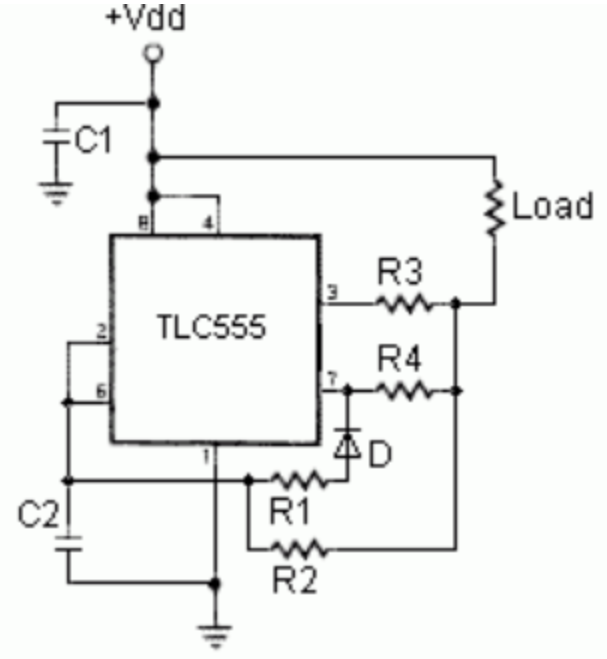

图1:TS555低功耗单CMOS计时器框图(来源:STMicroelectronics)图2中的电路结合了输出和放电引脚的灌电流,使我们可以将输出电流增加一倍。电阻器R3和R4是负载的一部份,它们将灌电流限制在安全值以内。 图2:该电路结合了TS555的输出和放电引脚的灌电流,使输出电流加倍这一倍增的代价是精度有些微下降:现在,电路更容易受到电源电压变化的影响。尽管如此,对许多应用来说,精度的小幅降低是令人可以接受的权衡折衷。现在,让我们尝试使用555的新电路来做一些有用的事情。测量电容的等效串联电阻(ESR)可能会有问题,因为ESR可能非常低,大约只有数十毫欧(mΩ)。因此,电流必须足够大,才能可靠地测量它。应用电路如图3所示。

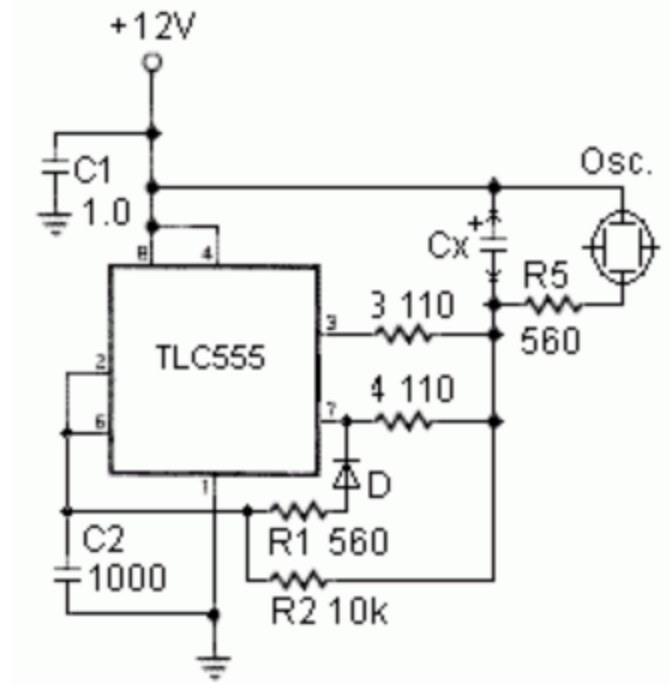

图2:该电路结合了TS555的输出和放电引脚的灌电流,使输出电流加倍这一倍增的代价是精度有些微下降:现在,电路更容易受到电源电压变化的影响。尽管如此,对许多应用来说,精度的小幅降低是令人可以接受的权衡折衷。现在,让我们尝试使用555的新电路来做一些有用的事情。测量电容的等效串联电阻(ESR)可能会有问题,因为ESR可能非常低,大约只有数十毫欧(mΩ)。因此,电流必须足够大,才能可靠地测量它。应用电路如图3所示。 图3:使用图2中介绍的概念测量电容ESR的应用电路该电路通过电容Cx产生周期约为10µs的短电流脉冲(小于1µs);电容上的压降(Vesr)与其ESR成正比。因此,将此压降与R3、Cx上的电压(V)比较,即可计算出ESR:r = R3 * Vesr / 2*(V-Vesr)或者您也可以简单地从几个备选电容中选择 ESR最低的那一个。

图3:使用图2中介绍的概念测量电容ESR的应用电路该电路通过电容Cx产生周期约为10µs的短电流脉冲(小于1µs);电容上的压降(Vesr)与其ESR成正比。因此,将此压降与R3、Cx上的电压(V)比较,即可计算出ESR:r = R3 * Vesr / 2*(V-Vesr)或者您也可以简单地从几个备选电容中选择 ESR最低的那一个。

共2条

1/1 1 跳转至页

强大的555计时器和ESR电容表

让我们看看如何有效地将普通555计时器的输出灌(sink)电流增加一倍。

关键词: 555 计时器 ESR 电容表

共2条

1/1 1 跳转至页

回复

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 【S32DS】S32K3 RTD7.0.1 HSE 组件配置报错问题解决被打赏¥27元 | |

| 【S32K3XX】MCME 启动 CORE1被打赏¥23元 | |

| AG32VH407下温度大气压传感器及其检测被打赏¥20元 | |

| AG32VH407下光照强度传感器BH1750及其检测被打赏¥22元 | |

| AT32VH407下使用温湿度传感器DHT22进行检测被打赏¥20元 | |

| DIY一个婴儿澡盆温度计被打赏¥34元 | |

| 【FreeRtos】FreeRtos+MPU region 配置规则被打赏¥23元 | |

| 【分享开发笔记,赚取电动螺丝刀】三分钟快速上手驱动墨水屏(ArduinoIDE)被打赏¥28元 | |

| 【S32K3XX】LIN 通讯模块使用被打赏¥31元 | |

| 【FreeRtos】FreeRtos + MPU模块的配置使用被打赏¥32元 | |