其余走线要求如下:

1、所有CLK信号建议串接22ohm电阻,并靠近RK3588放置,提高信号质量;

2、所有CLK信号走线不得挨在一起,避免串扰;时钟信号需要全程独立包地,包地的走线间隔300mil以内必须打一个地过孔;如图1所示

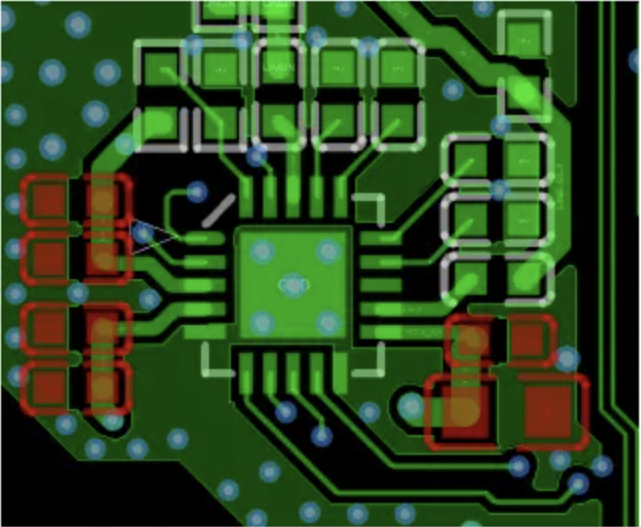

3、芯片的各IO电源的去耦电容务必靠近芯片放置;如图2所示。

图1 时钟包地处理

如图2去耦电容的放置

4、音频接口按照结构放置,没有结构要求尽量放置在板边,方便插拔;

5、IC靠近接口放置,不要放置太远,模拟信号尽量短。

6、Audio in和Audio out不用控制阻抗,走线需要加粗至15mil,全程包地处理,间隔300mil必须打一个地过孔;

7、ESD器件要靠近音频接口放置,走线需要警告ESD器件在进入音频接口,不要打孔换层,如图3所示。

图3 ESD器件的摆放

8、所有音频信号线走线应远离电感区域、远离RF信号和器件;

9、对于一个 I2S 接口接多个设备的情况,相关的 CLK 应按照菊花链走线拓扑连接;对于一个PDM接口接多个设备的情况,相关的CLK应按照菊花链走线拓扑连接;如果 GPIO 充裕情况下,PDM 接口一组内的两个CLK都可以使用,以优化走线分支;

10、所有音频信号都应远离LCD、DRAM等高速信号线。禁止在高速信号线相邻层走线,音频信号的相邻层必须为地平面,禁止在高速信号线附近打孔换层;

11、SPDIF 信号建议全程包地处理,包地的走线间隔 300mil 以内必须有地过孔;

对于外设相关音频信号要求,以对应器件设计指南为准,如果没有强调的,可参考以下说明:

1、喇叭的SPKP/SPKN信号耦合走线,并整组包地,线宽根据输出的峰值电流进行计算,并尽量缩短走线以控制线阻;

2、喇叭的功放输出如有放置磁珠、LC滤波等器件,建议靠近功放输出放置,可优化EMI;

3、Headphone的左右声道输出应独立包地,避免串扰,优化隔离度,建议走线宽度大于10mil;

4、麦克风单端连接时,MIC信号单独走线并分别包地;麦克风差分连接时,特别大多数伪差分的情况,也要按照差分走线,并整组包地;

5、麦克风信号的走线建议线宽8mil 以上;

6、对于耳机座、麦克风的TVS保护二极管,放置上尽量靠近连接座,信号拓扑为:耳机座/麦克风→TVS→IC;这样使得发生ESD现象时,ESD电流先经过TVS器件衰减;TVS器件走线上不要有残桩,TVS 的地管脚建议尽量增加地过孔,至少保证两个0.4mm*0.2mm 的过孔,加强静电泄放能力。

我要赚赏金

我要赚赏金