I2C从模式编程之时钟线保持

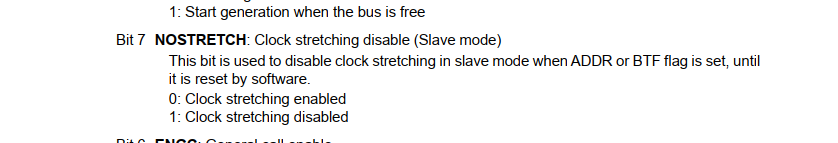

I2C从机编程我们还会遇到一个很重要的I2C特性——I2C时钟线保持。I2C SCK Stretching(有的网站翻译为时钟延展)。I2C时钟线保持功能,允许从机通过将SCL线拉低保持来暂停传输。STM32的I2C外设该功能控制寄存器为I2C_CR1的Bit7(NOSTRETCH)位,默认开启状态。

I2C时钟线保持功能的具体作用如下:

- 时钟延展是I2C通信中的一种特性,允许从机通过将SCL(时钟线)拉低来暂停传输。

- 当从机需要更多时间来处理数据或准备响应时,它会保持SCL低电平,从而延迟通信。

- 主机在检测到SCL变高之前,需要等待并不能继续发送或接收数据。

I2C时钟线保持功能的具体优势如下:

- 确保较慢的从机可以与更快的主机有效地通信,实现同步数据传输。

- 防止从机因无法及时处理数据而造成数据丢失。

- 允许从机有足够的时间准备响应,确保传输的数据有效且无误。

总体来讲,I2C时钟线保持功能是重要的一个特性,大家在编程的时候注意这个特性哟!

我要赚赏金

我要赚赏金