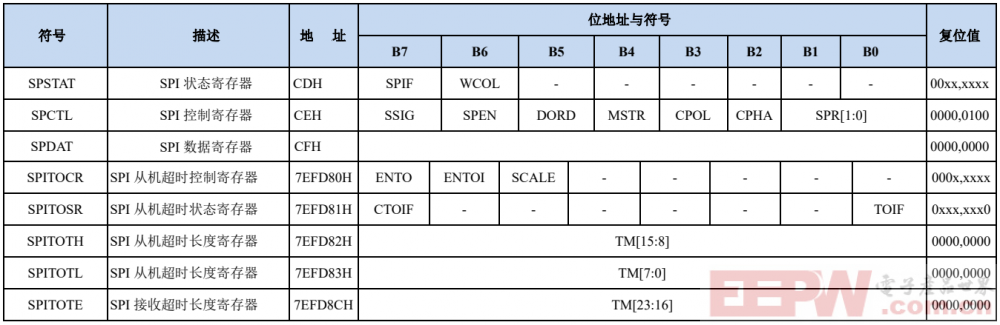

在Ai8051U 系列单片机中,与SPI外设有关的寄存器有

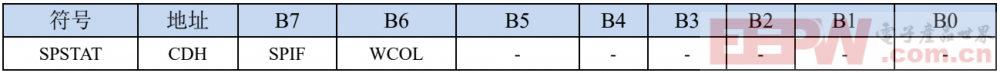

一、SPI 状态寄存器(SPSTAT)

SPIF:SPI 中断标志位。

当发送/接收完成 1 字节的数据后,硬件自动将此位置 1,并向 CPU 提出中断请求。当 SSIG 位被设

置为 0 时,由于 SS 管脚电平的变化而使得设备的主/从模式发生改变时,此标志位也会被硬件自动

置 1,以标志设备模式发生变化。

注意:此标志位必须用户通过软件方式向此位写 1 进行清零。

WCOL:SPI 写冲突标志位。

当 SPI 在进行数据传输的过程中写 SPDAT 寄存器时,硬件将此位置 1。

注意:此标志位必须用户通过软件方式向此位写 1 进行清零。

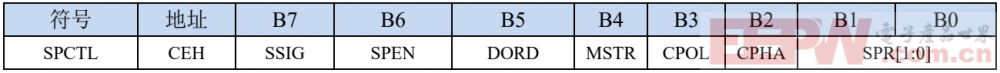

二、SPI 控制寄存器(SPCTL),SPI 速度控制

SSIG:SS 引脚功能控制位

0:SS 引脚确定器件是主机还是从机

1:忽略 SS 引脚功能,使用 MSTR 确定器件是主机还是从机

SPEN:SPI 使能控制位

0:关闭 SPI 功能

1:使能 SPI 功能

DORD:SPI 数据位发送/接收的顺序

0:先发送/接收数据的高位(MSB)

1:先发送/接收数据的低位(LSB)

MSTR:器件主/从模式选择位

设置主机模式:

若 SSIG=0,则 SS 管脚必须为高电平且设置 MSTR 为 1

若 SSIG=1,则只需要设置 MSTR 为 1(忽略 SS 管脚的电平)

设置从机模式:

若 SSIG=0,则 SS 管脚必须为低电平(与 MSTR 位无关)

若 SSIG=1,则只需要设置 MSTR 为 0(忽略 SS 管脚的电平)

CPOL:SPI 时钟极性控制

0:SCLK 空闲时为低电平,SCLK 的前时钟沿为上升沿,后时钟沿为下降沿

1:SCLK 空闲时为高电平,SCLK 的前时钟沿为下降沿,后时钟沿为上升沿

CPHA:SPI 时钟相位控制

0:数据 SS 管脚为低电平驱动第一位数据并在 SCLK 的后时钟沿改变数据,前时钟沿采样数据(必须 SSIG=0)

1:数据在 SCLK 的前时钟沿驱动,后时钟沿采样

SPR[1:0]:SPI 时钟频率选择

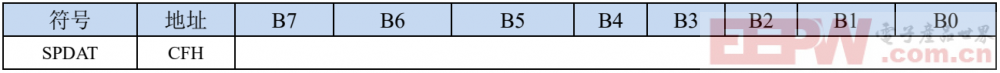

三、SPI 数据寄存器(SPDAT)

SPI 发送/接收数据缓冲器。

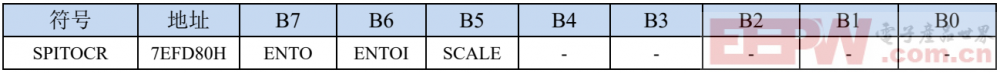

四、SPI 从机超时控制寄存器(SPITOCR)

ENTO:SPI 从机超时功能控制位

0:禁止 SPI 从机超时功能

1:使能 SPI 从机超时功能(注:SPI 的主机模式不要使能接收超时功能)

ENTOI:SPI 从机超时中断控制位

0:禁止 SPI 从机超时中断

1:使能 SPI 从机超时中断

SCALE:SPI 从机计数时钟源选择

0:1us 时钟(1MHz 时钟)。(注意:如需要使用此时钟源,用户必须先正确设置 IAP_TPS 寄存器。

例如:若系统时钟为 12MHz,则需要将 IAP_TPS 设置为 12;若系统时钟为 22.1184MHz,则需要将 IAP_TPS 设置为 22;其他频率以此类推。

特别注意,此 1us 的时钟并不是精准时间

1:系统时钟

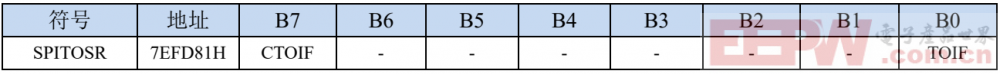

五、SPI 从机超时状态寄存器(SPITOSR)

CTOIF:写“1”清除 SPI 超时中断标志位 TOIF。(只写)

TOIF:SPI 超时中断请求标志位。(只读)

当发生 SPI 超时时,TOIF 会被硬件置“1”。如果 ENTOI 为 1 时会产生 SPI 中断,中断入口地址为原 SPI 的中断入口地址。标志位需要软件向 CTOIF 位写“1”清零

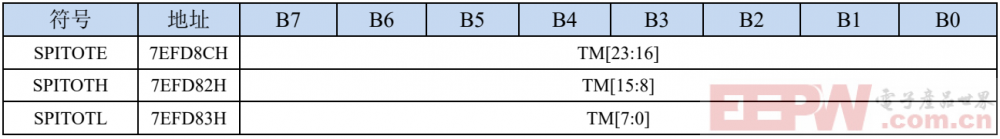

六、SPI 从机超时长度控制寄存器(SPITOTE/H/L)

TM[23:0]:SPI 超时时间控制位。

当 SPI 处于接收空闲状态时,内部超时计数器根据 SCALE 寄存器所选择的时钟源进行计数,当计数时间达到 TM 所设置的超时时间时,便会产生超时中断。当 SPI 接收数据完成时,复位内部超时计数器,重新进行超时计数。

注:

1、如果需要使能接收超时中断功能,则 TM 不可设置为 0,且 SPITOTL、SPITOTH、SPITOTE寄存器的设置必须先设置 SPITOTL 和 SPITOTH,最后设置 SPITOTE

2、必须设置 SPI 为从机模式才有接收超时功能

3、接收超时功能必须在正确接收到一字节数据后才能触发

4、正在接收过程中,无接收超时功能

我要赚赏金

我要赚赏金