今天分享一个PMOS的电路设计,详细了解下各个元器件在电路中起到的作用。

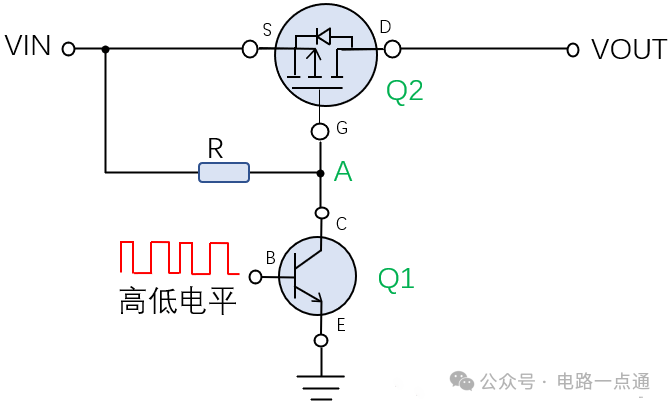

这里的Q1为NPN三极管,Q2为PMOS管,MCU通过高低电平控制三极管Q1的导通和关断。

当Q1关断时,由于电阻R没有电流流过,A点的电压等于Vin,也就是说Q2的栅极电压VG等于Vin,此时Q2的源极电压VS也等于Vin,Q2的G、S两端的电压等于0,Q2关断,此时的VOUT输出关断。

当Q1导通时,A点电压为0,此时的Q2是G、S电压为0-Vin=-Vin,当-Vin满足Q2的PMOS 管的导通门限电压,Q2导通,也就是说Vout输出导通。

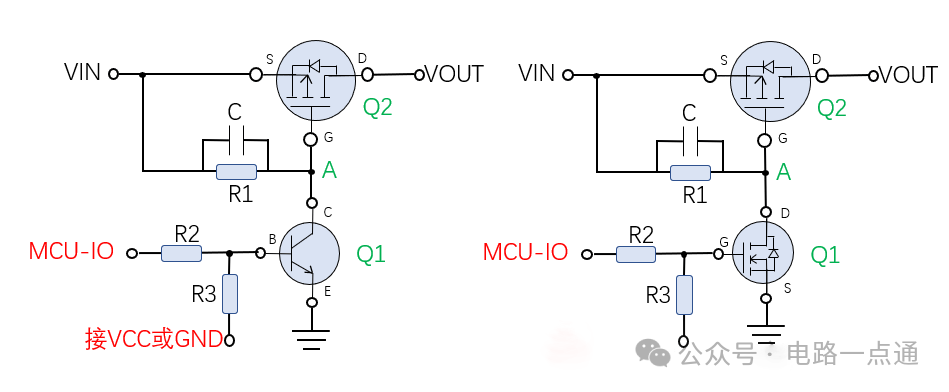

开关管Q1

可以选择NMOS或者NPN三极管,根据MCU的IO电压来选择MOS管的开启电压要大于三极管的开启电压。

限流电阻R2

R2的选值要根据MCU的IO电压、最大输出电流和开关管Q1的类型来选择,MOS管的限流电阻通常可以在几十Ω级别,三极管的限流电阻要根据MCU的IO电压/最大输出电流来计算,一般在kΩ级别。

上下电阻R3

R3可作为上拉电阻,也可作为下拉电阻。

这是根据VOUT的默认状态来决定的,在上电时,MCU还没准备好,此时就需要一个电阻来固定电平;如果默认VOUT上电,那么R3就需要上拉,反之则是下拉,

上拉的电压VCC是MCU的IO供电电压。

GS并联电容C

在PMOS的GS之间并联一个电容C。当开启PMOS时,先给电容C充电,此时PMOS的VGS从0开始上升,PMOS经过可变电阻再到饱和区,可以防止开通瞬间后级电路中,各种因素,导致PMOS被大电流冲击。

GS电阻R1

R1的选值在几十上百KΩ,能有效减小Q1导通时的功耗。不过这里要注意,R1给MOS的GS电容提供了放电回路,如果R1过大,就会导致MOS管关断速度变慢。

我要赚赏金

我要赚赏金