单芯片功率集成电路的数据手册通常会规定两个电流限值:最大持续电流限值和峰值瞬态电流限值。其中,峰值瞬态电流受集成功率场效应晶体管(FET)的限制,而持续电流限值则受热性能影响。数据手册中给出的持续电流限值,是基于典型电压转换、室温条件和标准演示板工况得出的。在特定工作环境中,实施有效的热设计对于确保集成电路可靠承载所需电流至关重要。

热概念和参数

为清晰起见,表1列出了稳态电气参数与热参数的类比关系。

表1. 参数转换

从稳态角度来看,电气领域中电流从高电位流向低电位,倾向于选择电阻更低的路径。类似地,在热领域中,热能从高温区域向低温区域耗散,且通过热阻更低的路径会产生更大的能量耗散。

在功率集成电路应用中,通常将结(裸片)视为热源,表1中的热方程可调整如下:

其中:

TJ是集成电路结温。

TA是环境温度。

PLOSS是集成电路功率损耗。

θJA是结至环境热阻。

根据公式1,降低集成电路的功率损耗或热阻,均可帮助减小结至环境的温差(ΔTJA)并改善热性能。

散热模式

散热模式有三种:

热传导:通过直接接触散热。

热对流:通过周围流动的流体带走热量。

热辐射:以电磁波的形式散热。

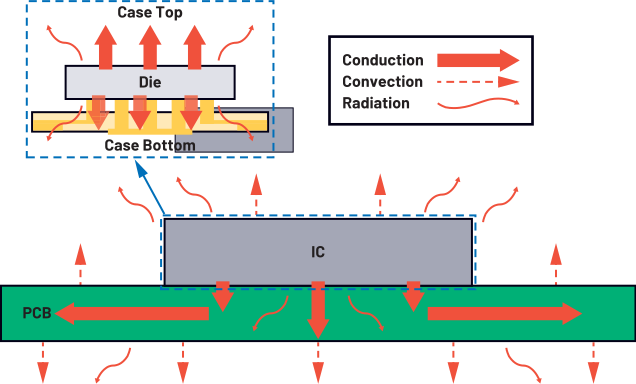

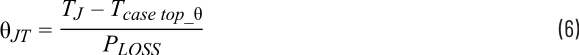

如图1所示,在集成电路(IC)应用中,热传导通常指的是在IC封装 内部通过PCB铜箔进行散热。热对流通常发生在IC或PCB表面与周 围空气之间。热辐射无处不在,因为它不需要介质。

图1. IC应用中的散热。

计算不同散热方式的热阻:

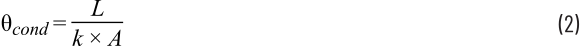

热传导:

其中,L是材料长度或热传导距离(m),k是材料的热导率[W/(m × K)], 而A是材料的横截面积(m2)。

热对流:

其中,h是热传递系数[W/(K × m2)], Acool是散热面积

热辐射:

其中,ε是材料的热发射率,σ是斯特凡-玻尔兹曼常数,Asurf是 表面积(m2),Tsurf是表面温度(K),而Ta则是环境温度(K)。

从公式4可见,辐射模式下的热阻高度依赖于温度。随着温度升高,θradi降低,这使得在实际场景中针对性地降低θradi颇具难度。因此,后续章节将重点探讨热传导和热对流模式下的热阻。

简化热模型

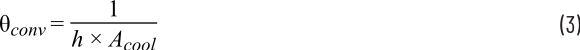

如图2所示,现引入简化的热模型,以评估系统级(板载芯片) 的热性能。

图2. 简化的热模型。

此模型将 θJA分解为四个不同的参数:

θJT(θJCtop): 集成电路结至外壳热阻。

θJB: 集成电路结至板热阻。

θTA: 集成电路外壳顶部至环境热阻。

θBA: 板至环境热阻。

这些参数之间的关系如下:

θ与ψ的区别

一些数据手册将θ和ψ值列为热参数,其中θ指实际热阻,ψ则表示热特性值。例如,考虑 θJT和ψJT:

主要区别在于,公式6假设热能仅通过集成电路外壳顶部耗散,而公式7假设热能通过所有可能的路径耗散。因此,在自然散热的实际应用中,使用 ψJT而非θJT来计算结温更为准确:

需要注意的是,ψJT并非热阻,不具备物理意义;它仅仅从系统 角度表示 TJ与Tcasetop之间的数值关系。此外, ψJT无法用于构建热模型。类似的区别也适用于 θJB和ψJB。

集成电路封装的影响

功率集成电路内部的散热主要通过传导方式进行,如公式2所述。表2列出了集成电路封装中常用材料的热导率值,这些数据可用于评估不同封装结构的散热路径。需要注意的是,这些数值也会受到温度的影响。

表2. 集成电路中不同材料的热导率

带底部裸露散热焊盘的焊线封装(ADI MSE)

图3展示了ADI MSE封装的标准结构,包含焊线和裸露底部焊盘。结合表2中的数据,引入表3以评估不同的散热路径。其中热阻最低的路径为“裸片-裸片贴装-底部裸露焊盘”结构。

图3. MSE封装的典型结构。

表3. MSE中的散热路径

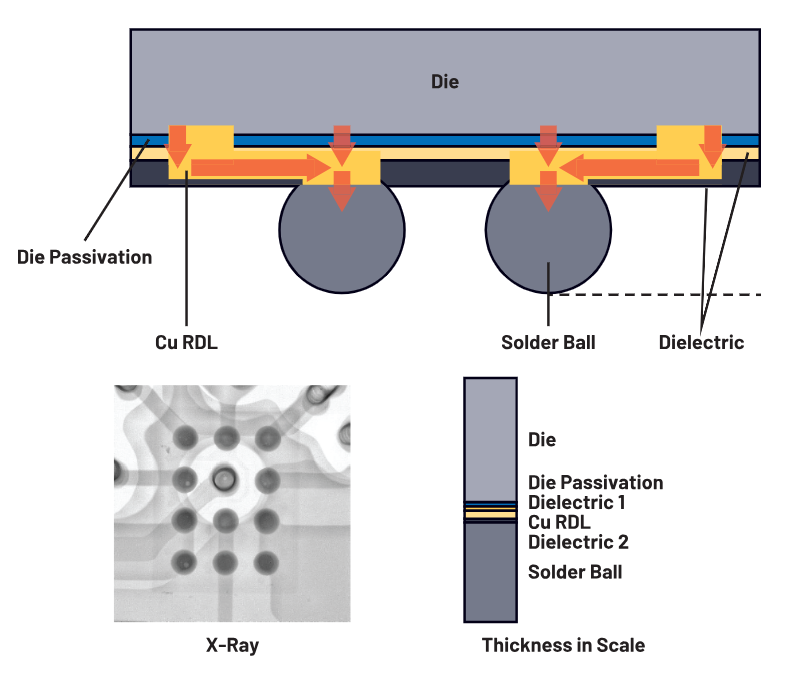

晶圆级芯片规模封装(WLCSP)

图4展示了WLCSP的标准结构。相应地,表4提供了WLCSP的详细信息,其中强调热阻最低的最优散热路径为“芯片-铜重分布层(RDL)-焊球”结构。

图4.WLCSP的典型结构。

表4. WLCSP中的散热路径

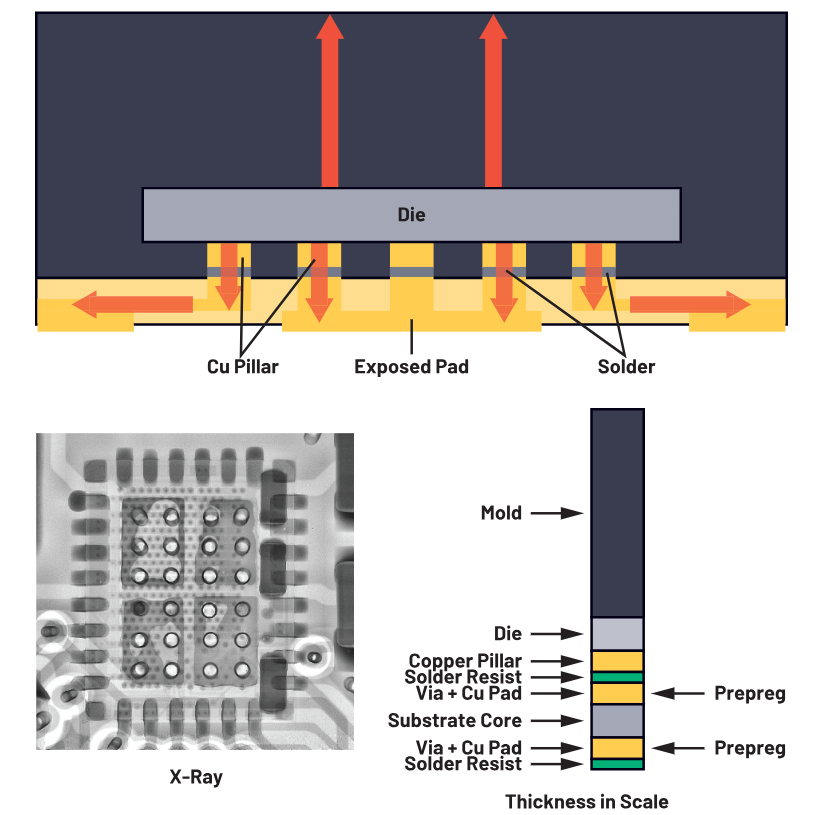

带底部裸露散热焊盘的倒装芯片封装 (ADI LQFN)

图5展示了ADI LQFN封装的标准结构。结合表5可知,热阻最低的散热路径是通过“芯片-铜柱-焊料”及底部裸露焊盘构成的。

图5. LQFN封装的典型结构

表5. LQFN中的散热路径

基于封装特性的θ和ψ数值差异

如前文所述,热阻θ是在假设热量沿特定方向耗散的条件下计算得出的,而ψ值则是基于自然散热条件确定的。在封装结构中,顶部的环氧模塑化合物热导率相对较低,且散热路径较长。因此,仅有极少热能通过顶部耗散,导致Tcasetop接近TJ。根据公式6和7,ψJT显著小于θJT。相反,由于大部分热能通过IC外壳底部和PCB耗散,ψJB值通常与θJB接近。

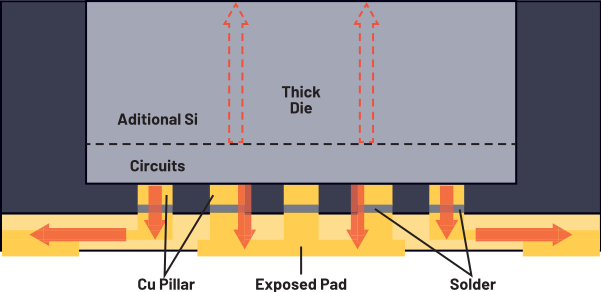

裸露芯片封装

与顶部覆盖环氧层的封装不同,裸露芯片封装的芯片厚度更大。图6展示了带有裸露芯片的LQFN封装的典型结构。

图6. 裸露芯片LQFN封装的典型结构。

顶部额外的硅层降低了热源至外壳顶部的热阻(θJT),从而增强了封装顶部的散热能力。然而,在自然散热条件下,由于其他系统级因素会影响整体热阻,裸露芯片封装并未显著提升热性能。裸露芯片封装的热优势将在第二部分中详细介绍。

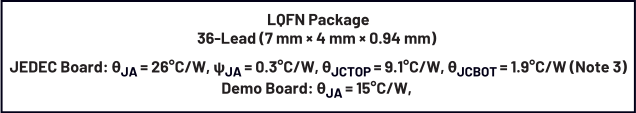

数据手册上的热参数

功率集成电路数据手册通常会列出多个热参数以供参考,如图7所示。由于集成电路封装的特性,θJCBOTT小于θJT(θJCTOP),而 ψJT显著小于θJT(JCTOP)。在自然散热条件下,使用θJT计算 TJ可能会导致显著误差。此外,需要注意θJCBOT与θJB不同,因为θJB表示的是结与板之间的热阻,而非结与IC外壳底部之间的热阻。

图7. 数据手册上的热参数。

示例中同时列出了JEDEC和演示板的 θJA值。JEDEC板是根据JEDEC标 准51-7构建的,用于测量热参数。通常,JEDEC板的布局未针对 散热进行优化,因此其JA值高于演示板。一般而言,JEDEC板上的θJA反映了集成电路封装本身的热性能,而演示板上的θJA则表示经过优化的系统设计值。

结语

在功率集成电路(IC)封装内部,热传导是主要的散热模式。根据封装内部材料的热特性,部分内部路径的热阻可能较低。然而,实际的散热路径还会受到系统级因素的影响,例如装配方式、印刷电路板(PCB)设计、风冷散热、散热片的使用等。有关 这些系统级因素的更多细节,将在第二部分中介绍。

我要赚赏金

我要赚赏金