引 言

FPGA广泛应用在电子通信领域,其安全性引起了注意,本文针对安全配置提出了解决方案。

现场可编程门阵列FPGA(Field Programmablc Gate Array)是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。采用在线可重配置方式ICR(In-Circuit Reconfigurability)将这些配置数据配置到FPGA内部SRAM中,但由于SRAM的易失性,每次上电时,都必须对FPGA重新进行配置,从而实现用户编程所要实现的功能。

以前的设计大多是将配置数据存放在FPGA组成的系统上,本文提出将配置数据存放在使用者自己携带的外部存储器(如可加密的U盘)中。使用前将U盘接入FPGA组成的系统,系统上电时由单片机控制读出配置数据,再传送给FPGA进行配置。这样做优点很多:修改、升级简便,现场保密性强,安全性高;可多人分时使用同一硬件系统,同一硬件系统插入不同的配置U盘就可以实现不同的功能,可以方便地存储大容量配置数据或多个配置数据文件等;同时,符合计算机和嵌入式系统的热点USB OT

G(On The Go,移动USB)技术趋势,是具有创新的设计。

1 FPGA的配置方式和配置数据文件

1.1 FPGA的配置方式

以Altera公司的FPGA器件为例,有2类配置下载方式:主动配置和被动配置。主动配置方式是由FPGA器件主动引导配置操作,从外围专用配置芯片(如EPC4)中获得配置数据的过程;被动配置方式则是由外部计算机或控制器控制配置过程。

以Mercury、APEX 20K(2.5V)、ACEX 1K和FLEX10K系列FPGA为例,配置方式有:被动串行PS(PasiveSerial)、被动并行同步PPS(Passive Parallel Synchronous)、被动并行异步PPA(Passive Parallel Asyn-chronous)和JTAG(Jont Test Action Group)等。具体配置方式由方式选择引脚MSEL1和MSELO的逻辑电平组合决定。

基于SRAM LUT(查找表)结构的FPGA采用在线可重配置方式ICR。以配置方式PS为例,可通过下载电缆南计算机直接对FPGA器件进行配置。这种方法在设计调试时非常方便,但在现场应用巾是很不现实的。上电后自动加载对FPGA器件进行配置是实际必须的,有许多方法,例如专用配置芯片(如EPC4)配置、单片机控制配置、MAX3000A控制F1ash存储器配置、PCI总线配置、Internet配置、PSD(Programmable System Devices可编程器件)配置等。

1.2 FPGA的配置数据文件

Altera公司的Quartus II开发工具可以生成多种配置或编译文件,用于不同配置方式。对于不同的目标器件,编译后开发工具会根据指定的FPGA器件自动生成“.sof(SRAM Object File)”和“.pof(Programmer ObjectFile)”配置文件。“.sof”配置文件是由下载电缆将其下载到FPGA中的;“.pof”配置文件是存放在配置器件里的。用单片机配置时,要将“.sof”文件转换成“.rbf(Raw BinaryFile)”文件,可打开QuartusII的File菜单,单击ConvertProgramming Fiks进行转换。配置文件的大小随FPGA器件的不同而不同,例如EPFlOKlO的配置文件“.sof”和“.rbf”的大小为15KB。

2 单片机配置FPGA设计

2.1 单片机配置FPGA的优点

在实际应用中,单片机控制配置FPGA,对于保密和升级,以及实现多任务电路结构重配置和降低配置成本,都是很好的选择。配置方式PS、PPS和PPA均可以用单片机控制配置。

由单片机和外部存储器组成配置FPGA电路,将配置数据写入外部存储器,系统上电时再由单片机控制对FPGA进行配置。也可将多个配置文件分区存储到外部存储器中,然后由单片机接收不同的命令,选择读取不同存储区的数据配置到FPGA器件,从而实现多任务电路结构重配置,在线配置成多种不同的电路功能;代替了价格昂贵的不可擦写和可擦写配置芯片,降低了成本。

2.2 配置数据存储在U盘

在银行等保密行业,如果要求安全和保密程度非常高,那么一定要有权限的使用者才能使用,或由不同的用户分时使用同一台FPGA组成的系统。最好是不要将配置数据存放在FPGA组成的系统上,而是将配置数据存放在使用者自己携带的外部存储器(如U盘)中(对U盘的读/写还可以加密);使用前将存放配置数据的外部存储器接入FPGA组成的系统,系统上电时冉由单片机控制对FPGA进行配置就可以了。

1994年11月,以Intel为首的7家公司推出了通用串行总线USB(Universal serial Bus)协议规范的第一个草案。USB协议从1.1过渡到2.0,作为其最重要指标的设备传输速度也从USBl.1标准的低速1.5 Mbps和全速12Mbps提高到USB2.0标准的高速480Mbps。目前,USB设备已经非常普遍,USB接口以其速度快、功耗低、支持即插即用、使用安装方便和价格低廉等优点得到了广泛应用。USB OTG已经成为嵌入式系统领域中的热点,使得USB能应用在没有PC的领域中,实现移动数据交换和存储。本文提出将配置数据存储在U盘中,通过单片机控制读/写,符合USB OTG发展趋势,将在嵌入式和FPGA领域得到广泛应用。

2.3 单片机读取存储在u盘中的配置数据

通常USB设备终端必须与计算机连接。如果没有PC,则需要通过USB总线的通用接口芯片(当然也可以利用带USB接口的单片机)控制U盘的读/写。本设计采用单片机AT89S52控制USB总线的通用接口芯片CH375来读取存储在U盘的配置数据。

CH375是一个USB总线的通用接口芯片,内部集成了PLL倍频器、主从USB接口SIE、数据缓冲区、被动并行接口、异步串行接口、命令解释器、控制传输的协议处理器和通用的固件程序等;支持USB-HOST主机方式和USB-DEVICE/SL****E没备方式,可以方便地挂接到单片机/DSP/MCU/MPU等控制器的系统总线上。外部单片机可以直接以扇区为基本单位读/写常用的USB存储设备(包括USB硬盘、USB闪存盘和U盘)。

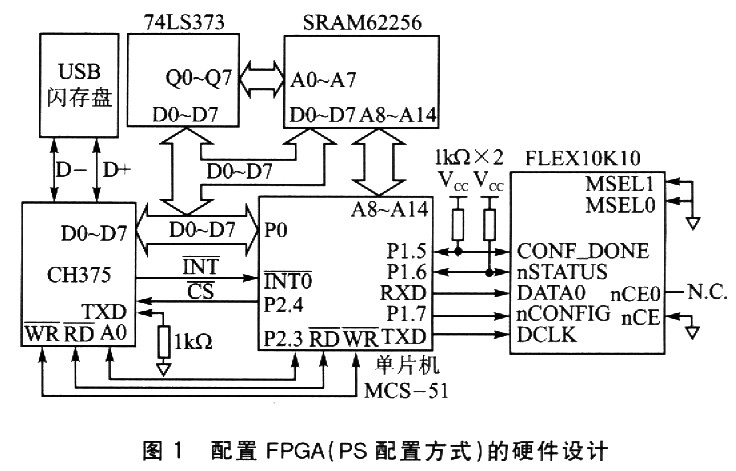

硬件设计:CH375工作于并口方式,与普通的MCS-5l单片机的连接如图1所示。CH375的TXD引脚通过l kΩ左右的下拉电阻接地或者直接接地,从而使CH375工作于并口方式。

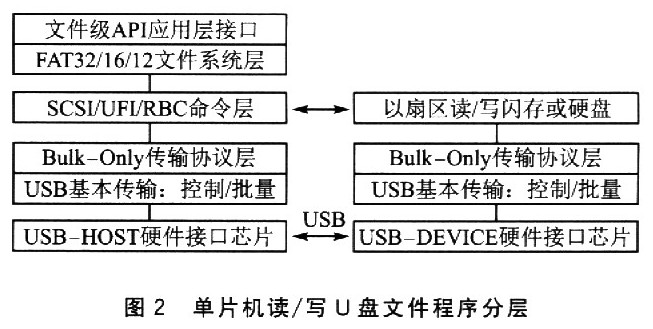

软件设计:①进入USB主机模式,要读/写U盘,必须先设置CH375使其工作于USB主机方式。②将U盘当作存储器进行读/写,方法与读/写闪存差不多,操作简单且速度快。单片机读/写U盘文件程序分层如图2所示。

2.4 用单片机配置FPGA的过程

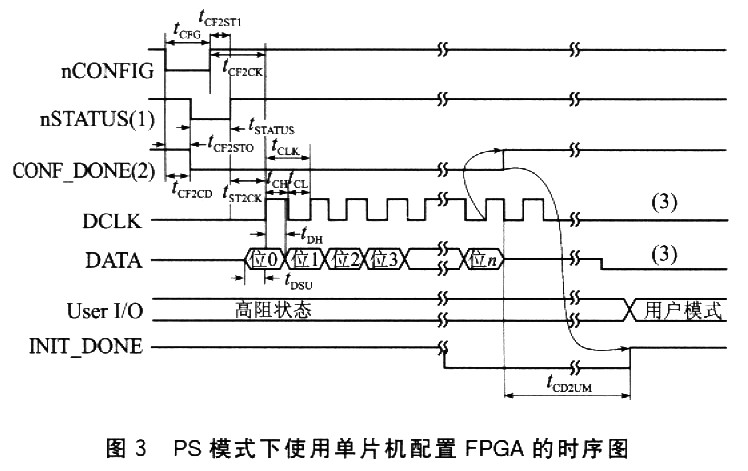

FPGA器件上电以后,开始配置过程的复位、配置和初始化3个阶段,然后进入用户状态。以配置FLEX10K10为例,图3为PS模式下使用单片机配置FPGA的时序图。

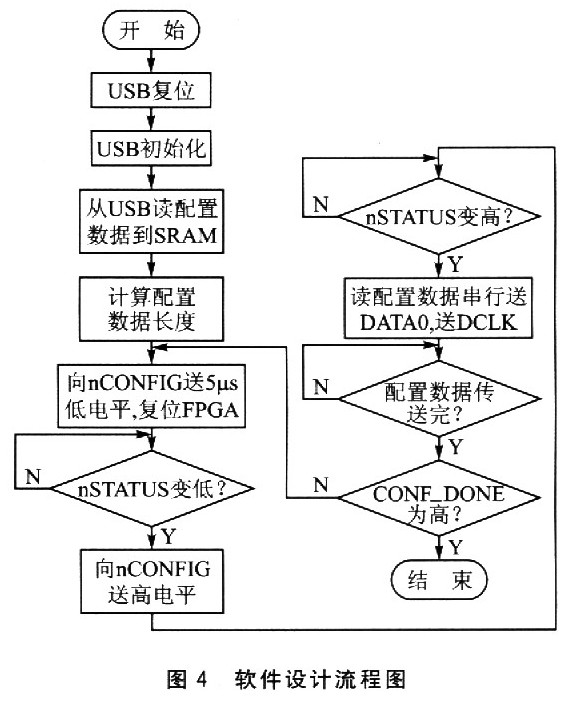

配置过程如下:①MCU的P1.7引脚产生一个tCFG≥μs的低电平给FPGA的nCONFIG引脚使FPGA复位,200 ns后nSTATUS和CONF_DONE同时跟随变为低电平;FPGA的I/O端口为高阻状态,RAM被清除。②MCU的P1.7引脚产生上跳变时开始配置,FPGA退出复位状态,4μs后nSTATUS被释放并被上拉电阻拉高,FPGA准备接收数据进入配置阶段。设置MCU的串口工作方式为O,单片机检测到nSTATUS由低跳到高后,读取配置数据(从U盘读取或上电时先将配置数据从U盘读到SRAM62255)由RXD送到FPGA的DATA0(注意低位LSB先送出);MCU的TXD接收FPGA的DCLK以提供时钟信号,配置数据足在DCLK上升沿被移位入FPGA的,全部配置数据移入FPGA直到CONF_DONE变为高电平,配置阶段结束。若CONF_DONE没有变为高电平,则需要重新配置。③初始化阶段,持续O.6~2μs。不同的FPGA器件,持续时间不等。A1tera公司的Quartus II开发工具生成配置文件时,对于不同的目标器件和配置方式已经添加了相应的空DCLK。软件设计使微处理器提供配置所需的时序和串行传送配置数据,以及对配置进行监测,从而实现配置过程。软件设计流程如图4所示

3 结论

FPGA器件的配置技术犹如集成电路制造中的流片,是非常重要的一个环节。用单片机配置FPGA器件与用专用器件相比,具有成本低、保密性好、可升级、可实现多任务电路结构重构(符合软件无线电思想)等特点,本设计具有创新性,硬件设计简单可靠,且成本低,易于实现,是确保FPGA安全性和保密性的一种方法,在金融等关系到国家利益的场合具有重大实用价值。