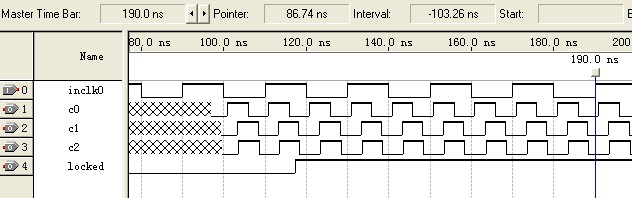

我用q2的core做了个锁相环,输入时钟50兆,输出三路皆为100兆的时钟,相移参数我都设成了10ns,然而仿真出来的图却有一路与另外两路时钟相位不一致,如下图所示,请问这是为什么呢?

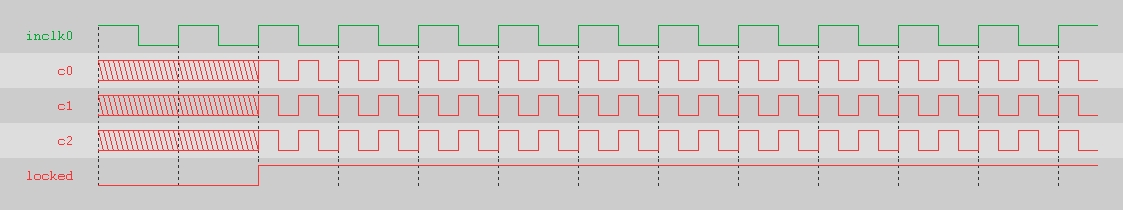

(生成pll时我选择了生成一个仿真图文件,这个图的输出关系却是正确的,如下图)

| 有奖活动 | |

|---|---|

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

| 送您一块开发板,2025年“我要开发板活动”又开始了! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| 在FireBeetle2ESP32-C5上实现温湿度检测和显示被打赏¥20元 | |

| 在FireBeetle2ESP32-C5上实现光照强度检测及显示被打赏¥21元 | |

| 以FireBeetle2ESP32-C5实现数据识读播报被打赏¥19元 | |

| 【STM32F103ZET6】14:实测STM32F1的串口输出任务的挂起与恢复功能被打赏¥27元 | |

| Chaos-nano在压力容器监控系统中的项目应用被打赏¥23元 | |

| 基于FireBeetle2ESP32-C5的WS2812B彩色灯带控制被打赏¥21元 | |

| SWM221CBT7显示开发板驱动TFT显示屏被打赏¥19元 | |

| SWM221CBT7显示开发板驱动OLED屏显示被打赏¥19元 | |

| SWM221CBT7显示开发板及其使用被打赏¥20元 | |

| 揭秘Chaos-nano:ArduinoProMini轻量级操作系统开发框架深度解析与实战应用被打赏¥19元 | |