【2012-09-22】报名申请FPGA开发板DIY。选择第一种方案:申请核心板和外围板PCB,自己购买元器件焊接。

【2012-09-23】下载FPGA开发板DIY活动准备工作里面的部分资料。

【2012-09-25】审核通过。对收到的材料电子报价进行分类,部分买不到的材料就在淘宝上购买。

【2012-09-29】收到PCB板。

【2012-10-12】采购失败:零件杂而且少结果不卖。

【2012-10-22】准备USB-Blaster,继续采购。

【2012-10-27】根据汇总情况,分配材料采购数量。

【2012-10-28】准备好了USB-Blaster,材料成功采购了90%预计31日或次月初收到。剩下的材料当地购买。

【2012-10-29】早上购买到材料,开始焊接。

【2012-10-30】下载工具软件。

【2012-10-31】继续下载软件,今天包裹收到了继续焊接。

【2012-11-01】安装软件,熟悉一下软件。

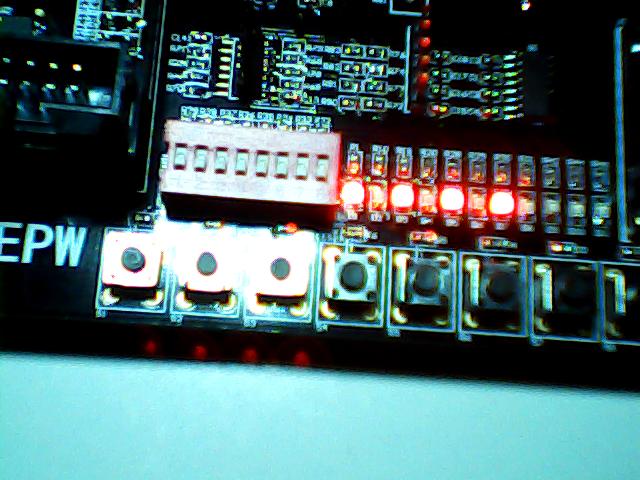

【2012-11-02】能测试到芯片(测不到实际的完整型号)。

【2012-11-04】开始写LED代码工程。

herer进程帖

关键词: herer 进程

FPGA 入门的第一个实验终于完成了 ~o(^_^)o~

实验文件如下:

LED实验一:LED001.rar静态

module LED001 (led);

output [7:0] led;

assign led =8'b10101010;

endmodule

LED实验二:LED002.rar闪烁

module LED001 ( sys_clk,

sys_rstn,

led

);

input sys_clk;

input sys_rstn;

output [7:0] led;

reg [7:0] led;

reg [24:0] delay_cnt;

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

delay_cnt<=25'd0;

else

begin

delay_cnt<=delay_cnt+1'd1;

if(delay_cnt==25'd24999999)

begin

delay_cnt<=25'd0;

led<=~led;

end

end

end

endmodule

LED实验二课后作业:LED002_1.rar

LED实验二:LED003.rar流水灯

module LED001 ( sys_clk,

sys_rstn,

led

);

input sys_clk;

input sys_rstn;

output [7:0] led;

reg [7:0] led;

reg [24:0] delay_cnt;

always@(posedge sys_clk or negedge sys_rstn)

begin

if(!sys_rstn)

begin

delay_cnt<=25'd0;

led =8'b11111111;

end

else

begin

delay_cnt<=delay_cnt+1'd1;

if(delay_cnt==25'd24999999)

begin

delay_cnt<=25'd0;

led<=led<<1;

end

end

end

endmodule

LED实验二课后作业:LED003_1.rar

LED实验二:LED004.rar跑马灯

led<={led[6:0],led[7]};

LED实验二课后作业:LED004_1.rar

回复

| 有奖活动 | |

|---|---|

| 【有奖活动】分享技术经验,兑换京东卡 | |

| 话不多说,快进群! | |

| 请大声喊出:我要开发板! | |

| 【有奖活动】EEPW网站征稿正在进行时,欢迎踊跃投稿啦 | |

| 奖!发布技术笔记,技术评测贴换取您心仪的礼品 | |

| 打赏了!打赏了!打赏了! | |

| 打赏帖 | |

|---|---|

| 与电子爱好者谈读图四被打赏50分 | |

| 与电子爱好者谈读图二被打赏50分 | |

| 【FRDM-MCXN947评测】Core1适配运行FreeRtos被打赏50分 | |

| 【FRDM-MCXN947评测】双核调试被打赏50分 | |

| 【CPKCORRA8D1B评测】---移植CoreMark被打赏50分 | |

| 【CPKCORRA8D1B评测】---打开硬件定时器被打赏50分 | |

| 【FRDM-MCXA156评测】4、CAN loopback模式测试被打赏50分 | |

| 【CPKcorRA8D1评测】--搭建初始环境被打赏50分 | |

| 【FRDM-MCXA156评测】3、使用FlexIO模拟UART被打赏50分 | |

| 【FRDM-MCXA156评测】2、rt-thread MCXA156 BSP制作被打赏50分 | |