FlexIO是MCXA156的外设模块。它具有高度可配置性,能够模拟各种通信协议,如UART、I2C、SPI、I2S和LIN,以及其它一些通讯协议,FlexIO作为微控制器的一个独立外设模块,并不能替代任何通信外设。FlexIO 的主要特点是可以根据用户的需求来直接构建自己的外设。

本文描述使用 FlexIO模拟UART。

本例程位于:SDK_2_16_100_FRDM-MCXA156\boards\frdmmcxa156\driver_examples\flexio\uart\polling_transfer

一、FlexIO

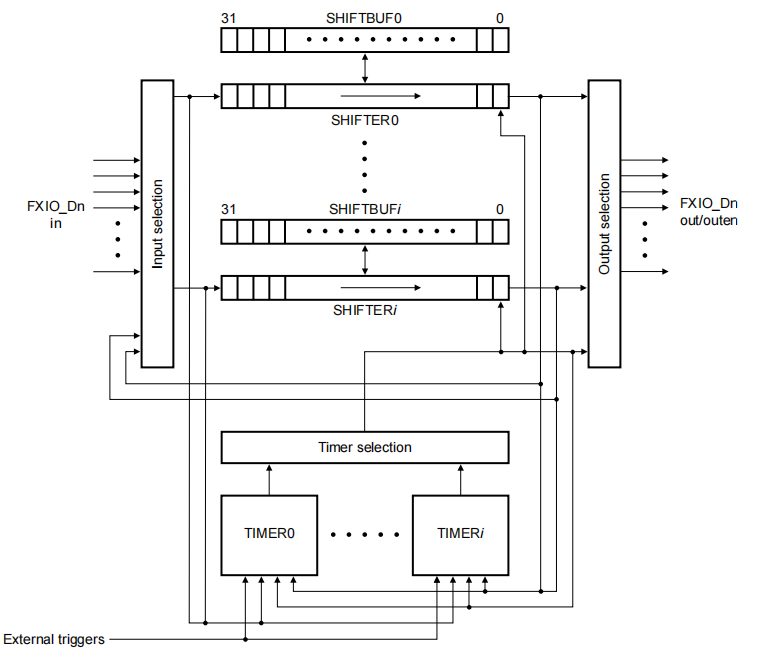

FlexIO 模块具有以下主要硬件资源:

移位器、定时器 引脚

The following diagram provides a high-level overview of the FLEXIO timer and shifter configuration. FLEXIO uses shifters, timers, and external triggers to shift data into or out of FLEXIO. As shown in the block diagram, timers control the timing of this data shift. You can configure the timers to use generic timer functions, external triggers, or various other conditions to determine the control.

二、FlexIO模拟UART

为实现UART 应用 需要的资源:

TX发送需要资源:一个定时器0、一个移位器0、一个引脚FlexIO_D0

移位器 0 作用于 UART的TXD,即 FlexIO_D0 脚。定时器 0 被 UART 用来对移位器 0 的控制。

RX接收需要资源:一个定时器1、一个移位 器1、一个引脚FlexIO_D1

移位器 1 作用于UART的RXD,即引脚 FlexIO_D1定时器 1 被 UART 用来作为对移位器 1 的控制

模拟RX接收

三、程序实现

1、pin初始化

PORT0_16 (pin 83) is configured as FLEXIO0_D0

PORT0_17 (pin 84) is configured as FLEXIO0_D1

void BOARD_InitPins(void)

{

/* PORT0: Peripheral clock is enabled */

CLOCK_EnableClock(kCLOCK_GatePORT0);

/* FLEXIO0 peripheral is released from reset */

RESET_ReleasePeripheralReset(kFLEXIO0_RST_SHIFT_RSTn);

/* PORT0 peripheral is released from reset */

RESET_ReleasePeripheralReset(kPORT0_RST_SHIFT_RSTn);

/* LPUART0 peripheral is released from reset */

RESET_ReleasePeripheralReset(kLPUART0_RST_SHIFT_RSTn);

const port_pin_config_t port0_16_pin83_config = {

/* Internal pull-up resistor is enabled */

kPORT_PullUp,

/* Low internal pull resistor value is selected. */

kPORT_LowPullResistor,

/* Fast slew rate is configured */

kPORT_FastSlewRate,

/* Passive input filter is disabled */

kPORT_PassiveFilterDisable,

/* Open drain output is disabled */

kPORT_OpenDrainDisable,

/* Low drive strength is configured */

kPORT_LowDriveStrength,

/* Normal drive strength is configured */

kPORT_NormalDriveStrength,

/* Pin is configured as FLEXIO0_D0 */

kPORT_MuxAlt6,

/* Digital input enabled */

kPORT_InputBufferEnable,

/* Digital input is not inverted */

kPORT_InputNormal,

/* Pin Control Register fields [15:0] are not locked */

kPORT_UnlockRegister};

/* PORT0_16 (pin 83) is configured as FLEXIO0_D0 */

PORT_SetPinConfig(PORT0, 16U, &port0_16_pin83_config);

const port_pin_config_t port0_17_pin84_config = {

/* Internal pull-up resistor is enabled */

kPORT_PullUp,

/* Low internal pull resistor value is selected. */

kPORT_LowPullResistor,

/* Fast slew rate is configured */

kPORT_FastSlewRate,

/* Passive input filter is disabled */

kPORT_PassiveFilterDisable,

/* Open drain output is disabled */

kPORT_OpenDrainDisable,

/* Low drive strength is configured */

kPORT_LowDriveStrength,

/* Normal drive strength is configured */

kPORT_NormalDriveStrength,

/* Pin is configured as FLEXIO0_D1 */

kPORT_MuxAlt6,

/* Digital input enabled */

kPORT_InputBufferEnable,

/* Digital input is not inverted */

kPORT_InputNormal,

/* Pin Control Register fields [15:0] are not locked */

kPORT_UnlockRegister};

/* PORT0_17 (pin 84) is configured as FLEXIO0_D1 */

PORT_SetPinConfig(PORT0, 17U, &port0_17_pin84_config);2、FLEXIO_UART初始化

#define BOARD_FLEXIO_BASE FLEXIO0 #define FLEXIO_UART_TX_PIN 0U //FLEXIO0_D0 PORT0_16 #define FLEXIO_UART_RX_PIN 1U //FLEXIO0_D1 PORT0_17 FLEXIO_UART_GetDefaultConfig(&config); config.baudRate_Bps = BOARD_DEBUG_UART_BAUDRATE; //115200 config.enableUart = true; uartDev.flexioBase = BOARD_FLEXIO_BASE; uartDev.TxPinIndex = FLEXIO_UART_TX_PIN; uartDev.RxPinIndex = FLEXIO_UART_RX_PIN; uartDev.shifterIndex[0] = 0U; //移位器0 uartDev.shifterIndex[1] = 1U; //移位器1 uartDev.timerIndex[0] = 0U; //定时器0 uartDev.timerIndex[1] = 1U; //定时器1 result = FLEXIO_UART_Init(&uartDev, &config, FLEXIO_CLOCK_FREQUENCY); //初始化FLEXIO_UART

FLEXIO_UART_Init实现了很多功能,使得FLEXIO_UART初始化非常简洁。

3、发送接收函数

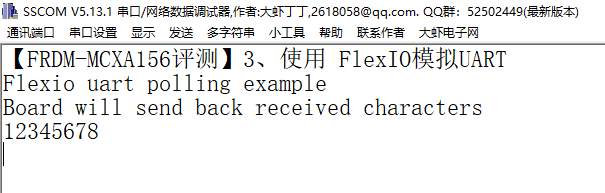

FLEXIO_UART_WriteBlocking(&uartDev,"【FRDM-MCXA156评测】3、使用 FlexIO模拟UART\r\n",44);

FLEXIO_UART_WriteBlocking(&uartDev, txbuff, sizeof(txbuff) - 1);

while (1)

{

FLEXIO_UART_ReadBlocking(&uartDev, &ch, 1);

FLEXIO_UART_WriteBlocking(&uartDev, &ch, 1);

}四、效果

我要赚赏金

我要赚赏金