学习了,楼主速度真快呀~~

13、关于LCD时钟只显示一行的讨论(已解决)

问题就是,LCD的字符是常量的时候,显示正常,但是如果字符数据时变量,第二行就没法显示,

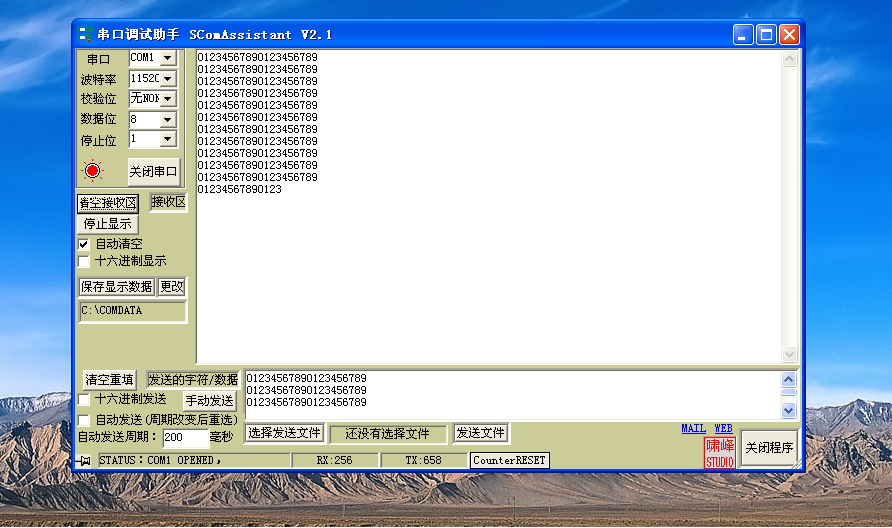

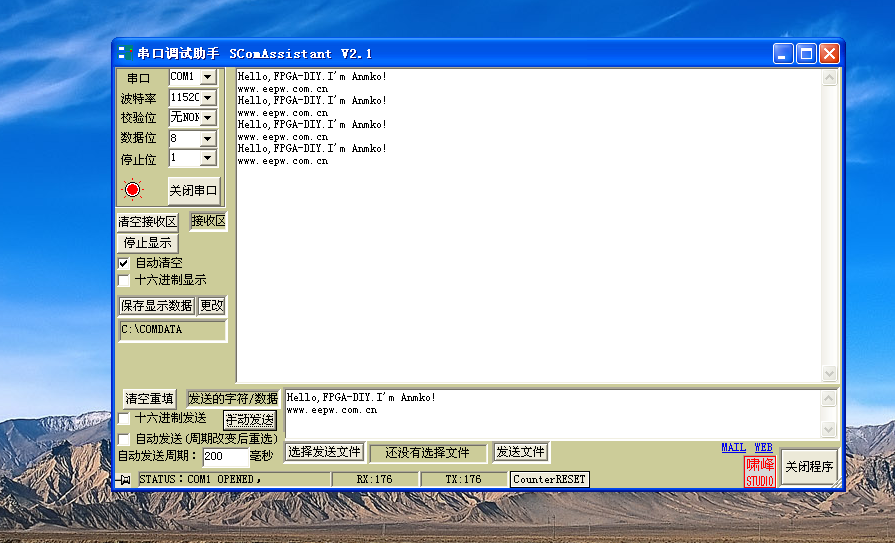

这个是常量的 这个是变量的

顶层文件:

module lcd_timer(clk,rst_n,key_in,ledout,lcd_en,lcd_rs,lcd_rw,lcd_data);

input clk;

input rst_n;

input [5:0] key_in;

output ledout;

output lcd_en;

output lcd_rs;

output lcd_rw;

output [7:0] lcd_data;

wire clk_en;

Div_50M CLK_DIV

(

.clk(clk),

.rst(rst_n),

.clk_out(clk_en)

);

wire [3:0] S_H;

wire [3:0] S_L;

wire SecCout;

counter60 Sec

(

.en(clk_en),

.clk(clk),

.rst(rst_n),

.key1(key_in[0]),

.key2(key_in[1]),

.cout(SecCout),

.HighOut(S_H),

.LowOut(S_L)

);

wire [3:0] M_H;

wire [3:0] M_L;

wire MinCout;

counter60 Min

(

.en(SecCout),

.clk(clk),

.rst(rst_n),

.key1(key_in[2]),

.key2(key_in[3]),

.cout(MinCout),

.HighOut(M_H),

.LowOut(M_L)

);

wire [3:0] H_H;

wire [3:0] H_L;

counter24 Hour

(

.en(MinCout),

.clk(clk),

.rst(rst_n),

.key1(key_in[4]),

.key2(key_in[5]),

.cout(ledout),

.HighOut(H_H),

.LowOut(H_L)

);

lcd1602_driver DISP

(

.clk(clk),

.rst_n(rst_n),

.lcd_en(lcd_en), // lcd enable

.lcd_rs(lcd_rs), // record,statement

.lcd_rw(lcd_rw),

.lcd_data(lcd_data),

.disp_1th(S_L),

.disp_2th(S_H),

.disp_3th(M_L),

.disp_4th(M_H),

.disp_5th(H_L),

.disp_6th(H_H)

);

endmodule

50分频

/*************************************************

fc = 50MHz 50*10^6

fo = fc*K/(2^32)

K = fo*(2^32)/fc

= fo*(2^32)/(50*10^6)

**************************************************/

module Div_50M(clk,rst,clk_out);

input clk; //50MHz

input rst; //clock reset

output reg clk_out;

//--------------------------------------

reg [31:0] cnt;

always@(posedge clk or negedge rst)

begin

if(!rst)

cnt <= 32'd0;

else

cnt <= cnt + 32'd91;

end

//--------------------------------------

always@(posedge clk or negedge rst)

begin

if(!rst)

clk_out <= 1'b0;

else

begin

if(cnt < 32'h7FFF_FFFF)

clk_out <= 1'b0;

else

clk_out <= 1'b1;

end

end

endmodule

60计数器

module counter60(en,clk,rst,key1,key2,cout,HighOut,LowOut);

input en,clk,rst;

input key1,key2;

//input mode;

output reg cout;

output [3:0] HighOut;

output [3:0] LowOut;

reg [3:0] HighOut_r;

reg [3:0] LowOut_r;

reg[17:0] cnt;

// reg[3:0] cnt;

always @(posedge clk or negedge rst)

begin

if (!rst)

cnt <= 18'd0;

else

cnt <= cnt + 1'b1;

end

wire sample_pulse = cnt == 18'h3ffff;

reg add1,add2,cnt_en;

always @(posedge clk or negedge rst)

begin

if (!rst)

begin

add1 <= 1'b1;

add2 <= 1'b1;

end

else

begin

cnt_en <= en;

if(sample_pulse)

begin

add1 <= key1;

add2 <= key2;

end

end

end

reg add1_r,add2_r,cnt_en_r;

always @(posedge clk ) begin

add1_r <= add1;

add2_r <= add2;

cnt_en_r <= cnt_en;

end

wire add1_ctrl = add1_r & (!add1);

wire add2_ctrl = add2_r & (!add2);

wire cnt_ctrl = (!cnt_en_r) & cnt_en;

always @(posedge clk or negedge rst) begin

if(!rst)

begin

HighOut_r <= 4'b0;

LowOut_r <= 4'b0;

end

else if(add1_ctrl)

begin

HighOut_r <= HighOut_r + 1'b1;

if(HighOut_r >= 4'b0101 ) HighOut_r <= 4'b0;

end

else if(add2_ctrl)

begin

LowOut_r <= LowOut_r + 1'b1;

if(LowOut_r >= 4'b1001 ) LowOut_r <= 4'b0;

end

else if(cnt_ctrl)

begin

if((HighOut_r>=4'b0101)&&(LowOut_r>=4'b1001))

begin

HighOut_r <= 4'b0;

LowOut_r <= 4'b0;

cout = 1;

end

else

begin

cout = 0;

LowOut_r <= LowOut_r + 1'b1;

if(LowOut_r >= 4'b1001)

begin

HighOut_r <= HighOut_r + 1'b1;

LowOut_r <= 4'b0;

end

end

end

end

assign HighOut = HighOut_r;

assign LowOut = LowOut_r;

endmodule

24计数器

module counter24(en,clk,rst,key1,key2,cout,HighOut,LowOut);

input en,clk,rst;

input key1,key2;

output reg cout;

output [3:0] HighOut;

output [3:0] LowOut;

reg [3:0] HighOut_r;

reg [3:0] LowOut_r;

reg[4:0] counter;

reg[17:0] cnt;

always @(posedge clk or negedge rst)

begin

if (!rst)

cnt <= 18'd0;

else

cnt <= cnt + 1'b1;

end

wire sample_pulse = cnt == 18'h3ffff;

reg add1,add2,cnt_en;

always @(posedge clk or negedge rst)

begin

if (!rst)

begin

add1 <= 1'b1;

add2 <= 1'b1;

end

else

begin

cnt_en <= en;

if(sample_pulse)

begin

add1 <= key1;

add2 <= key2;

end

end

end

reg add1_r,add2_r,cnt_en_r;

always @(posedge clk ) begin

add1_r <= add1;

add2_r <= add2;

cnt_en_r <= cnt_en;

end

wire add1_ctrl = add1_r & (!add1);

wire add2_ctrl = add2_r & (!add2);

wire cnt_ctrl = (!cnt_en_r) & cnt_en;

always @(posedge clk or negedge rst) begin

if(!rst)

counter <= 5'b0;

else if(add1_ctrl)

begin

counter <= counter + 1'b1;

if(counter == 5'd23)

counter <= 5'b0;

end

else if(add2_ctrl)

begin

counter <= counter - 1'b1;

if(counter == 5'b0)

counter <= 5'd23;

end

else if(cnt_ctrl)

if(counter == 5'd23)

begin

counter <= 5'b0;

cout <= 1;

end

else

begin

cout <= 0;

counter <= counter + 1'b1;

end

end

always @(posedge clk) begin

HighOut_r <= counter/10;

LowOut_r <= counter%10;

end

assign HighOut = HighOut_r;

assign LowOut = LowOut_r;

endmodule

lcd1602显示

/*************************************************

* Module Name : lcd1602_driver

* Engineer : Anmko

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 12.0

* Create Date : 2012-9-3

* Revision : v1.0

* Description :

**************************************************/

module lcd1602_driver

(

input clk,

input rst_n,

input [3:0]disp_1th,

input [3:0]disp_2th,

input [3:0]disp_3th,

input [3:0]disp_4th,

input [3:0]disp_5th,

input [3:0]disp_6th,

output lcd_en, // lcd enable

output reg lcd_rs, // record,statement

output reg lcd_rw,

output reg [7:0] lcd_data

);

parameter [127:0] line_rom1 = "Hello,I' Anmko!";

parameter [127:0] line_rom2 = "EEPW---FPGA DIY!";

reg [7:0] Sec_H;

reg [7:0] Sec_L;

reg [7:0] Min_H;

reg [7:0] Min_L;

reg [7:0] Hour_H;

reg [7:0] Hour_L;

//--------------------------------------

reg [15:0] cnt;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

assign lcd_en = cnt[15]; //lcd enable,keep same time; >1000ns

wire cmd_flag = (cnt == 16'h7FFF) ? 1'b1 : 1'b0; //when lcd_en is steady,write a cmd

// Gray code : 40 states

parameter IDLE = 8'h00; // IDLE

// lcd init

parameter CLEAR = 8'h01;

parameter SETFUNCTION = 8'h02;

parameter SWITCHMODE = 8'h03;

parameter SETMODE = 8'h04;

parameter SHIFT = 8'h05;

// parameter SETCGRAM = 8'h40;

// parameter SETDDRAM1 = 8'h81;

// parameter SETDDRAM2 = 8'h82;

// display 1th line

parameter ROW1_ADDR = 8'h09;

parameter ROW1_0 = 8'h0A;

parameter ROW1_1 = 8'h0B;

parameter ROW1_2 = 8'h0C;

parameter ROW1_3 = 8'h0D;

parameter ROW1_4 = 8'h0E;

parameter ROW1_5 = 8'h0F;

parameter ROW1_6 = 8'h10;

parameter ROW1_7 = 8'h11;

parameter ROW1_8 = 8'h12;

parameter ROW1_9 = 8'h13;

parameter ROW1_A = 8'h14;

parameter ROW1_B = 8'h15;

parameter ROW1_C = 8'h16;

parameter ROW1_D = 8'h17;

parameter ROW1_E = 8'h18;

parameter ROW1_F = 8'h19;

// display 2th line

parameter ROW2_ADDR = 8'h1A;

parameter ROW2_0 = 8'h1B;

parameter ROW2_1 = 8'h1C;

parameter ROW2_2 = 8'h1D;

parameter ROW2_3 = 8'h1E;

parameter ROW2_4 = 8'h1F;

parameter ROW2_5 = 8'h20;

parameter ROW2_6 = 8'h21;

parameter ROW2_7 = 8'h22;

parameter ROW2_8 = 8'h23;

parameter ROW2_9 = 8'h24;

parameter ROW2_A = 8'h25;

parameter ROW2_B = 8'h26;

parameter ROW2_C = 8'h27;

parameter ROW2_D = 8'h28;

parameter ROW2_E = 8'h29;

parameter ROW2_F = 8'h2A;

always @ (cmd_flag )

begin

Sec_L = disp_1th;

Sec_L = Sec_L+8'd48;

Sec_H = disp_2th;

Sec_H = Sec_H+8'd48;

Min_L = disp_3th;

Min_L = Min_L+8'd48;

Min_H = disp_4th;

Min_H = Min_H+8'd48;

Hour_L = disp_5th;

Hour_L = Hour_L+8'd48;

Hour_H = disp_6th;

Hour_H = Hour_H+8'd48;

end

//---------------------------------------

reg [7:0] state;

//---------------------------------------

// FSM: ״̬��

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

lcd_rs <= 0;

lcd_data <= 8'hXX;

end

else if(cmd_flag)

begin

// write statement

case(state)

IDLE :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'hxx;

state <= CLEAR;

end

//lcd init

CLEAR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b0000_0001;

state <= SETFUNCTION;

end

SETFUNCTION :begin

lcd_rs <= 0; lcd_rw <= 0; //3C

lcd_data <= 8'b0011_1100;

state <= SWITCHMODE;

end

SWITCHMODE :begin

lcd_rs <= 0; lcd_rw <= 0; //08

lcd_data <= 8'b0000_1000;

state <= SETMODE;

end

SETMODE :begin

lcd_rs <= 0; lcd_rw <= 0; //06

lcd_data <= 8'b0000_0110;

state <= SHIFT;

end

SHIFT :begin

lcd_rs <= 0; lcd_rw <= 0; //0c

lcd_data <= 8'b0000_1100;

state <= ROW1_ADDR;

end

ROW1_ADDR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b1000_0000;

state <= ROW1_0;

end

ROW1_0 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Hour_H[7:0];//line_rom1[127:120];

state <= ROW1_1;

end

ROW1_1 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Hour_L[7:0];//line_rom1[119:112];

state <= ROW1_2;

end

ROW1_2 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= ":";//line_rom1[111:104];

state <= ROW1_3;

end

ROW1_3 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Min_H[7:0];//line_rom1[103:96];

state <= ROW1_4;

end

ROW1_4 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Min_L[7:0];//line_rom1[95:88];

state <= ROW1_5;

end

ROW1_5 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= ":";//line_rom1[87:80];

state <= ROW1_6;

end

ROW1_6 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Sec_H[7:0];//line_rom1[79:72];

state <= ROW1_7;

end

ROW1_7 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Sec_L[7:0];//line_rom1[71:64];

state <= ROW1_8;

end

ROW1_8 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[63:56];

state <= ROW1_9;

end

ROW1_9 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[55:48];

state <= ROW1_A;

end

ROW1_A :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[47:40];

state <= ROW1_B;

end

ROW1_B :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[39:32];

state <= ROW1_C;

end

ROW1_C :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[31:24];

state <= ROW1_D;

end

ROW1_D :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[23:16];

state <= ROW1_E;

end

ROW1_E :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[15:8];

state <= ROW1_F;

end

ROW1_F :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[7:0];

state <= ROW2_ADDR;

end

ROW2_ADDR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b1100_0000;

state <= ROW2_0;

end

ROW2_0 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[127:120];

state <= ROW2_1;

end

ROW2_1 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[119:112];

state <= ROW2_2;

end

ROW2_2 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[111:104];

state <= ROW2_3;

end

ROW2_3 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= Sec_L[7:0];//line_rom2[103:96];

state <= ROW2_4;

end

ROW2_4 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[95:88];

state <= ROW2_5;

end

ROW2_5 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[87:80];

state <= ROW2_6;

end

ROW2_6 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[79:72];

state <= ROW2_7;

end

ROW2_7 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[71:64];

state <= ROW2_8;

end

ROW2_8 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[63:56];

state <= ROW2_9;

end

ROW2_9 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[55:48];

state <= ROW2_A;

end

ROW2_A :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[47:40];

state <= ROW2_B;

end

ROW2_B :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[39:32];

state <= ROW2_C;

end

ROW2_C :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[31:24];

state <= ROW2_D;

end

ROW2_D :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[23:16];

state <= ROW2_E;

end

ROW2_E :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[15:8];

state <= ROW2_F;

end

ROW2_F :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[7:0];

state <= ROW1_ADDR;

end

default : state <= IDLE;

endcase

end

end

endmodule

问题已经解决。把LCD1602驱动改了一下;红色的为更改部分

/*************************************************

* Module Name : lcd1602_driver

* Engineer : Anmko

* Target Device : EP2C8Q208C8

* Tool versions : Quartus II 12.0

* Create Date : 2012-9-3

* Revision : v1.0

* Description :

**************************************************/

module lcd1602_driver

(

input clk,

input rst_n,

input [3:0]disp_1th,

input [3:0]disp_2th,

input [3:0]disp_3th,

input [3:0]disp_4th,

input [3:0]disp_5th,

input [3:0]disp_6th,

output lcd_en, // lcd enable

output reg lcd_rs, // record,statement

output reg lcd_rw,

output reg [7:0] lcd_data

);

reg [127:0] line_rom1 = "A Clock 00:00:00";

reg [127:0] line_rom2 = "EEPW---FPGA DIY!";

//--------------------------------------

reg [15:0] cnt;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

assign lcd_en = cnt[15]; //lcd enable,keep same time; >1000ns

wire cmd_flag = (cnt == 16'h7FFF) ? 1'b1 : 1'b0; //when lcd_en is steady,write a cmd

always @ (cmd_flag )

begin

line_rom1[7:0] <= 48 + disp_1th;

line_rom1[15:8] <= 48 + disp_2th;

line_rom1[31:24] <= 48 + disp_3th;

line_rom1[39:32] <= 48 + disp_4th;

line_rom1[55:48] <= 48 + disp_5th;

line_rom1[63:56] <= 48 + disp_6th;

end

// Gray code : 40 states

parameter IDLE = 8'h00; // IDLE

// lcd init

parameter CLEAR = 8'h01; //锟斤拷锟斤拷

parameter SETFUNCTION = 8'h02;

parameter SWITCHMODE = 8'h03;

parameter SETMODE = 8'h04;

parameter SHIFT = 8'h05;

// parameter SETCGRAM = 8'h40; //锟斤拷锟斤拷CGRAM

// parameter SETDDRAM1 = 8'h81; //锟斤拷锟斤拷DDRAM

// parameter SETDDRAM2 = 8'h82; //锟斤拷锟斤拷DDRAM

// display 1th line

parameter ROW1_ADDR = 8'h09;

parameter ROW1_0 = 8'h0A;

parameter ROW1_1 = 8'h0B;

parameter ROW1_2 = 8'h0C;

parameter ROW1_3 = 8'h0D;

parameter ROW1_4 = 8'h0E;

parameter ROW1_5 = 8'h0F;

parameter ROW1_6 = 8'h10;

parameter ROW1_7 = 8'h11;

parameter ROW1_8 = 8'h12;

parameter ROW1_9 = 8'h13;

parameter ROW1_A = 8'h14;

parameter ROW1_B = 8'h15;

parameter ROW1_C = 8'h16;

parameter ROW1_D = 8'h17;

parameter ROW1_E = 8'h18;

parameter ROW1_F = 8'h19;

// display 2th line

parameter ROW2_ADDR = 8'h1A;

parameter ROW2_0 = 8'h1B;

parameter ROW2_1 = 8'h1C;

parameter ROW2_2 = 8'h1D;

parameter ROW2_3 = 8'h1E;

parameter ROW2_4 = 8'h1F;

parameter ROW2_5 = 8'h20;

parameter ROW2_6 = 8'h21;

parameter ROW2_7 = 8'h22;

parameter ROW2_8 = 8'h23;

parameter ROW2_9 = 8'h24;

parameter ROW2_A = 8'h25;

parameter ROW2_B = 8'h26;

parameter ROW2_C = 8'h27;

parameter ROW2_D = 8'h28;

parameter ROW2_E = 8'h29;

parameter ROW2_F = 8'h2A;

//---------------------------------------

reg [7:0] state;

//---------------------------------------

// FSM: 状态锟斤拷

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

lcd_rs <= 0;

lcd_data <= 8'hXX;

end

else if(cmd_flag)

begin

// write statement

case(state)

IDLE :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'hxx;

state <= CLEAR;

end

//lcd init

CLEAR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b0000_0001;

state <= SETFUNCTION;

end

SETFUNCTION :begin

lcd_rs <= 0; lcd_rw <= 0; //3C

lcd_data <= 8'b0011_1100;

state <= SWITCHMODE;

end

SWITCHMODE :begin

lcd_rs <= 0; lcd_rw <= 0; //08

lcd_data <= 8'b0000_1000;

state <= SETMODE;

end

SETMODE :begin

lcd_rs <= 0; lcd_rw <= 0; //06

lcd_data <= 8'b0000_0110;

state <= SHIFT;

end

SHIFT :begin

lcd_rs <= 0; lcd_rw <= 0; //0c

lcd_data <= 8'b0000_1100;

state <= ROW1_ADDR;

end

ROW1_ADDR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b1000_0000;

state <= ROW1_0;

end

ROW1_0 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[127:120];//Hour_H[7:0];//line_rom1[127:120];

state <= ROW1_1;

end

ROW1_1 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[119:112];//Hour_L[7:0];//line_rom1[119:112];

state <= ROW1_2;

end

ROW1_2 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[111:104];//":";//line_rom1[111:104];

state <= ROW1_3;

end

ROW1_3 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[103:96];//Min_H[7:0];//line_rom1[103:96];

state <= ROW1_4;

end

ROW1_4 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[95:88];//Min_L[7:0];//line_rom1[95:88];

state <= ROW1_5;

end

ROW1_5 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[87:80];//":";//line_rom1[87:80];

state <= ROW1_6;

end

ROW1_6 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[79:72];//Sec_H[7:0];//line_rom1[79:72];

state <= ROW1_7;

end

ROW1_7 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[71:64];//Sec_L[7:0];//line_rom1[71:64];

state <= ROW1_8;

end

ROW1_8 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[63:56];

state <= ROW1_9;

end

ROW1_9 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[55:48];

state <= ROW1_A;

end

ROW1_A :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[47:40];

state <= ROW1_B;

end

ROW1_B :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[39:32];

state <= ROW1_C;

end

ROW1_C :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[31:24];

state <= ROW1_D;

end

ROW1_D :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[23:16];

state <= ROW1_E;

end

ROW1_E :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[15:8];

state <= ROW1_F;

end

ROW1_F :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom1[7:0];

state <= ROW2_ADDR;

end

ROW2_ADDR :begin

lcd_rs <= 0; lcd_rw <= 0;

lcd_data <= 8'b1100_0000;

state <= ROW2_0;

end

ROW2_0 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[127:120];

state <= ROW2_1;

end

ROW2_1 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[119:112];

state <= ROW2_2;

end

ROW2_2 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[111:104];

state <= ROW2_3;

end

ROW2_3 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[103:96];

state <= ROW2_4;

end

ROW2_4 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[95:88];

state <= ROW2_5;

end

ROW2_5 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[87:80];

state <= ROW2_6;

end

ROW2_6 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[79:72];

state <= ROW2_7;

end

ROW2_7 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[71:64];

state <= ROW2_8;

end

ROW2_8 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[63:56];

state <= ROW2_9;

end

ROW2_9 :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[55:48];

state <= ROW2_A;

end

ROW2_A :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[47:40];

state <= ROW2_B;

end

ROW2_B :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[39:32];

state <= ROW2_C;

end

ROW2_C :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[31:24];

state <= ROW2_D;

end

ROW2_D :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[23:16];

state <= ROW2_E;

end

ROW2_E :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[15:8];

state <= ROW2_F;

end

ROW2_F :begin

lcd_rs <= 1; lcd_rw <= 0;

lcd_data <= line_rom2[7:0];

state <= ROW1_ADDR;

end

default : state <= IDLE;

endcase

end

end

endmodule

回复

| 有奖活动 | |

|---|---|

| 2026年“我要开发板活动”第三季,开始了! | |

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| PTC与NTC功能常规对比被打赏¥14元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于3pin锂电池接口的介绍/使用被打赏¥16元 | |

| 以启明云端ESP32P4开发板实现TF卡读写功能被打赏¥28元 | |

| 【分享开发笔记,赚取电动螺丝刀】树莓派5串口UART0配置被打赏¥25元 | |

| 【STM32F103ZET6】17:分享在Rtos项目中断管理的使用经验被打赏¥23元 | |

| 【STM32F103ZET6】16:分享在中断中恢复串口任务,遇到的问题被打赏¥31元 | |

| 在FireBeetle2ESP32-C5上实现温度大气压检测及显示被打赏¥21元 | |

| 【分享开发笔记,赚取电动螺丝刀】SAME51双串口收发配置被打赏¥27元 | |

| Chaos-nano操作系统在手持式VOC检测设备上的应用被打赏¥37元 | |

| 【分享开发笔记,赚取电动螺丝刀】关于在导入第三方库lib时,wchart类型冲突的原因及解决方案被打赏¥30元 | |