AT89S52——低功耗高性能CMOS 8位单片机,片内8k Bytes ISP(In-system

programmable)的可反复擦写1000次的FLASH只读程序存储器,器件采用ATMEL公司之高密度、非易失性存储技术制造,兼容标准 MCS-51指令系统及80C51引脚结构,片上Flash允许程序存储器在系统可编程,亦适于常规编程器。单芯片上,拥有8 位CPU及在系统可编程FLASH,使AT89S52为众多嵌入式控制应用系统提供高灵活、超有效之解决方案。

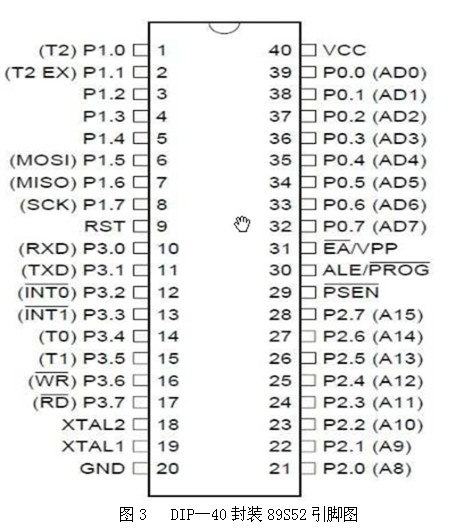

AT89S52之特点:40个引脚,8k Bytes Flash片内程序存储器,256 bytes

的随机存取数据存储器(RAM),32个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。

AT89C52——低电压高性能CMOS 8位单片机,片内8k bytes的可反复擦写的FLASH只读程序存储器及256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器及FLASH存储单元,功能强大之AT89C52单片机可为您提供许多较复杂系统控制之应用场合。

AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口,2个读写口线,AT89C52可按照常规方法进行编程,亦可在线编程。其将通用之微处理器及Flash存储器结合,特别是可反复擦写的FLASH存储器可有效降低开发成本。

AT89C52及AT89S52之别,在于C及S, C表示需用并行编程器下载(接线多且复杂),S表示可支持ISP下载,可在89S52系统板上面预留ISP下载接口,ISP下载线可方便地自制,一74HC373,若干电阻,连接电脑并口就可用软件将hex文件下载至89S52。相比较AT89C52及AT89S52 ,以方便计,选用AT89S52。

AT89S52功能:8k字节FLASH,256字节RAM,32位I/O口线,看门狗定时器,2 个数据指针,三个16 位定时器/计数器,一6向量2级中断结构,全双

工串行口,片内晶振及时钟电路。AT89S52可降至0Hz静态逻辑操作,支持2种软件可选节电模式。空闲模式下,CPU 停止工作,允许RAM、定时器/计数器、串口、中断继续工作。掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一中断或硬件复位为止。

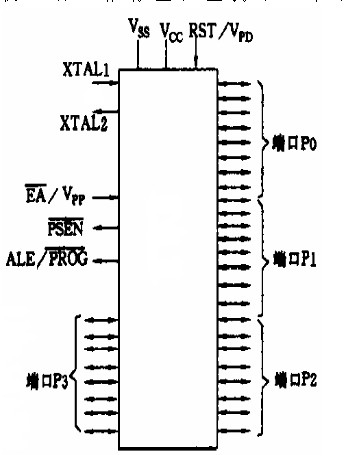

P0口——8位漏极开路之双向I/O口。作为输出口,每位能驱动8个TTL逻辑电平。对P0端口写“1”时,引脚用作高阻抗输入。访问外部程序和数据存储器时,P0口亦被作为低8位地址/数据复用。在这种模式下,P0不具有内部上拉电阻。在FLASH编程时,P0口亦用来接收指令字节;在程序校验时,输出指令字节。程序校验时,需外部上拉电阻。

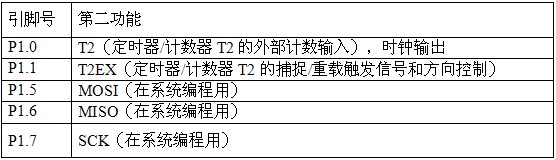

P1口——有内部上拉电阻的8位双向I/O 口,p1 输出缓冲器能驱动4 个 TTL 逻辑电平。对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可作输入口用。作为输入使用时,被外部拉低的引脚由于内部电阻的原因,将输出电流(IIL)。对P1 端口写“1”时,内部上拉电阻把端口拉高,此时可作输入口用。作输入用时,被外部拉低的引脚因内部电阻,将输出电流(IIL)。此外,P1.0及P1.2分别作定时器/计数器2之外部计数输入(P1.0/T2)及时器/计数器2之触发输入(P1.1/T2EX),详见表1所示。在flash编程及校验时,P1口接收低8位地址字节。 表1:

P2口——有内部上拉电阻的8 位双向I/O口,P2输出缓冲器能驱动4个TTL 逻辑电平。对P2 端口写“1”时,内部上拉电阻把端口拉高,此时可作输入口。作输入用时,被外部拉低的引脚因内部电阻,将输出电流(IIL)。 在访问外部程序存储器或用16位地址读取外部数据存储器(例如执行MOVX @DPTR) 时,P2口送出高八位地址。在这种应用中,P2口用很强的内部上拉发送1。在用8位地址(如MOVX @RI)访问外部数据存储器时,P2口输出P2锁存器之内容。在FLASH编程及校验时,P2口亦接收高8位地址字节及一些控制信号。

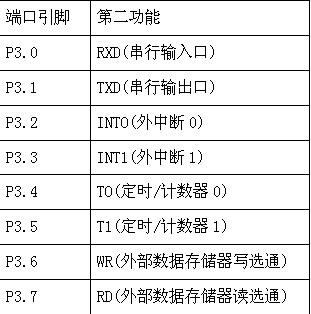

P3口——有内部上拉电阻的8位双向I/O口,p3输出缓冲器能驱动4个TTL 逻辑电平。对P3端口写“1”时,内部上拉电阻把端口拉高,此时可用作输入口。作输入用时,被外部拉低的引脚因内部电阻之原因,将输出电流(IIL)。P3口亦作为AT89S52特殊功能(第二功能)用,如表2所示。在FLASH编程及校验时,P3口亦接收些控制信号。此外,P3口亦接收些用于FLASH闪存编程及程序校验的控制信号。 表2

RST——复位输入。振荡器工作时,RST引脚有两个机器周期以上高电平将是单片机复位。

ALE/PROG——访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节。一般,ALE仍以时钟振荡频率的1/6输出固定之脉冲信号,故它可对外输出时钟或用于定时目的。需注意:每当访问外部数据存储器时将跳过一个ALE脉冲。对FLASH存储器编程期间,该引脚亦用于输入编程脉冲(PROG)。若必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位,可禁止ALE操作。该位置位后,只有一条MOVX及MOVC指令方能将ALE激活。此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE禁止位无效。

PSEN——程序储存允许(PSEN)输出是外部程序存储器之读选通信号,AT89S52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲,在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

EA/VPP——外部访问允许,要CPU仅访问外部程序存储器(地址为0000H-FFFFH),EA端须保持低电平(接地)。需注意:若加密位LB1被编程,复位时内部会锁存EA端状态。若EA端为高电平(接Vcc端),CPU则执行内部程序存储器之指令。

FLASH存储器编程时,该引脚加上+12V的编程允许电源Vpp,当然这须是该器件是使用12V编程电压Vpp。

XTAL1——振荡器反相放大器及内部时钟发生电路之输入端。

XTAL2——振荡器反相放大器之输出端。