简介:

ARM R/A 系列都存在PMU(Performance Monitoring Unit) ,该IP 可以用来监测CPU 的运行的性能参数,ARM M系列在ARMV8.1-M架构中引入了该扩展特性,瑞萨的 RA8 架构是M85 的IP CORE 对应于 ARMV8.1-M架构 已经集成了该功能,ARMV8M 文档中对该功能描述如下

The Performance Monitors Extension describes an optional non-invasive debug component that allows performance events to be identified and counted. An implementation of the Performance Monitors Extension is known as the Performance Monitoring Unit (PMU).

The Cortex®-M85 processor Data Watchpoint and Trace (DWT) implements the Performance Monitoring Unit (PMU). This enables software to get information about events that are taking place in the processor and can be used for performance analysis and system debug. The PMU supports eight 16-bit event counters and one 32-bit cycle counter. Each event counter can count one event from a list comprising both architectural and IMPLEMENTATION DEFINED events. For more information on PMU events, see 17.2 PMU events on page 264. The PMU also supports a chain function which allows the PMU to cascade two of the 16-bit counters into one 32-bit counter. Only odd event counters support the chain feature. PMU counters increment if the appropriate bit in PMU_CNTENSET register is set. The Arm®v8.1‑M architecture specifies that operation of the PMU counters and DWT profiling counters is mutually exclusive. The Cortex®-M85 processor uses this requirement to share the state used for the counters. The PMU cycle counter PMU_CCNTR is an alias of the DWT_CYCCNT register. All derived functions of the counter are available whenever either the DWT or the PMU enables the cycle counter. DWT_CTRL.NOCYCCNT is RAZ.

从上述features 可以看出PMU 的功能只要是可以监测CPU 运行的counter 及 一些CPU 运行的event 类如CPU指令执行数量、cache 访问事件等CPU 运行的性能参数。

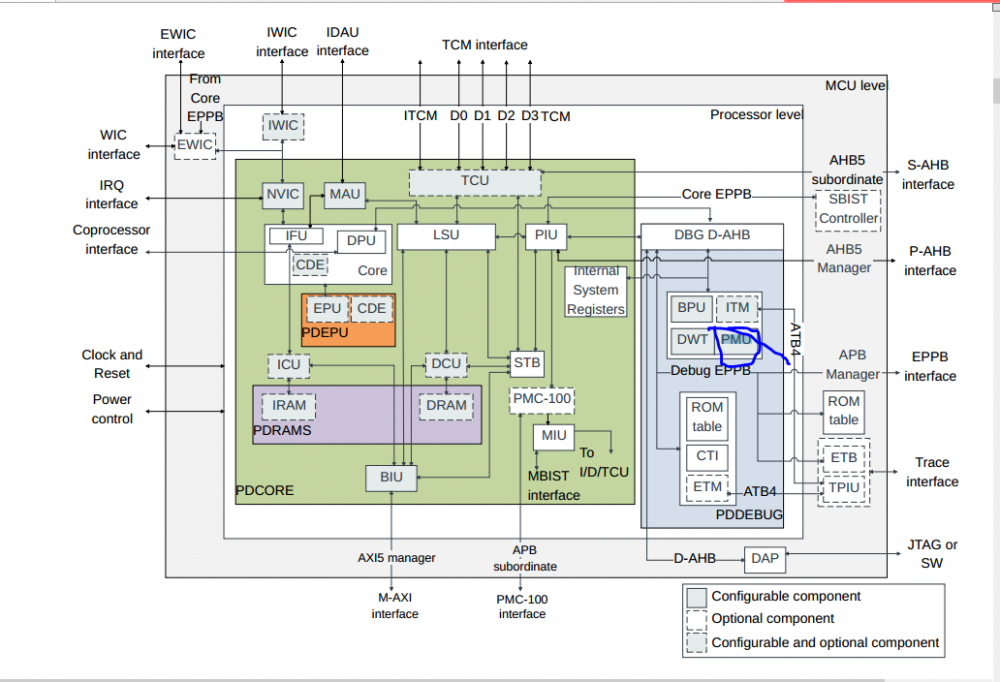

从M85 的框图可以看出,CPU 已经集成了PMU ,其属于PDDEBUG domain 的一部分。

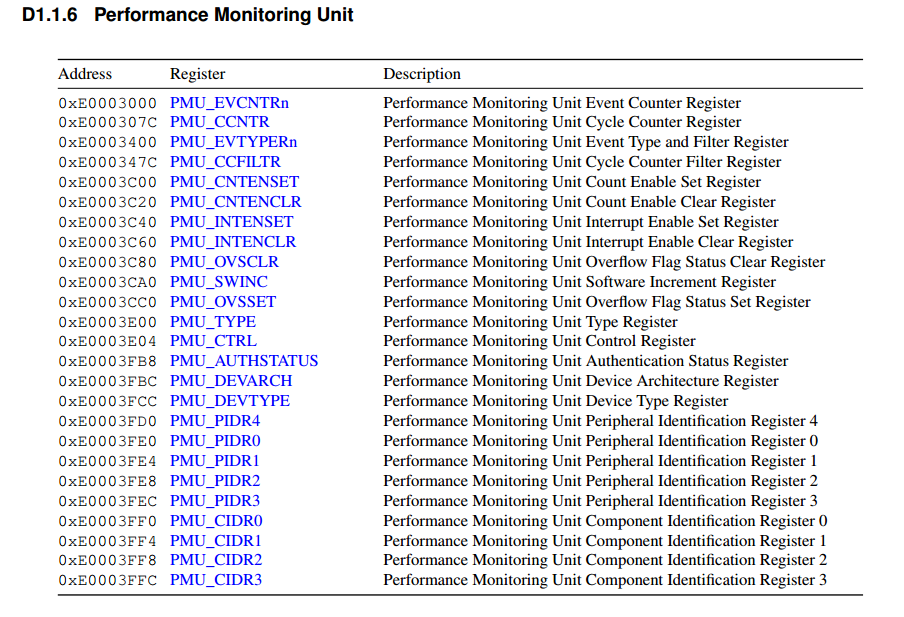

PMU 寄存器

PMU 模块对应寄存器列表如下

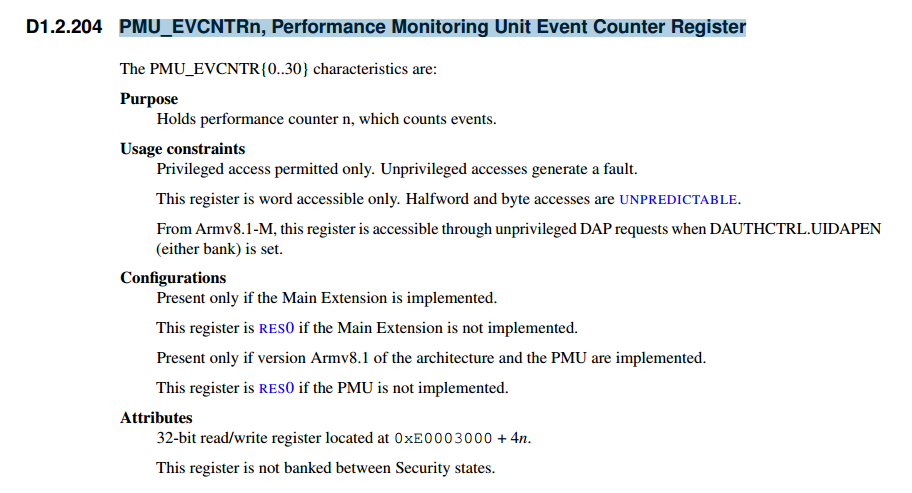

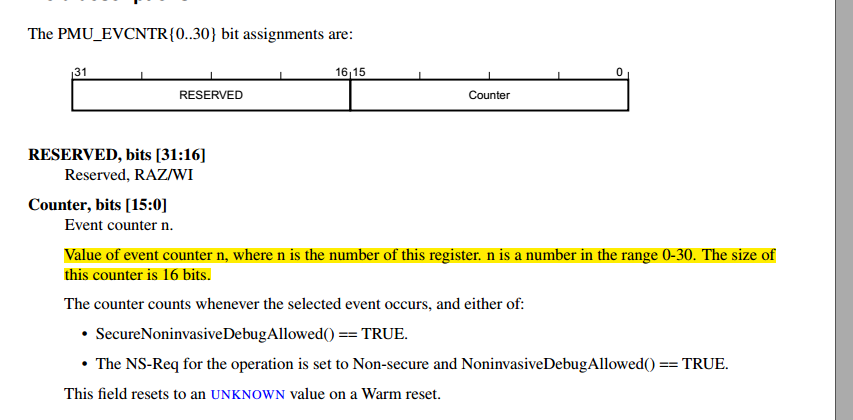

PMU_EVCNTRn (Performance Monitoring Unit Event Counter Register)寄存器用于保存monitor event n 的触发次数。

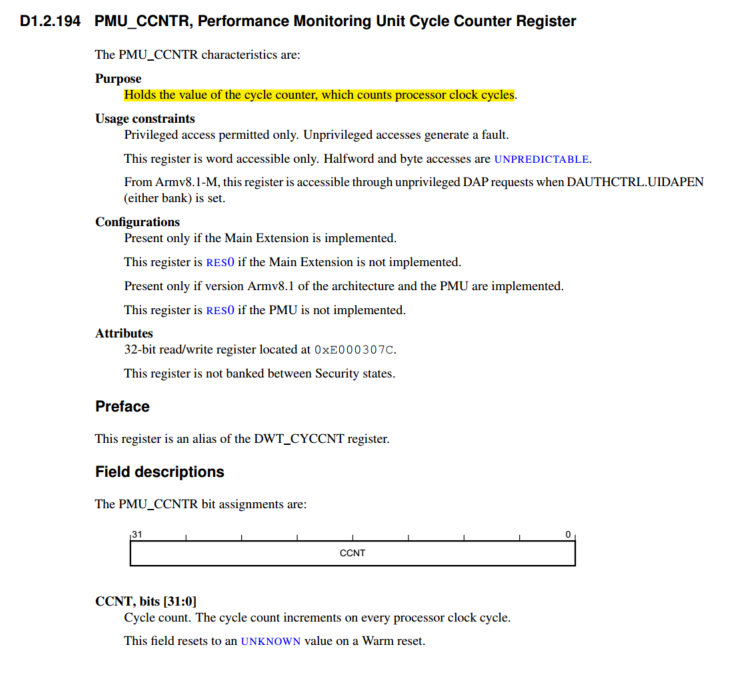

PMU_CCNTR(Performance Monitoring Unit Cycle Counter Register) 该寄存器主要是用来记录监测的cpu 的clock cycle信息。

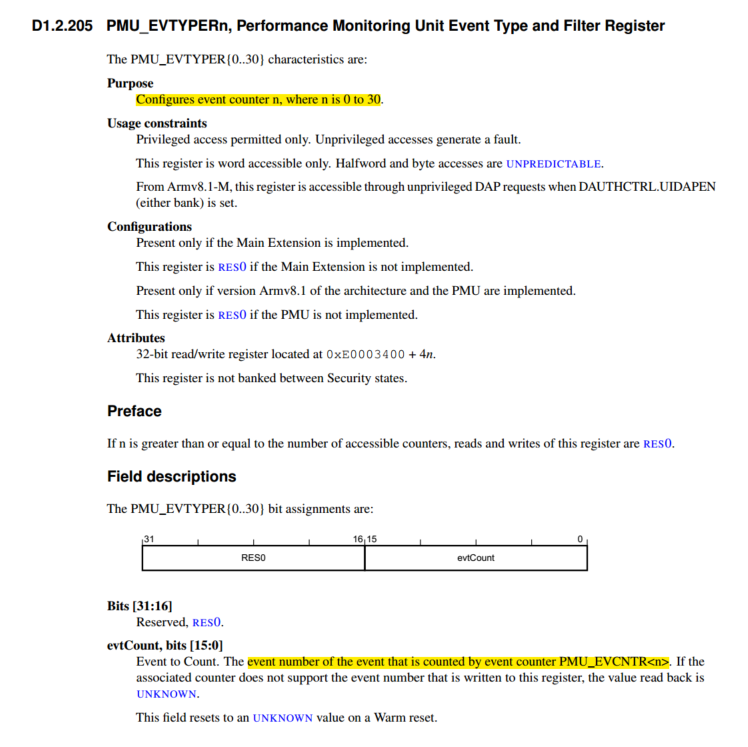

PMU_EVTYPERn(Performance Monitoring Unit Event Type and Filter Register) 寄存器用于配置事件要监测的event 类型,对应的event 发生会在PMU_EVCNTRn + 1

PMU_CCFILTR(Performance Monitoring Unit Cycle Counter Filter Register) 该寄存器作为保留寄存器后续使用,暂未使用。

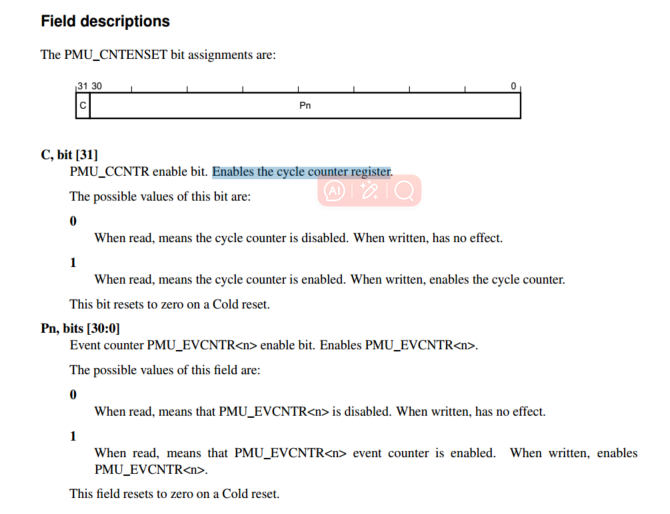

PMU_CNTENSET(Performance Monitoring Unit Count Enable Set Register)用于 enable cpu cycle counter 和 event 监测功能,bit 31 对应 PMU_CCNTR enable bit,bit0-30 对应Enables PMU_EVCNTR<n>

PMU_CNTENCLR( Performance Monitoring Unit Count Enable Clear Register) 和 PMU_CNTENSET 相反用于disable 对应的功能

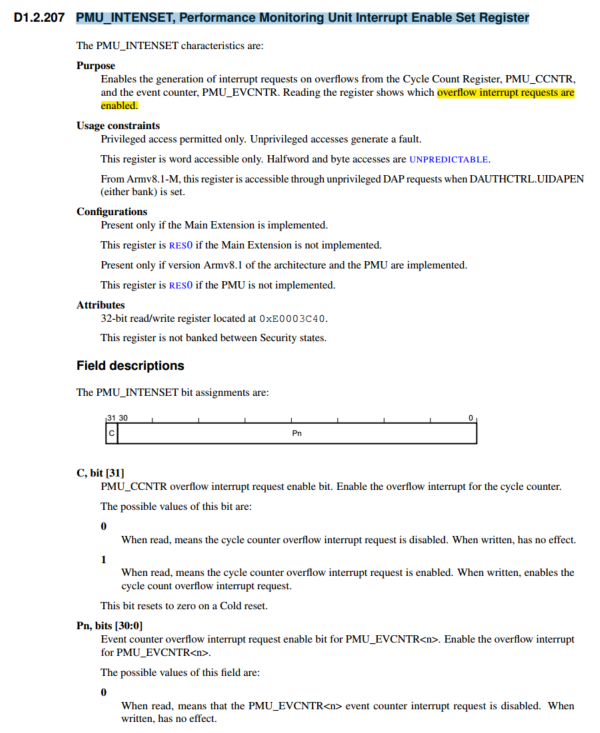

PMU_INTENSET(Performance Monitoring Unit Interrupt Enable Set Register)寄存器用于使能PMU_CCNTR 和 PMU_EVCNTR 事件计数溢出的overflow 中断使能

PMU_INTENCLR(Performance Monitoring Unit Interrupt Enable Clear Register) 和 PMU_INTENSET 相反用于关闭对应的overflow 中断。

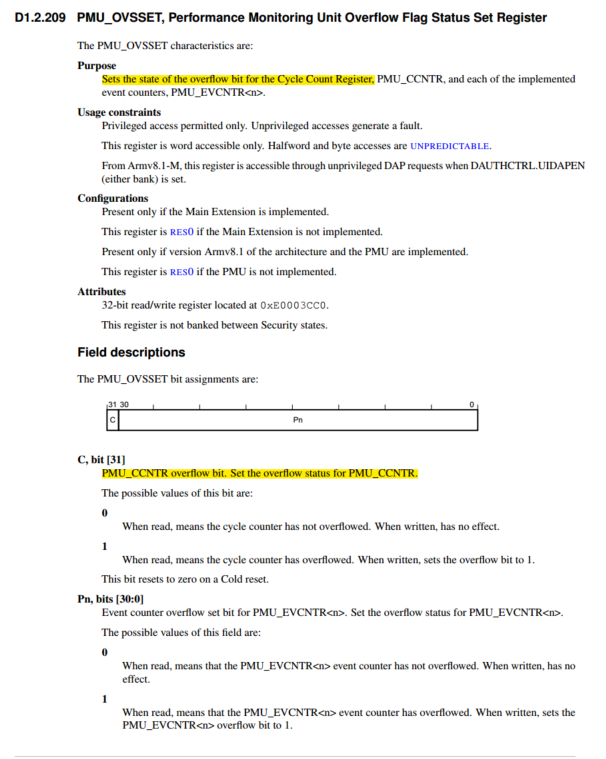

PMU_OVSSET(Performance Monitoring Unit Overflow Flag Status Set Register)寄存器在PMU_CCNTR 和 PMU_EVCNTR<n> 计数溢出时会更新该寄存器为0,如果开启对应的中断使能会触发中断事件。

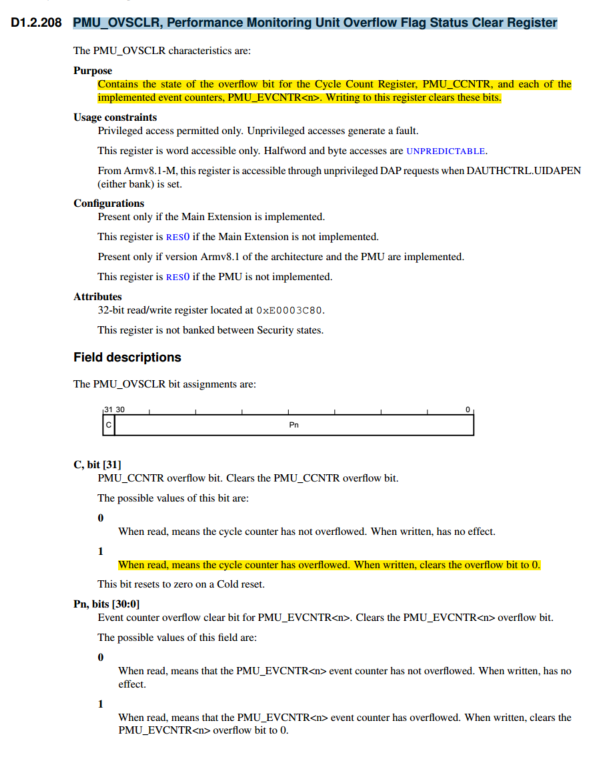

PMU_OVSCLR(Performance Monitoring Unit Overflow Flag Status Clear Register)寄存器用于清除PMU_CCNTR 和 PMU_EVCNTR<n> 计数的overflow 状态,对应位为1时写入即可清除该状态,对应的位为零写入则无影响。

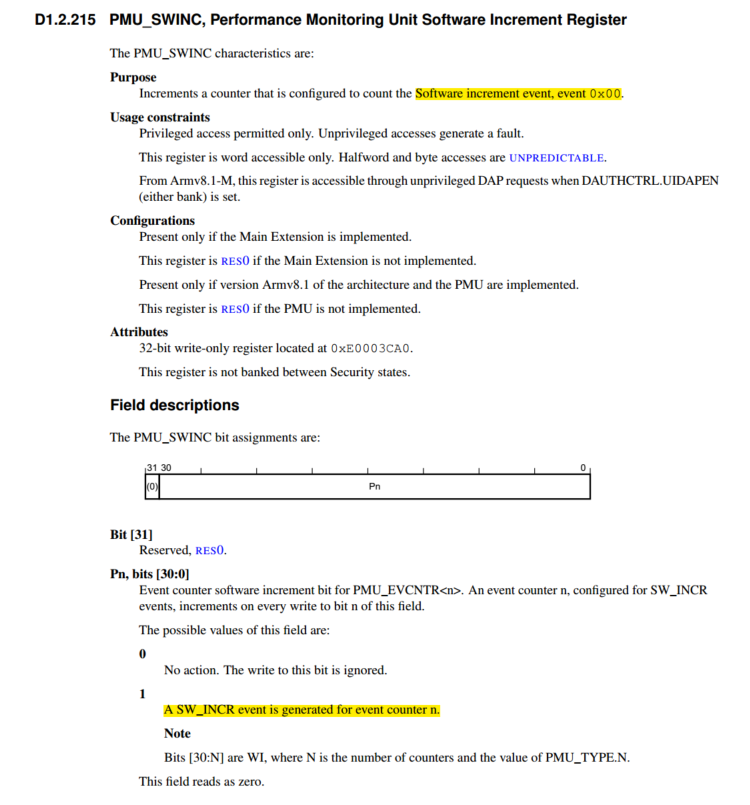

PMU_SWINC(Performance Monitoring Unit Software Increment Register) 该寄存器用于通过软件触发SW_INCR 事件。

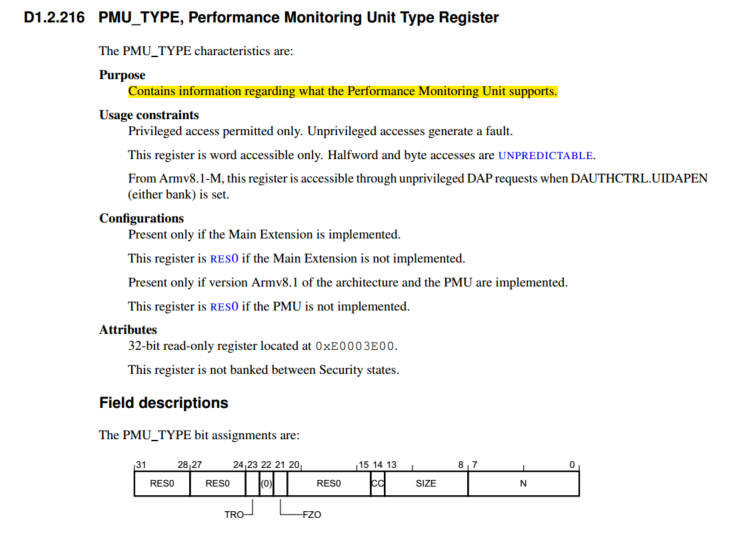

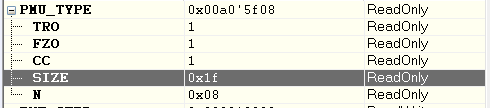

PMU_TYPE(Performance Monitoring Unit Type Register) 是个readonly寄存器包含了PMU 配置相关的寄存器,可以通过读取该寄存器来获取PMU 的功能属性信息。

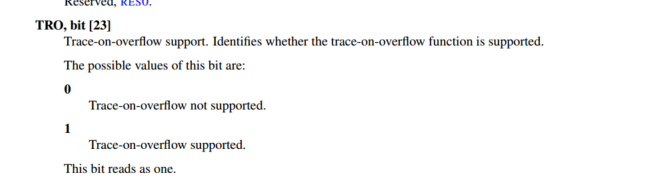

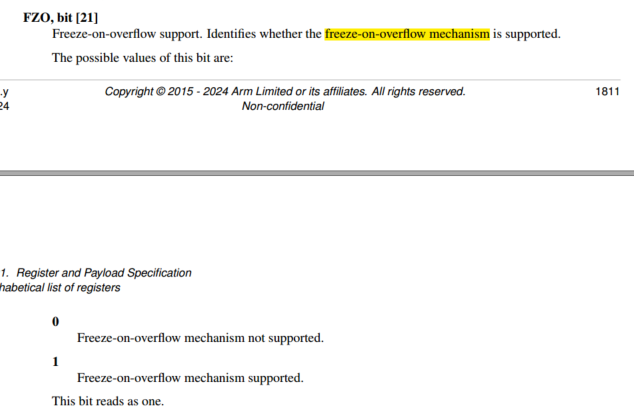

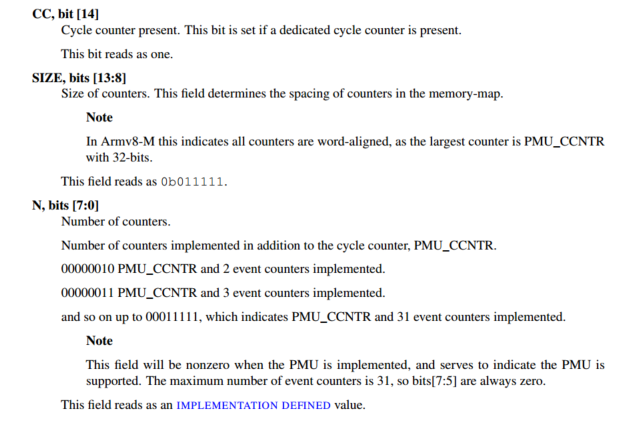

M85 处理器对应该寄存器的定义如下,可以看出述支持TRO/FZ0, 对你供应的cycle counter 的计数器sie为32bit,支持的event monitor 的数量为8,最多可以同时监测8哥event 和 cpu cycle counter.

PMU 相关需要我们关注的寄存器主要由以上这些,最新的CMSIS 软件包已经包含了PMU 的驱动库,我们后续可以使用CMSIS 的接口监测CPU的性能。

我要赚赏金

我要赚赏金