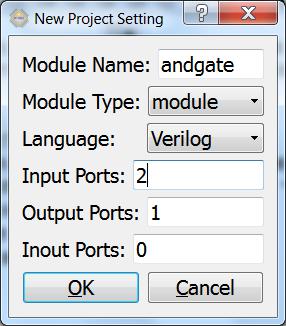

参数填写完成后点击“OK”按钮,Robei就会生成一个新的模块,名字就是andgate。

2)修改模型。在自动生成的界面图上用鼠标选中输入引脚“p0”,右侧的属性编辑栏就会展示该引脚相对应的属性。每条属性有其对应的名称。为了跟实验设计名称一致,我们把p0的名称改成a,p1的名称改成b,p2的名称改成y。修改的方法是在属性编辑器Name栏里面修改并点回车。为了区分每个引脚,我们可以修改每个引脚的Color值,并点回车保存。

3)输入算法。点击模型下方的Code进入代码设计区。

在代码设计区内输入以下Verilog代码:

assign y = a & b; //学习Verilog assign的写法。

该代码实现的是与门逻辑运算。

4)保存。点击工具栏![]() 图标,或者点击菜单“File”中的下拉菜单“Saveas”,将模型另存到一个文件夹中。

图标,或者点击菜单“File”中的下拉菜单“Saveas”,将模型另存到一个文件夹中。

5)运行。在工具栏点击![]() 或者点击菜单“Build”的下拉菜单“Run”,执行代码检查。如果有错误,会在输出窗口中显示。如果没有错误提示,恭喜你,模型andgate设计完成。

或者点击菜单“Build”的下拉菜单“Run”,执行代码检查。如果有错误,会在输出窗口中显示。如果没有错误提示,恭喜你,模型andgate设计完成。

3.2测试文件设计

1)新建一个文件。点击工具栏上的![]() 图标,在弹出的对话框中参照图2-1-9进行设计。

图标,在弹出的对话框中参照图2-1-9进行设计。

2)修改各个引脚的颜色。选中每个引脚,在属性栏中修改其颜色,方便区分不同的引脚信号。

3)另存为测试文件。点击工具栏![]() 图标,将测试文件保存到andgate模型所在的文件夹下。

图标,将测试文件保存到andgate模型所在的文件夹下。

4)加入模型。在Toolbox工具箱的Current栏里,会出现一个andgate模型,单击该模型并在andtest上添加。

5)连接引脚。点击工具栏中的![]() 图标,或者选择菜单“Tool”中的“Connect”,连接引脚p0到a,p1到b和y到p2。这个时候,注意查看连接线的颜色。如果鼠标要变回选择模式,点击图标

图标,或者选择菜单“Tool”中的“Connect”,连接引脚p0到a,p1到b和y到p2。这个时候,注意查看连接线的颜色。如果鼠标要变回选择模式,点击图标 。

。

6)输入激励。点击测试模块下方的“Code”,输入激励算法。激励代码在结束的时候要用$finish 结束。

initial begin //学习initial begin和end的写法

p0 = 0; //设置初始值

p1 = 0;

#1 //一个时钟延迟

p0 = 1;

#1 //再加一个时钟延迟

p1 = 1;

#1

p0 = 0;

#1

p1 = 0;

#1

$finish; //结束仿真的标志

end

7)执行仿真并查看波形。点击工具栏![]() ,查看输出信息。检查没有错误之后点击

,查看输出信息。检查没有错误之后点击 ,或者点击菜单“View”中的“Waveview”。波形查看器就会打开。

,或者点击菜单“View”中的“Waveview”。波形查看器就会打开。

8)点击右侧Workspace中的信号,进行添加并查看。点击波形查看器工具栏上的![]() 图标进行自动缩放。分析仿真结果并对照真值表,查看设计正确与否。

图标进行自动缩放。分析仿真结果并对照真值表,查看设计正确与否。

关注微信公众号 更多精彩教程为您呈现。

关注微信公众号 更多精彩教程为您呈现。