问题:

某客户工程师讲述,在其产品中需要使用STM32 的 ADC 对多路模拟信号进行同步采样。采用了 ADC 常规通道的扫描模式来完成这一功能。然而,在调试过程中发现一个奇怪的现象:当将各路模拟信号的电平设置成相同时,ADC对各路模拟信号的转换结果相同,假设结果用 A 来表示。改变其中某一路模拟信号的电平,并保持其它各路模拟信号的电平不变,ADC对该路信号的转换结果记为 B。结果发现此时与其在扫描次序上相邻的下一路模拟信号的转换结果也发生了变化,记为C。经多次实验发现,B 和 C 在数值上相对于A 有相同的变化方向。于是,怀疑 ADC 的相邻通道间存在着某种串扰。

调研:

重复试验,确认现象如其所述。检查其硬件设计,在与 VDD、VDDA、VSS、VSSA、Vref+、Vref-相关的电路中未发现异常。修改软件,增大 ADC 各个通道的采样保持时间Ts 。重新测试,发现 C 相对于 A 的变化量有所减小。进一步增大 ADC 各个通道的采样保持时间Ts,发现 C 相对A 的变化量进一步减小。

分析与建议:

对 ADC 所设置的采样保持时间Ts偏小,导致相邻通道之间透过采样电容发生了藕合。

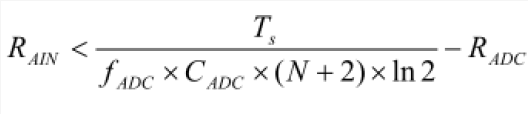

根据公式:

重新计算 ADC 的采样保持时间T。其中:

由该公式计算出的采样保持时间Ts,可以保证采样电容上的采样值相对于信号源的电平的偏差不大于1/4LSB。

当 ADC 的采样电容在两个通道之间进行切换时,其电路如下图(一)所示:

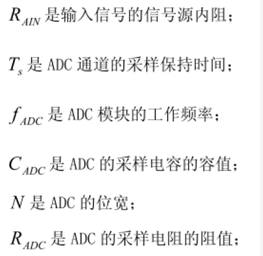

其中, Cs是ADC的采样电容,Rs是 ADC 的采样电阻。两路信号源 A 和B 的电平分别为Ua和Ub,其内阻分别是Ra和Rb。为了简化问题,假定两路信号的扫描次序是由信号源 B 到信号源 A,且信号源 B 接入的时间足够长,以至在通道切换时采样电容Cs上的电压可以近似的等于Ub ,于是,在通道切换到信号源 A 后,采样电容Cs上的电压将按如下曲线变化:

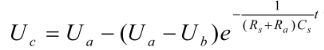

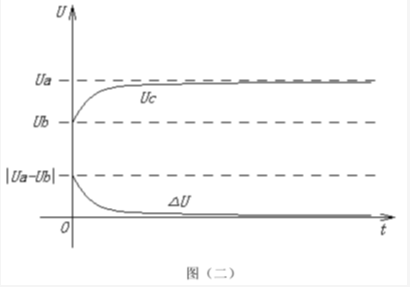

随着时采样保持时间t 的增长,采样电容Cs 上的电压逐渐趋近于Ua,而其与Ua之间的误差为:

该误差即是信号源 B 通过采样电容Cs对信号源 A 的藕合值,随着采样保持时间t的增长,该值逐渐减小,最终趋近于零,如图(二)所示。从上面表达式可以看出,有两种方法可以减小误差:

1. 通过增加采样保持时间t,使获得更多的衰减时间;

2. 通过减小信号源的内阻Ra,使其具有更快的衰减速率;

以上两点可以作为消除 ADC 不同通道之间通过采样电容Cs 产生寄生藕合的理论依据。在实际运用时,在增加采样保持时间方面可以通过修改 ADC 的设置参数来实现,而在降低信号源内阻方面可以通过在信号源与ADC 之间加入跟随器进行隔离来实现。