在一个前面的文章中 ,我介绍的基本概念和已知为锁相环(PLL)的负反馈系统的核心功能。你可能还记得,最基本的PLL由相位检测器(实际上是一个相位的差检测器),一个低通滤波器和压控振荡器:

VCO产生的周期性波形是主输出信号。在适当的情况下,PLL将确保输出信号的频率恰好等于输入信号的频率。

我更喜欢自己进行模拟,而不是完全依赖于其他人创建的情节和方程式。这几乎适用于任何电路,但对PLL来说尤为重要,因为在我看来,PLL功能的分析探索是令人困惑和不充分的。

初始瞬态响应尤其如此,即PLL在尝试锁定输入信号时表现出的行为。当我们试图获得直观的理解时,PLL的瞬态响应不仅难以实现 - 它也是非线性的,不易转化为方程式。实际上,这篇学术论文的摘要表明,即使是“精确的数值模拟”也可能存在问题,因为它们需要大量的处理时间。

电路

您可以通过多种方式模拟PLL。我创建的电路并没有什么特别之处,但我认为它是一个很好的起点,原因有两个:它在概念上很简单,它不会使SPICE引擎负担过重(换句话说,没有必要去喝咖啡)在你等待模拟完成时休息)。

这是我的LTspice PLL:

三个功能块中的两个非常简单。相位检测器是XOR门(我使用此处讨论的库),低通滤波器是单极RC电路。据我所知,即使是专业品质的PLL,通常也只能通过RC低通获得足够的性能。我在模拟中尝试了二阶滤波器,RC电路工作得更好。在我看来,二阶滤波器提供的附加纹波抑制根本不是必需的。

VCO

系统不太直接的部分是VCO块。我决定通过使用用于Linear Tech电阻器设置振荡器IC的宏模型来节省自己一些重要的时间和精力,而不是定制设计的电路,例如可变频率Colpitts振荡器。

LTC6900支持1 kHz至20 MHz的频率。尽管它被称为“电阻器设置”振荡器,但您也可以通过直接调节流入SET引脚的电流量来控制频率。这并不奇怪,因为电阻(连接在SET和V +之间)只是建立流入SET引脚的电流的一种方法,它由内部电路在V +电压减去~1.1 V时保持。

如您所见,我的LTC6900实现类似:

第一个区别是DIV引脚为5 V而不是接地(因为我想要更低的频率)。我做的另一个改变(考虑到这里的目标并不奇怪)是,我有一个电压控制的电流源,而不是一个固定的电流源。这是电路中最细微的部分,所以让我们仔细看看。

从电压到电流到频率

低通滤波的相位检测器信号用作VCO的控制电压。我通过使用数学关系而不是元件来简化我的电路,从控制电压转换为控制电流。流入SET引脚的电流定义为(使用任意行为电流源),因为CTRL节点的电压乘以常数。

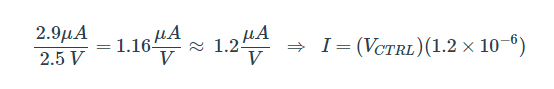

下一步是确定常数。我们知道输入频率为5 kHz,因此VCO最终需要稳定在5 kHz的输出频率上。通过反复试验,我确定当流入SET引脚的电流约为2.9μA时,VCO将产生5 kHz波形。这是我们需要知道的第一件事。

接下来我们需要考虑控制电压。相位检测器的输出在地和5 V之间切换,这意味着控制电压范围也是0到5 V.我们需要确保对应于~2.9μA的SET引脚电流的控制电压将是实际上,我希望最终控制电压在接近中间范围的某个位置,即2.5 V。因此,我只需将2.9μA除以2.5 V即可确定相关的因素。 SET引脚电流达到控制电压。

另外要记住的是,VCO应该与控制电压达到最大值时产生的电流兼容。我们无法真正预测电路的启动行为,因此我们不妨假设输入和输出信号的相位(或其他一些初始条件)之间的差异可能导致高相位检测器占空比,从而导致高度控制电压。如果这些高控制电压导致VCO发生故障,我们将遇到麻烦。在我的LTspice电路中,5 V的V CTRL导致SET引脚电流为6μA,这完全在可接受的范围内。

我们将在以后的文章中研究模拟细节和结果。现在我将给你留下以下图表,它显示了控制电压的变化,因为PLL逐渐锁定在输入频率上。

结论

在本文中,我介绍并解释了我为执行简单的锁相环仿真而设计的LTspice电路。瞬态响应在控制电压图(即相位检测器的低通滤波输出)中很明显。