随着网络技术的发展,网络通信控制器的应用已经越来越广泛。集成PowerPC微处理器的MPC8560 PowerQUICC Ⅲ作为一个多用途、高性能的通信微处理器,具有非常灵活的一体化单元系统和外围通信控制器,能被广泛运用于通信和网络系统,是目前为电信和网络市场而设计的最先进的集成通信微处理器之一。它集成了丰富的网络和通信外围设备,提供了更大的灵活性、扩展能力和更高的集成度。

MPC8560简介

MPC8560内部集成了两个处理模块:一个高性能嵌入式PowerPC e500内核和一个通信处理模块(CPM)。此外,该芯片还提供了片内缓存、DDR控制器、可编程中断控制器、通用I/O口、DMA和I2C等多种接口控制器。

与使用较多的MPC8260最大的不同是,MPC8560增加了两个三速以太网控制器(Three-Speed Ethernet Controller,TSEC),实现了10Mb/s、100Mb/s和1Gb/s三种不同速度的以太网协议接口控制。本文将主要讨论如何使用这两个TSEC实现吉比特以太网接口。

吉比特以太网物理层协议及接口

参考文献上对于网络协议的介绍往往局限于对协议分层的理论分析,对网络协议尤其是吉比特以太网协议在实际应用中的接口讨论较少,本文将对吉比特以太网协议在应用中的接口作总结性的介绍。

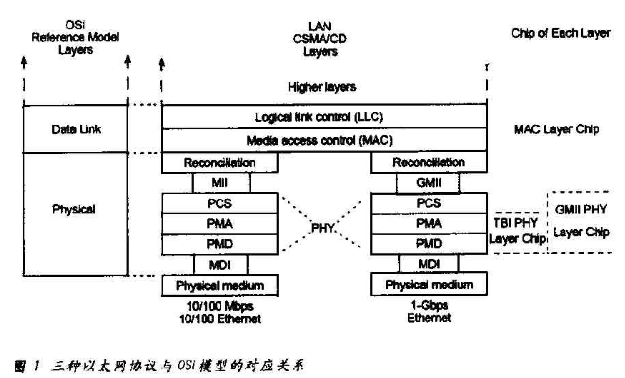

吉比特以太网协议的数据链路层与传统的10/100Mb/s以太网协议相同,但物理层有所不同。三种协议与OSI七层模型的对应关系如图1所示。

从图1可以看出,吉比特以太网协议与10/100Mb/s以太网协议的差别仅仅在于物理层。图中的PHY表示实现物理层协议的芯片;协调子层(Reconciliation sublayer)用于实现指令转换;MII(介质无关接口)/GMII(吉比特介质无关接口)是物理层芯片与实现上层协议的芯片的接口;MDI(介质相关接口)是物理层芯片与物理介质的接口;PCS、PMA和PMD则分别表示实现物理层协议的各子层。在实际应用系统中,这些子层的操作细节将全部由PHY芯片实现,只需对MII和MDI接口进行设计与操作即可。

吉比特以太网的物理层接口标准主要有四种:GMII、RGMII(Reduced GMII)、TBI(Ten-Bit Interface)和RTBI(Reduced TBI)。GMII是标准的吉比特以太网接口,它位于MAC层与物理层之间。对于TBI接口,图1中PCS子层的功能将由MAC层芯片实现,在降低PHY芯片复杂度的同时,控制线也比GMII接口少。RGMII和RTBI两种接口使每根数据线上的传输速率加倍,数据线数目减半。

由此可见,使用TBI接口来实现吉比特以太网接口所用的控制线和数据线比GMII接口少,因此设计与使用相对容易。虽然TBI接口比RTBI接口的数据线多,但是每根数据线上的传输速率可以低一倍,大大降低了PCB布板的难度。因此,相对其他方式,使用TBI接口实现起来最简单,难度最低。此外,TBI接口的PHY芯片比GMII接口的PHY芯片成本低很多。对于同时提供GMII和TBI两种接口的芯片,推荐使用TBI接口设计方案。

MPC8560与PHY芯片的接口设计

MPC8560对四种不同的接口标准都提供了支持,本文仅讨论TBI接口。

TLK2201芯片是支持TBI和RTBI两种接口的单信道吉比特以太网络收发器。它是业界第一批符合802.3规格的2.5V器件,无须任何外接电容,这可以节省电路板面积,减少零件的数目,从而降低产品的成本。此外,该芯片的功耗也相当低。

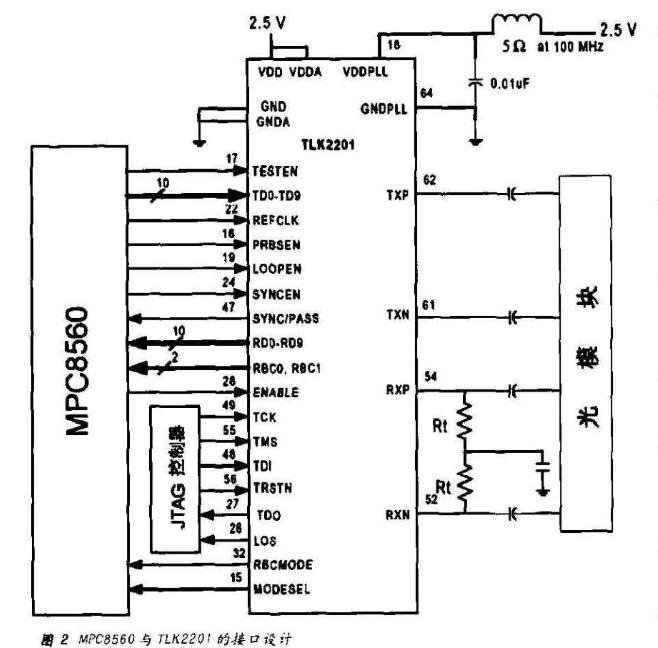

MPC8560与TLK2201的连接如图2所示。需要注意的是,TD0~TD9和RD0~RD9并不全是数据线。TD8对应Tx_ER,作为发送出错标志位;TD9对应Tx_EN,作为发送使能位;RD8对应Rx_DV,作为接收数据有效位;RD9对应Rx_ER,作为接收差错检测位。

此外还应注意到,图中使用的是SFP(可插拔)光模块,这是因为TLK2201只提供了光模块吉比特以太网接口。

对TSEC控制器的初始化

MPC8560对TSEC控制器的初始化过程如下。只要按照顺序逐一完成相应的步骤,即可正确配置TSEC的吉比特网络接口。

设置MACCFG1寄存器,对MAC进行软复位;

清除MACCFG1寄存器的软复位;

设置MACCFG2寄存器,选择TSEC工作模式(如全双工或半双工、CRC校验是否使能等);

初始化寄存器ECNTRL,设置接口为TBI标准;

设置MAC地址、物理地址;

设置MII口的速率,使用MDIO对PHY进行初始化;

清除并设置中断相关的寄存器IEVENT和IMASK;

设置Hash表和Hash寄存器;

初始化接收控制寄存器RCTRL;

设置DMA控制寄存器DMATRL;

设置接收缓冲区大小;

设置收发缓冲描述符(Buffer Descriptor,BD);

设置MACCFG1中的收发使能位,完成TSEC初始化。

在初始化TSEC的过程中尤其要注意在设置寄存器后,控制器处于不稳定状态,不能马上执行下一步的操作,需要作一定的延迟等待。通常,可以读取相应的状态寄存器以判断是否可以继续下一步,也可以使用某些操作系统提供的定时延迟来完成,如VxWorks中的taskDelay()。

测试及其结果

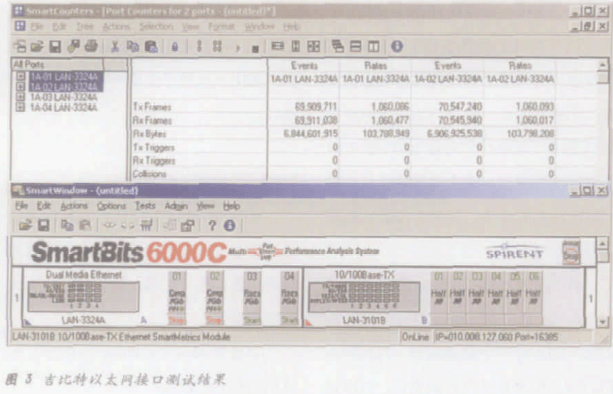

为了测试设计好的吉比特以太网接口的性能,将吉比特以太网接口与专门测试网络接口性能的仪器SmartBits相连。一个最为简单的测试方法是使用SmartBits发送数据包到MPC8560的吉比特以太网接口,MPC8560接到数据包后,将数据直接返还给SmartBits。SmartBits将会统计并显示测试结果。

测试结果如图3所示,传输速率(Rates)可以达到1Gb/s左右,而且还略有裕量。

为了测试吉比特以太网接口更为全面的性能,需要对不同大小的数据包、突发大量数据流等进行测试,限于篇幅,不再讨论具体的测试细节。

设计中的注意事项

由于数据线上的传输速率相对较高,硬件部分的设计需要注意以下几点。

TBI接口每根数据线的传输速率是125Mb/s,为了保证采样与信号的同步,接收信号线RD0~RD9的长度和接收时钟线RxCLK必须等长。同理,发送信号线TD0~TD9的长度和发送时钟线TxCLK也必须等长。

为了保证阻抗匹配,TBI接口所有信号线的阻抗必须控制在50Ω±5%。

光模块的输入信号是高速差分信号,设计时应该注意接收与发送的两对差分信号线必须等长。同时,差分阻抗需要控制在100Ω±5%,以保证阻抗匹配。

为了保证电源干净,TLK2201的PLL电源输入端必须加滤波器。

驱动软件部分的设计需要注意以下几点。

GE端口收发对于软件处理能力要求较高,需要仔细设计收发缓冲区的深度,合理调度收发处理程序,保证数据收发性能。

对于BD表的维护,需要正确维护BD读写指针和BD的状态标志位,以避免缓冲区重叠和溢出。尤其应注意BD读写指针需要根据收发缓冲区的大小,在合适位置进行循环。

如果设置了PHY使用自协商(auto-negoTIaTIon)方式,一定要在自协商方式正常工作后,才能设置TSEC是否使用全双工或半双工模式。

我要赚赏金

我要赚赏金