1、引言

时间数字转换(tdc)技术原本是实验核物理中的课题,随着科学技术的不断发展,精密时间测量数字化技术在高能物理、雷达、激光和声纳测距、通信测向、遥感成像等都应用了高分辨率的tdc技术,全数字集成电路的工艺简单,造价较低,设计难度较小,是电路设计人员追求的目标,因此,全数字的tdc也成为研究人员关注的问题,文献报道了一种全数字化的模数变换电路(adc),该方法本质上是基于全数字tdc的,以0.8μm cmos工艺在0.45mm2面积上实现了18位全数字的adc,该芯片在10ks/s采样率下可以达到12μv分辨率,非线性度为±0.1%。文献报道了该系统的tdc原理和专用集成电路(asic),用1.5μm的cmas工艺以1.1mm2面积实现了13位的tdc,其分辨率仅为单个门的延时时间,约0.5ns。

本文将文献的方法移植到pld中,pld包括fpga和cpld。可以有效地缩短研发周期,提高设计灵活性和重用性,降低设计成本和流片风险,一旦设计成功,所形成的软核可以与工艺脱钩,使设计重用变得十分方便。

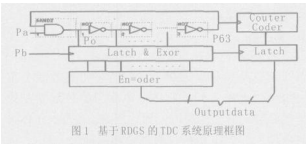

文献设计的tdc用环形延迟门单元(rgds)实现时间的分割,结构如图1。该设计采用延时门组成的环形延时单元作为时间信号的测量基础,译码器译码作为低位数字输出,后接环形计数器记录循环次数作为高位数字输出,最后将两组数字合并作为测量结果输出,有效降低了延时门的使用数量,从而减小了芯片面积。

将此方法移植到fpga/cpld设计中,需解决以下几个问题:1、延时门的设计和综合问题,2、单门电路延时时间的离散性,使各个门有相对等同的延时时间,3、考虑计数器最高工作频率,4、对所设计电路进行优化,使之在满足指标的情况下,占用较小的芯片资源,所选用的目标芯片经济适用。

本文在altera公司的max系列芯片上实现了上述结构的设计,仿真结果表明,在max系列中的max7000芯片可以达到的最高时间分辨率为3.5ns,硬件测试也是成功的。

2、基于rgds的tdc系统工作原理

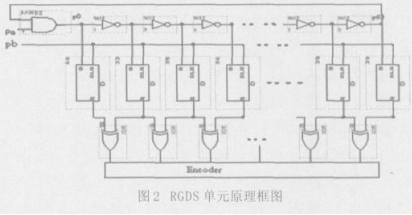

基于rgds的全数字tdc系统由环形延时单元、锁存与异或单元,编码单元、计数和锁存单元四部分组成,图2是图1中前三部分的电路原理图。rgds部分由63个非门和一个与门组成,其中电路节点po至p63的状态可以反应pa脉冲在非门链中传输所到达的位置,该位置的检测则由锁存与异或单元实现,在通常情况下,非门的输出和输入是反相的,但是对于pa信号在非门链中上传输恰好到达的那个非门来说,其输出和输入是同相的,异或门负责检测非门链中输出和输入相同的那个非门,即可得知信号到达的位置,进而计算出信号在rgds上的传输时间。

计数和锁存单元是一个7位计数器,其作用是对每一次pa信号传输到终端p63后作一次计数,采用双边沿计数器,该计数相当于在整个tdc过程中的“粗计数”。粗计数加上锁存与异或单元对p0到p63之间的“细计数”,可形成一次tdc过程的完整计数。细计数的值在编码单元形成,作为总计数的低位输出。由于64个非门可以组成6位输出,加上粗计数部分的高7位,组合为该tdc系统的13位最终输出,由此可见,tdc系统的分辨率由rgds中单个门的延时决定,而时间测量的动态范围则主要由计数器的位宽决定,采用rgds结构的asic实现了1.5μm cmos工艺13位的tdc电路,芯片面积1.1mm2,分辨率达到0.5ns。

3 、tdc的pld实现

将此方法移植到fpga/cpld设计要解决若干问题,eda工具对任何电路综合扩充的是逻辑功能而非特定的电路结构,所以很难得到所需的串联延时门结构,由于可编程器件内部的布局布线不能保证延时门的一致性,将影响tdc的转换精度,严重时甚至不能正常工作,另外,通用计数器的计数频率受到多种因素的限制,过高的工作速度可能会导致跳码,这也使rgds的结构设计受到一定限制。

3.1 环形延时单元的设计

如上所述,直接将上述asic设计中的环形延时单元移植到fpga/cpld中是不可行的,即使采用原理图输入的方法,经综合器综合后也得不到所需要的功能结构,原因很简单,eda工具做综合时是从电路输入和输出的逻辑关系出发给出综合结果,进奇数个非门的及联综合为单个非门或将偶数个非门综合为一条连接线,从而无法生成所需的延时结构,而本设计的目的是为了取得各级连非门之间的延时信息,所以简单地直接移植asic设计中的级联非门不能达到此目的,解决方法是将非门改称二端口输入的器件,例如用二输入与门或与非门代替非门,其中一个输入端口的联接方式和非门时情况类似,形成串接关系,将所有门多余的输入端口连接到高电平,此端口在仿真时还可以起到控制作用,但如果门的数量太少时,有可能发生一种情况,即在所有串接门上的延时总和小于计数器正常工作所需的最小时间,此时计数器将产生漏记或跳码现象,使rgds系统发生紊乱,而串接门的数量太多,又会使门延时时间离散的可能性增加,同时编码器的工作速度也决定了门的数量不能太小,因此需要通过仿真取得折衷的设计。

3.2 延时门的延时离散性

与asic不同,设计者很难预料eda软件布局布线后的情况,而且各种不同结构和性能的pld布局布线的结果也不尽相同,因此很难预计单个门的延时时间,即使通过仿真器得到一个数据,在硬件实验时,情况也会有所相同,而单个门的延时时间是整个系统精度的基本保证,所以有必要研究可资应用的方法。

本文从三方面考虑:1、通过减少延时环电路中门电路的数量可以有效地减小门延时时间离散的可能性,尽可能选择粗粒度的芯片,引起基本逻辑功能块大,串联门被配置在同一宏单元的可能性较大;3、尽可能选择连续互联型芯片,因其布线延时是相对固定和可预测的,可有效减小布线带来的误差。如上所述,串联门的数量要在计数器和编码器工作速度间做出平衡,按照xilinx的指标,一个16位的计数器最小时间为4.3ns,也就是可以达到232.558mhz的计数频率,在低于此工作频率的条件下,决定延时门的数量一般是可靠的。

通过对max系列大部分芯片做rgds系统两个循环周期的仿真,除了max5000和max9000延时较长未做测试外,其外各种芯片的单门延时时间在3.4-5.1ns。本设计的rgds采用了8个门组成的延时单元,在max7000芯片上实现分辨率为3.5ns的tdc系统,该系统中计数单元稳定工作在34.72mhz,计数时间为28.8ns。

3.3 设计电路优化

这是本设计不可缺少的环节,如采用max+plusii软件时,优化前rgds单元中编码器误码率高,不能正常工作,而经优化后,可以输出稳定准确的数据,可见在移植本方法时设计优化所起的作用,仍以max+plusii为例说明优化的一般过程,对软件优化开关的设置如下:1、因本设计选用max系列芯片,故选择对该芯片的多层综合选项(multi-level synthesis for max5000/7000/9000 device);2、在面积和速度优化选项中,选择对面积的优化,使rgds尽可能分配到同一个lab中,3、打开“slow slew rate”以降低开关噪声,打开“xor synthesis”以减少芯片面积的占用。4、打开“turbo bit”和“parallel expanders”开关,以对编码通过软件优化。

4、电路实现和仿真、测试结果

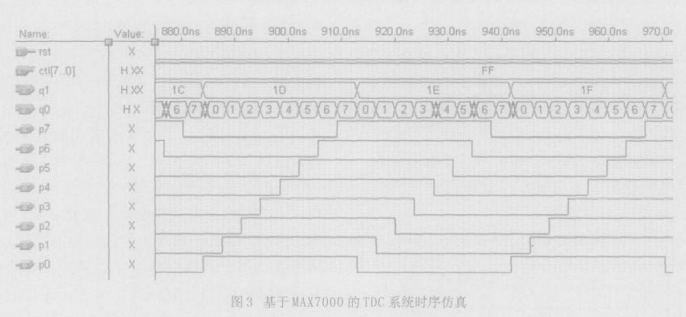

本设计以altera公司的max+plus ii 9.23为设计工具,在max系列芯片上实现。图3为max7000系列的时序仿真结果,其中p0至p7分别为rgds电路单个门之后的电路节点,ct1[7…0]为rgds中各延时门电路的控制端,即所有二端口门中多余的输入端子的互联,rgds正常工作时被置为高电平;rst为系统复位信号,q1为计数器输出作为tdc系统的高13位输出,为粗计数部分,q0为对rgds编码输出,作为该tdc系统的低3位输出,为细计数部分,此处还应考虑计数器延时和rgds编码输出延时之间的关系,应尽量使其同步,避免编码错位。

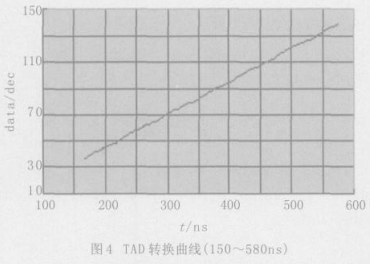

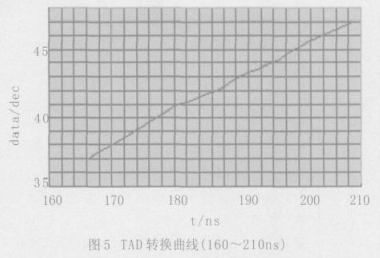

为了解决所设计tdc的硬件测试,专门设计了一个信号控制电路,该电路的tdc可以测量信号发生器所发生的连续脉冲的脉宽,从脉宽的测量可以估算出分辨率。限于条件,硬件测量采用目标芯片max7000s系列的epm7128slc84-15,电压为5v。图4是输入脉宽和测得的计数值关系曲线,共测量了85个值。横坐标是sp1641b型函数信号发生器发生的信号周期(ns),其对应的频率范围为1.4-3.2mhz,纵坐标是计数值。从图中曲线可以看出两者的线性关系,采用epm7128slc84-15的仿真结果,可以得到分辨率为9.8ns和tdc。经测量,在85个测试数据中,测量系统可以分辨出4.14-4.49ns的脉宽差,说明硬件的实际分辨率高于仿真结果,图5是图4中信号周期从160-210ns时的放大图,可以看出计数值无跳码,只有很小的波动,表示设计是完全合理可行的。由于7000s是慢速电路,按照此测量结果,如果采用max7000系列的芯片,完全可以达到或高于仿真结果表明的3.5ns的分辨率。

通过仿真和硬件测试表明,该设计系统能够准确计数,各项功能均达到预期的要求,整个设计的正确性和完整性得到验证,经优化后的设计,以max系列epm7064lc44-7为目标芯片的综合报告显示,其1250个门用了54%,转换率最高可达3.5ns,这表明本文的设计思想和实现方法是可行的。

5、结语

采用8个与门电路结构rgds实现的16位tdc系统,才保证计数器稳定的前提下,使rgds中单门延时的离散可能性大大减小。本设计max系列芯片max7000上实现了最高分辨率为3.5ns的tdc系统,仿真数据和硬件测试均表明计数结果稳定准确,由于采用vhdl语言实现设计,所以本设计可方便地移植到其他基于pld的设计中。

我要赚赏金

我要赚赏金