电池供电和功耗敏感应用的迅猛增长刺激了全球对低功耗半导体的需求。今天,功耗敏感应用的人员面对更加严格的系统总体功耗限制、规范和标准。今天,功耗敏感应用的设计人员正面对着更严格的系统总体功耗限制、规范和标准。与此同时,这些应用对功能、性能和复杂性的要求也在增加,但却不能增加电池消耗或成本。

设计人员过去依赖ASIC而不是FPGA来满足其设计中的低功耗约束。由于开发周期较长,一次性工程费用(NRE)高,缺乏应对标准变化及进行后期设计修改的灵活性,所以采用硬连线ASIC风险较高,对产品生命周期较短的应用不太实际。随着竞争加剧,上市时间对产品的成败越来越重要,PLD 逐渐成为首选的解决方案。市场研究机构iSuppli预测,在约值200亿美元的ASIC市场中,高达30亿美元的份额将会转向低功耗FPGA解决方案。

事实上,设计人员已逐渐发现要适应不断演进的标准、缩短开发周期并达到下一代先进半导体产品所要求的封装尺寸和功耗指标,必须采用低功耗的可重编程解决方案。例如,用于智能手机的FPGA必须在超低功耗和手机内各种不同技术 (如存储、触摸屏或键盘) 的高效控制及接口能力之间实现平衡。

FPGA的选择

当然,并非所有的可编程逻辑技术都能很好地满足低功耗要求。事实上,当今市场某些所谓的“低功耗”器件的电流消耗高达30mA,这往往比对功率敏感的典型电池供电应用所能容忍的耗电量高出1~2个数量级。

可编程器件在上电和配置之后的功耗分为两种基本形式——静态功耗和动态功耗。静态功耗是器件上电配置后闲置状态下的耗电量;而动态功耗则是指器件在工作状态下的耗电量。以往,动态功耗是功耗的主要部分,为了解决动态功耗问题,器件电源电压 (Vcc) 曾经随工艺尺寸的缩小而不断降低,系统电压也随之减小,但是继续降低器件Vcc的日子已不复存在。不仅如此,由于基于SRAM的器件晶体管密度极高,每一次半导体制造工艺节点的缩小都意味着静态功耗的增加。因为工艺节点缩小后,量子隧道效应(quantum tunneling)和亚阈区泄漏(sub-threshold leakage)之类的问题变得更加严重,这对面向功耗敏感应用的器件来说,是一个实实在在的挑战。随着漏电流加剧,静态功耗开始成为功耗的主要部分,成为人门最关心的问题。

由于不需要数百万耗电的 SRAM 配置数据存储单元,故基于闪存的非易失性FPGA的静态功耗比基于SRAM解决方案要低得多,因而成为功率敏感应用的理想选择。

针对功耗和I/O而优化的FPGA

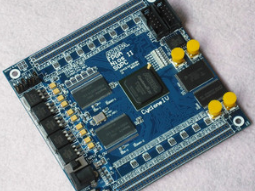

以基于闪存的IGLOO PLUS FPGA为例,它针对I/O密集的应用进行了优化,除提供可编程逻辑器件通常具有的可定制及上市速度快等优点之外,还可为工业手持应用 (如RFID读取器) 的设计人员提供与多个器件连接的能力。如图1所示,在这类控制应用中,IGLOO PLUS FPGA可用于电平转换、通用I/O扩展、地址和数据总线的多路复用/解码、排序、接口转换,以及胶粘逻辑 (glue logic)。

在给定封装尺寸下,IGLOO PLUS系列可提供极佳的每I/O功耗、面积、逻辑和功能比率。与采用同类封装的竞争可编程逻辑器件相比,IGLOO PLUS的静态功耗降低至其1/6;动态功耗减少50%;I/O密度提高1倍;逻辑密度高出1.7倍。

I/O解决方案设计人员面对各种各样的实现方案和配置选择,这些选择可能直接影响其最终设计的效率和效能。这种灵活的I/O结构支持宽泛的电压和I/O标准,能够帮助用户应对日益增多的各种不同应用的挑战。爱特公司 Libero集成设计环境(IDE) 提供了一种简易的I/O实现方法,从而开发出强大而稳健的设计。

结语

随着电池供电和功率敏感应用的急剧增长刺激了全球对低功耗半导体的需求,设计人员正逐渐发现需要采用低功耗可重编程解决方案来适应不断演进的标准和技术;加快上市速度,并提供下一代前沿硅解决方案所需的封装和功耗性能。对于当前采用可编程逻辑技术的设计人员来说,确定哪一种是最佳器件主要取决于功耗、性能、逻辑和I/O数量等设计约束。