介 绍

对实时视频流的需求给视频服务提供商带来了严峻挑战,因为他们必须在管理基础设施和互联网带宽运营成本的同时,还要为客户提供高质量体验。鉴于视频转换的计算强度,转码不断推升对灵活应变硬件加速的需求。

如今,视频服务提供商运用新一代压缩标准和自适应比特率 (ABR) 视频流协议,在保障高质量视频分发的同时对带宽进行管理。然而,两种方法虽都能降低比特率,但却会提高计算的复杂性。有没有一种鱼与熊掌可兼得的方案呢?

赛灵思与慧与公司 (HPE) 已经开发出一种足以掀起性能革命的最终用户解决方案。该方案使用搭载第二代 AMD EPYC 处理器的 HPE ProLiant DL385 Gen10 Plus 服务器。

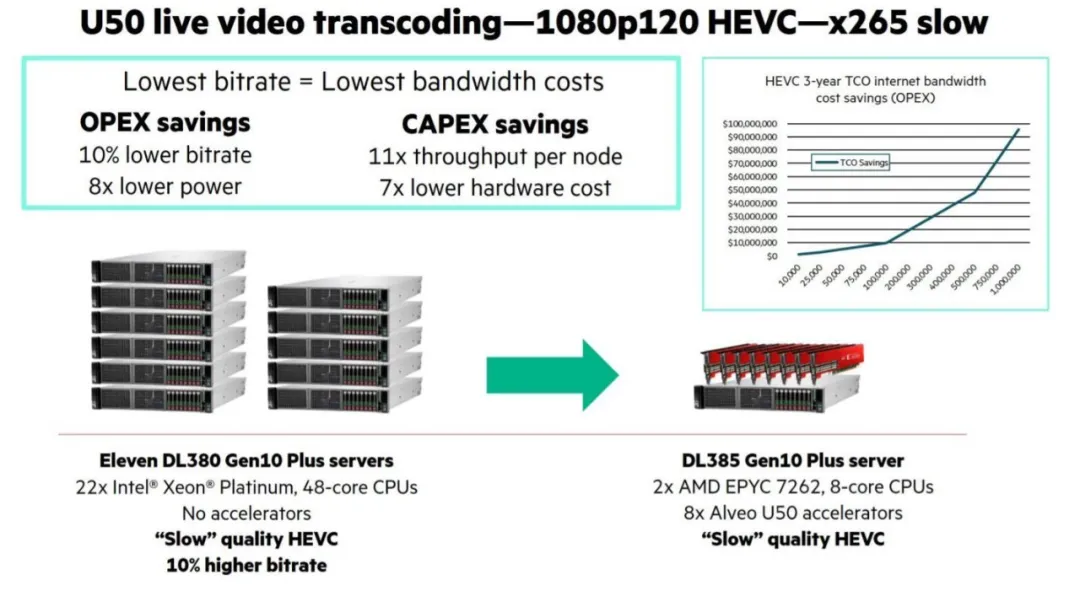

图 1:HEVC TCO 示例

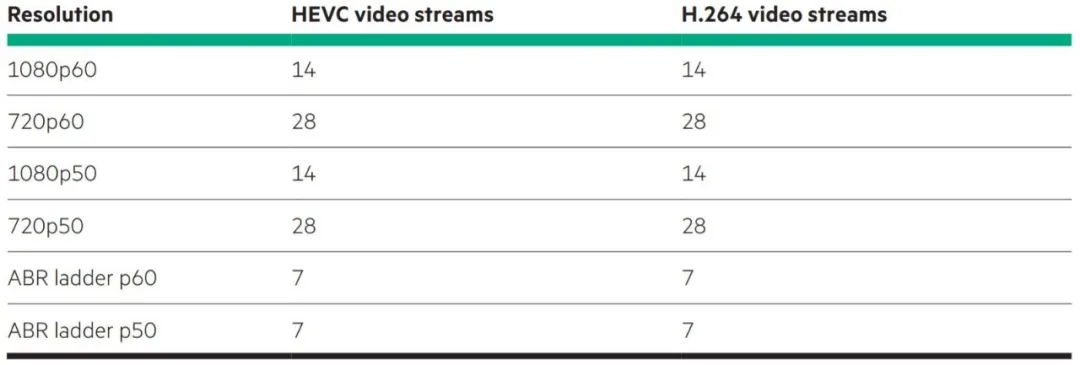

该服务器配置了 7 个 U50 用于编码、1 个 U50 用于 H.264 解码和缩放,能够支持视频流分辨率和全部 ABR 阶梯,如下表所示:

图 2:视频流与转码 ABR 阶梯示例

智能分区

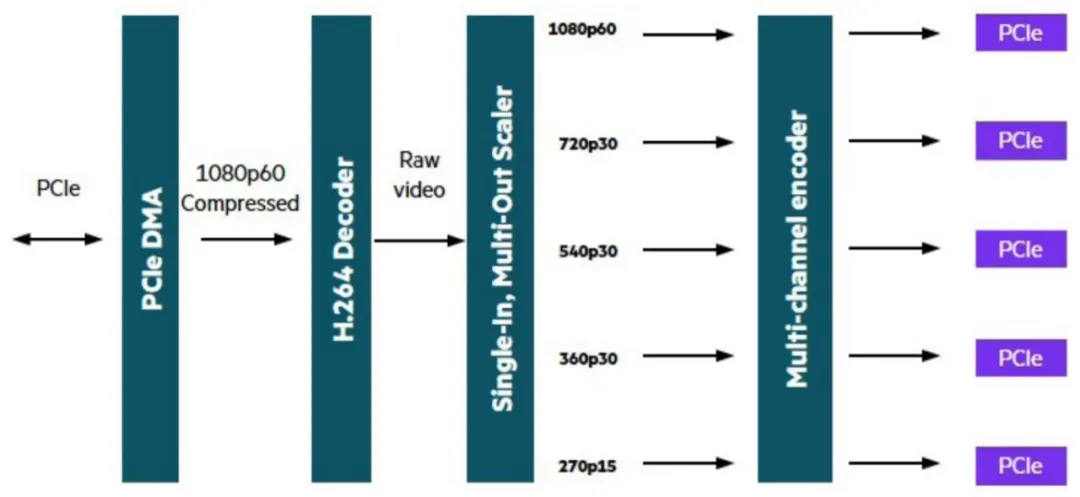

赛灵思与 HPE 携手提供最高系统级性能。通过详细的工作负载配置,能够确保在主机 CPU 和 Alveo 加速器卡之间进行智能功能分区。从 CPU 卸载编码器功能可确保处理器能够为音频处理和广告插入等其他关键任务提供支持。对 FFmpeg 插件的支持有助于客户将 Alveo U50 加速器卡和软件轻松集成到现有基础设施中。标准的命令行窗口也提供了全面控制。

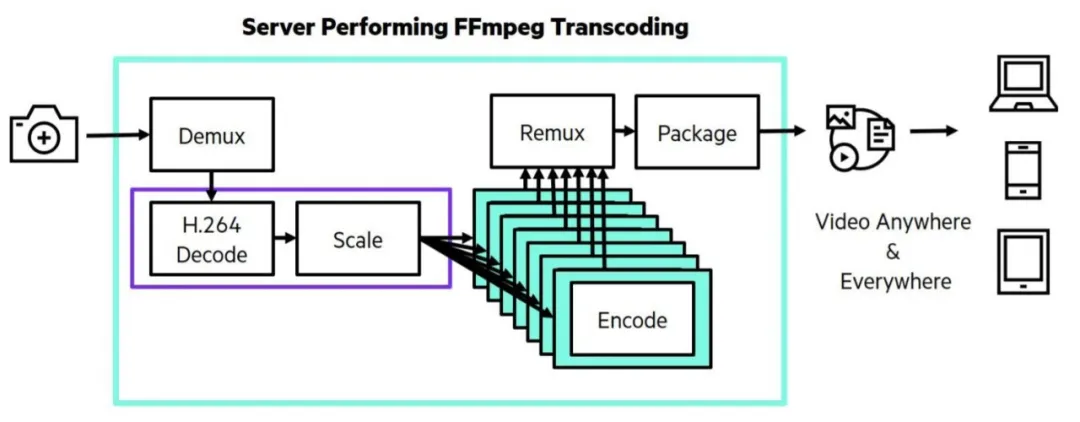

图 3:从内容生成器将数据流转码到消费端

优势与特性

1080P60 实时编码,具备 x265 慢速画质

提高每节点吞吐量

较低的比特率编码有助于降低网络带宽成本

更低的硬件成本

与基于 CPU 的编码相比功耗更低

用于****、定标器和编码器的 FFmpeg 插件

提供软件编码器不具备的确定性性能

HEVC:主 10 配置文件,级别可达 5.1 HD/SD 4:2:0 8 位

H.264:主 10 配置文件,级别可达 5.1 HD/SD 4:2:0 8 位

比特率:从 100Kb/s 到 40Mb/s 可配置

时延:从 100ms 到 10s 可配置

恒定比特率、受限可变比特率 (VBR) 和 ABR 模式

帧类型:I、P 和 B,提供灵活的开放/闭合 GOP 模式和 GOP 长度

低成本 HPE 服务器,提供比软件型解决方案更低的总体拥有成本 (TCO)

CPU 上最低的服务器负载,实现音频处理和广告插入等附加功能

HPE iLO BMC 可支持 Alveo U50 卡

初启您的自有编码器 IP

部署了专有视频编码器 IP (使用 C++++ 或 RTL 编写)的客户也能利用 Alveo Vitis 工具链提供的加速卸载功能。请联系您当地的 HPE 或赛灵思销售代表了解详情。

方案介绍

采用 HPE 与赛灵思技术

降低硬件成本并提高比特率效率能够大幅节省资本支出 (CAPEX) 和运营成本 (OPEX)。

解决方案构成

HPE ProLiant DL385 Gen10 Plus 服务器

赛灵思 Alveo U50 加速器卡

赛灵思视频转码固件与许可证

产品简介

低比特率高画质实时编码,提供最低的互联网带宽成本 (OPEX)

– AMD 第二代 EPYC 处理器技术

针对视频编码功能,以最低主机 CPU 负载加速编码

– 支持 ABR 阶梯的高性能 HEVC 和 H.264 编码流

完整配置的编码流水线解决方案

– 基于行业标准 FFmpeg 的简单 API

我要赚赏金

我要赚赏金