为了降低DSP外部SDRAM存储系统的功耗,针对DSP访问片外SDRAM的功耗来源特点,提出了基于总线利用率动态监测的读写归并方案。该方案动态监测外部存储器接口(EMIF')总线的利用率,根据总线利用率的不同选择开放的页策略,封闭的页策略或休眠模式。

DSP有限的片内存储器容量往往使得设计人员感到捉襟见肘,特别是在数字图像处理、语音处理等应用场合,需要有高速大容量存储空间的强力支持。因此需要外接存储器来扩展DSP的存储空间。

在基于DSP的嵌入式应用中,存储器系统逐渐成为功耗的主要来源。优化存储系统的功耗是嵌入式DSP极其重要的设计目标。本文主要以访问外部SDRAM为例来说明降低外部存储系统功耗的设计方法。

访问SDRAM的低功耗优化设计方案

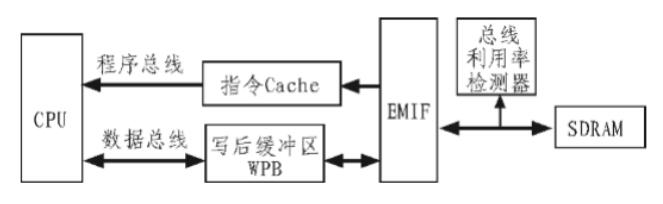

为更好的管理外部SDRAM,大部分嵌入式DSP片上集成和外部存储器的接口EMIF,DSP的片内设备通过EMIF访问和管理存储器。由EMIF将对同一行的读写尽量归并到一起进行,减少激活/关闭存储体引起的附加功耗开销。图1为基于总线监测的读写归并设计方案的框图。

图1基于总线监测的读写归并方案

1)采用块读的方法取指令。加入简化的指令Cache,将对SDRAM的读程序读操作按块进行。只有在Cache错过时,由Cache通过EMIF对SDRAM进行块读,每次读16个字节。

2)加入写后数据缓冲区(WPB),将数据总线上的请求发往WPB,由WPB对SDRAM进行块写、读写归并。

3)动态监测EMIF总线的利用率,块读和读写归并时采用开放的页策略,当总线利用率较低时,采用封闭的页策略,当总线利用率很低时,将SDRAM进入休眠模式。

我要赚赏金

我要赚赏金