作者:李北国,杨圣龙,李辉景

引言

LVDS(LowVoltageDifferenTIalSignal)信号比传统TTL接口有很低的电压摆幅、较高的噪声容限能力,且功耗仅为几毫瓦,抗干扰性相对其他总线接口也具有一定优越性。但由于其低电压差分传输导致其正常通信距离仅为5m左右,同时在面对空间复杂的电磁环境时会导致信号传输误码,降低传输可靠性。本设计通过对传输接口增加驱动器和自适应均衡器,极大地提高了LVDS信号通信距离;同时在链路中采用了10B6B的编码方式,在维持直流平衡的基础上还可检测并纠错1bit的数据,一定程度上减小了数据传输的误码率,保证了LVDS信号在恶劣环境中高速远距离传输时的可靠性。

1硬件电路的优化设计

工程应用中采用一般LVDS接口进行数据传输时,在传输距离为5m时信号已经发生严重衰减和畸变,无法正常区分高低电平,从而导致传输时产生很高的误码率。

在LVDS链路传输时,误码和丢数产生原因可从以下方面进行分析:

(1)发送端信号驱动能力不足,距离较长时信号衰减严重;

(2)线路中直流不失衡,导致误码产生;

(3)时钟同步错误,接收端解出的时钟与发送端嵌入的时钟不一致,导致数据接收错误。

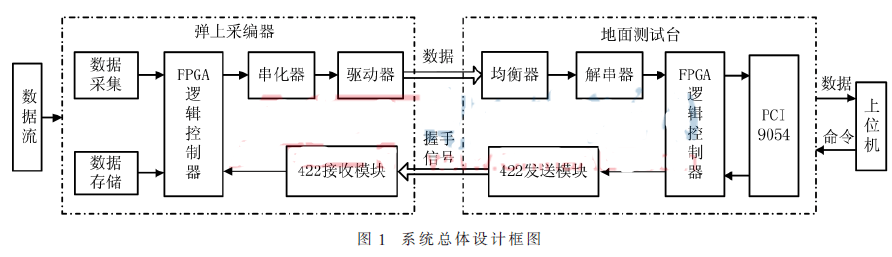

通过以上分析,首先在硬件设计方面对LVDS接口电路进行优化。在数据发送端,使用SN65LV1023A串化器将FPGA输出的并行数据转化为串行输出,其次在发送端增加LMH0001SQ高速驱动器,增强信号驱动能力;在接收端则采用LMH0073SQ自适应均衡器,补偿信号在远距离传输时出现的衰减,恢复其发生畸变的信号,最后通过SN65LV1224BDBR解串器,将串行数据转化为并行数据,经地面测试台PCI接口将数据送至上位机进行分析和处理。系统总体设计框图如图1所示。

1.1发送端电路的优化设计

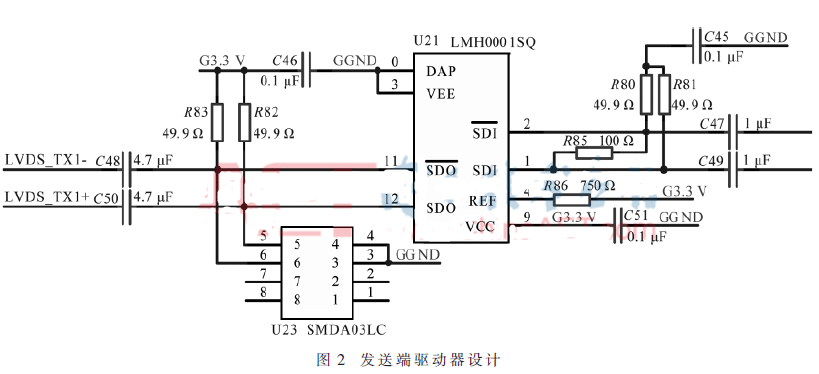

在LVDS发送端,由于串行器SN65LV1023A输出仅为100mV左右的低压差分信号,故需其在差分输出端增加LMH0001SQ驱动器来提高驱动能力。LMH0001SQ高速驱动器最高传输速率可达540Mb/s,差分输入门槛电压为100mV,功耗仅为125mW[3]。输出端电压可通过REF引脚外接电阻进行调节。本设计使用750Ω的外接电阻,得到约800mV的差分电压输出,加上直流偏置电压,使得输出电压在1.6V~2.4V之间,提高了数据远距离传输的驱动能力。发送端驱动器设计如图2所示。

由于LMH0001SQ差分线输入电阻需要与串行器SN65LV1023A进行阻抗匹配,因此PCB设计时100Ω电阻要紧贴引脚;同时输出端增加了SMDA03LC接口保护芯片,可防止输出端电路发生不可逆故障对后级电路造成影响,保证了LVDS接口的安全性以及可靠性。

1.2接收端电路的优化设计

LVDS信号在高速传输过程中由于导体的趋肤效应,信号会产生一定损耗,损耗程度与信号频率的平方根和电缆长度之积成正比。为保证信号传输可靠性,需要在接收端补偿信号。LMH0074SQ均衡器是针对78Mb/s~540Mb/s的传输速率,能够自适应补偿400mbelden1694A和第5类非屏蔽双绞线传输的损耗,该均衡器抖动性极低,功耗仅为208mW。

接收端均衡器设计如图3所示。使用时在LMH0074均衡器AEC+和AEC-引脚之间跨接一个1μF的电容,用来控制均衡环路的增益和带宽。由于输出端具有50Ω的差分输出,为防止信号发生振铃或反射,可在差分线间匹配精度为1%的100Ω电阻,布线时应尽量靠近解串器。均衡器最大程度地还原了衰减和畸变信号,提高了线缆传输质量,减少了误码和丢数现象。

210B6B编码逻辑设计

为进一步提高LVDS数据传输的可靠性,基于(7,4)线性分组码的编码思想,在传统的10B8B编码基础上改进并设计了一种10B6B编码方式,在允许降低传输有效带宽的情况下,设计4bit监督位来纠错4bit信息位,极大地降低了LVDS数据传输的误码率,很好地改善了直流平衡的状况。

2.110B6B编码原理

根据线性分组码的编码原理,(n,k)分组码要求2r-1≥n(r=n-k),才能用r个监督位构造r个监督关系式来指示一位误码的n种可能位置,进而实现差错控制。因为LVDS数据每次传输10bit数据,所以至少需要4bit监督位,因此该编码方式核心是用4bit监督位构造4个监督关系式用来指示误码的10种位置。这4bit监督位产生的4个监督关系式理论上可以产生16种校正子码组,根据实际需要选择合适的校正子码组来生成更适合传输的码型。

2.210B6B发送端逻辑设计

改进后的10B6B编码设定的校正子与误码位置关系如表1所示,其中S1、S2、S3、S4表示由监督关系方程式计算得到的校正子。由表1可知,当误码位置在a6、a8、a0、a2、a3时,校正子S1=1;否则S1=0。因此有:

编码时取a9、a8、a7、a6、a5、a4为信息码元,取a3、a2、a1、a0为监督码元,信息码元随机,而监督码元由以下监督方程唯一确定:

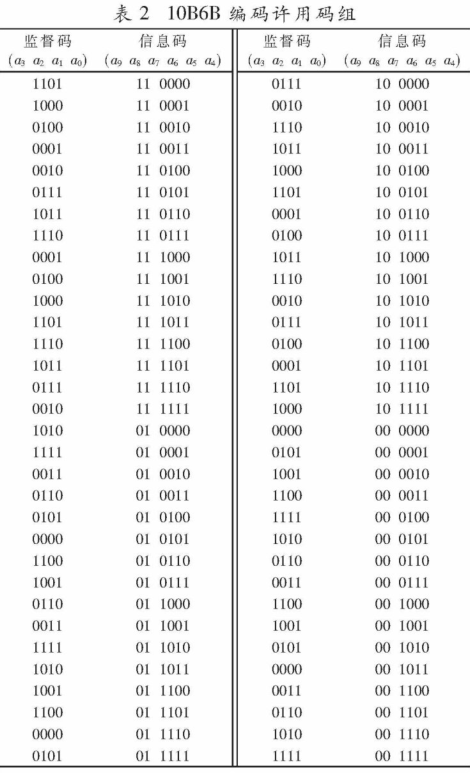

由上述方程式可得到表2所示的64个许用码组。

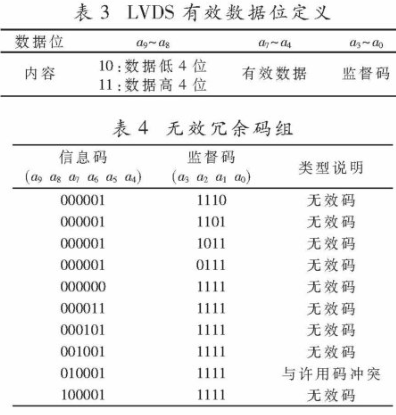

LVDS数据传输交替传输有效数据和无效数据。有效数据每个字节需传输两次,第一次传输低4bit,第二次传输高4bit,由LVDS最高两位a9、a8作为高低位标识。0000011111作为无效数据在数据线空闲时发送,用来锁定发送时钟。LVDS数据位具体定义如表3所示。

线上空闲时发送无效数据为0000011111,且编码时要考虑1bit误码的无效码冗余,即表4所示的无效冗余码接收时均当做无效码处理。由于0100011111与表2中许用码组冲突,因此在编码时不用01这个码组。

2.310B6B接收端解码设计

当接收端收到数据时,首先根据校正子方程式计算出校正子,根据表1即可对应出数据误码位置,对该位置进行编码生成纠错码,如表5所示。要注意的是当数据接收为表4中数据时,此时全部认为无效码,不予进行校正计算。生成纠错码后与接收的原始LVDS数据进行异或运算,即可纠正传输数据过程中的一位误码。

本系统还可对误码数据量进行统计,当纠错码为0000000011时,说明出现两位或以上的错位,此时字节错误统计自增1;当纠错码为不为0000000000时,说明数据出现一位错误,此时数据位错误统计自增1,方便对误码量进行数据统计。

3时钟同步逻辑设计

数据发送前,收发两端都需要对时钟进行同步锁定。初始化时串化器SN65LV1023A和解串器SN65LV1224B均为三态输出,当芯片供电电压稳定到2.45V时,解串器启动锁相环跟踪并锁定本地时钟,完成数据串行器和数据解串器的同步[7]。

本设计同步模式式采用随机同步和快速同步相结合的方式,设备上电后,串化器SN65LV1023A锁定发送时钟TCLK,FPGA将其SYNC1和SYNC2引脚电平拉低,此时串化器向接收端发送同步码,当解串器检测到LVDS输入端的边沿转换时,它就会根据FPGA提供的REFCLK参考时钟尝试锁定到嵌入在数据流中的时钟信息。由于串化器SYNC引脚与解串器的LOCK为开环状态,因此不能准确判断同步时间,所以设置在25μs的等待时间后,解串器与串行器完成同步,将解出的RCLK时钟送给FPGA后,LOCK引脚自动拉低,即可开始数据传输。

在进行数据发送时,当某个字节数据重复发送时,则解串器可能进入误锁定状态,错误地将数据上升沿识别为开始/停止位,这种现象称为重复多重转换(RMT)[9]。解串器中的电路检测到这种假锁状态时,电路就会阻止LOCK引脚输出有效,直到这种假锁状态发生改变。当解串器检测到4个连续周期的上升沿(停止/启动位)在同一位置时,解串器将重新锁定时钟,否则仍为失锁状态。

本设计数据传输采用有效数和无效数混合发送的方式,既可以保证LVDS线路时刻都有数据持续传送,不会因为由于有效数据发送不连续而造成失锁,也可减少由于内嵌时钟位锁定错误所造成的丢数的情况。同时设置最高两位为标识位,当最高位为“10”和“11”时为有效数据的低4位和高4位,否则为无效数。这种高位固定值的传输方式由于每次在12bit后有固定周期的跳变,极大程度地降低了嵌入时钟位误锁定的可能。

4数据可靠性验证

对硬件优化效果进行测试,在没有增加驱动器和均衡器双绞线长度为3.5m时,数据接收正常;当线缆长度增加时,误码率也随之上升,当测试传输电缆网长度增加为48m时,误码率已高达64.830245%,已完全不能保证数据的可靠传输。

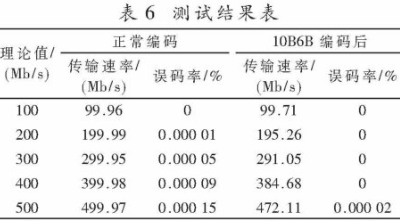

在增加驱动器和均衡器硬件优化后,采用6段8m的屏蔽双绞线组成48m的电缆网进行测试,修改采编器程序中LVDS数据发送时钟,使实际传输速率为100Mb/s、200Mb/s、300Mb/s、400Mb/s时,分别对采用10B6B编码方式前后进行误码测试,结果如表6所示。

分析测试结果可知:当传输速率低于100Mb/s时,硬件电路能保证传输的可靠性;当传输速率大于100Mb/s时,误码率随着速率的增大而增加。在逻辑设计上加入10B6B编码后,在允许降低传输有效带宽的情况下,传输速率为400Mb/s时可保证远程LVDS数据传输的可靠性。

5结束语

针对LVDS传输过程中的可靠性问题,从硬件和逻辑编码方式两方面进行了优化,设计的10B6B编码可对数据中存在1bit误码数据进行检测纠错,保障了数据的可靠性。在测试“递增数”、“递增数”、“全0数”、“全1数”4种码型数据时,可实现400Mb/s速率下48m的零误码远距离可靠传输,此设计系统已成功应用于航天飞行器中。

我要赚赏金

我要赚赏金