写这篇文章的初衷是缘于和做一位多年做SSD产品的人技术交流,对SSD产品PCIe信号走表层这一情况,很是疑惑。

这种疑惑是缘于我之前产品经验,不管是消费类产品,还是高速产品,在这些产品领域,走线初期规划,都是默认选择:高速信号走内层。

这里面有损耗问题,还有表层阻抗问题,还有绿油的问题,这些不稳定因素,是选择高速信号走内层的原因。

这个多年做存储产品的人,给的回答竟然是:三星很多大厂都是这样做的,我们照着做的。一时间无言以对。

那就自己想办法找找原因。

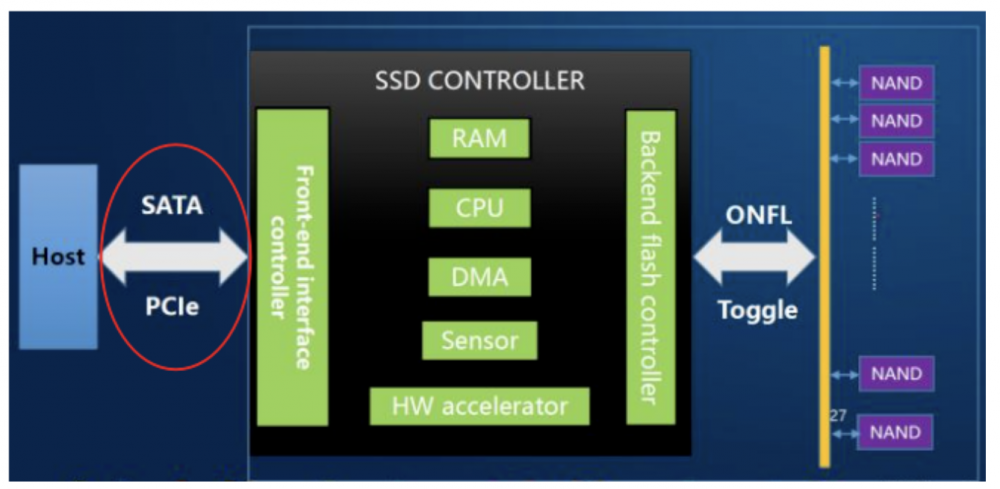

下图为SSD内部的一个组成框架,三个组件:NAND闪存,控制器及固件。本文不过多地讲解这类产品的工作原理,关注的是主控和接口的连接及版图走线问题。

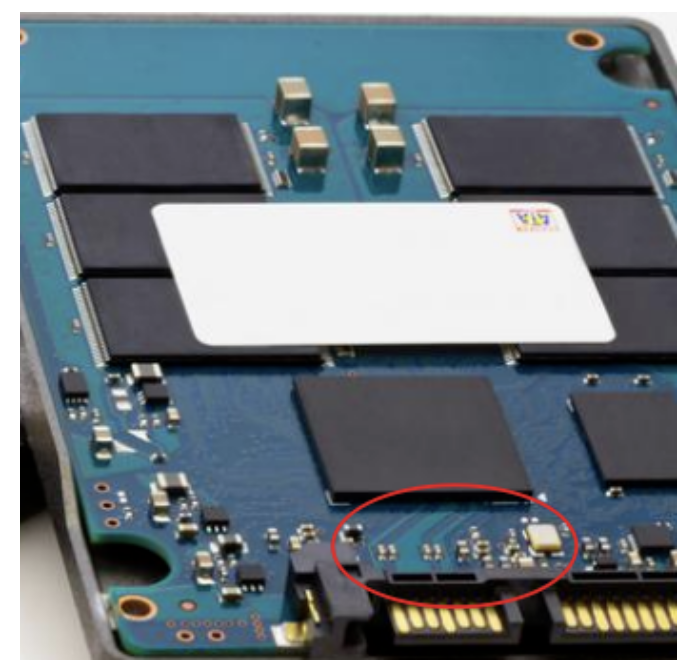

下图为常见存储产品表贴情况,也会发现主控和接口的走线连接在表层,这里面看到不仅仅是TX部分因为耦合电容问题,走线走表层,其实接收端RX也在表层。

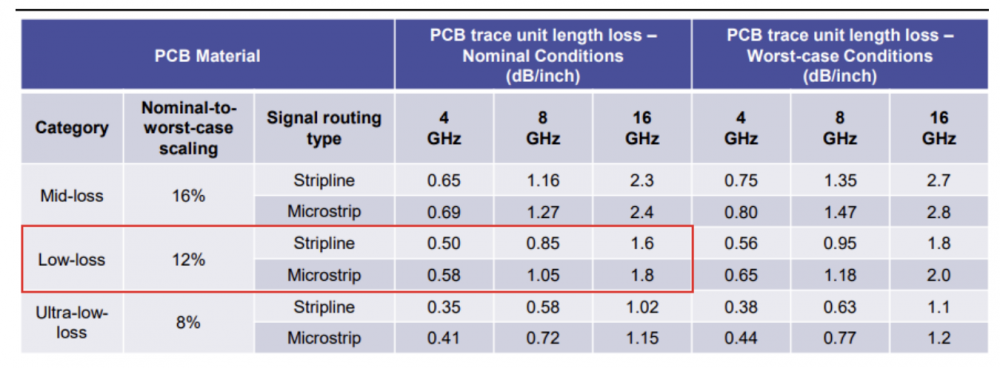

在正常的情况下,Low-loss级别的板材,PCIe Gen4 走线,在表层走线的损耗大于内层的,量化指标值为0.2dB/in,这个值只是用于探讨本文的问题,具体的差值需要PCB实测数值来比较,而且每家板厂的工艺和能力是不同的。

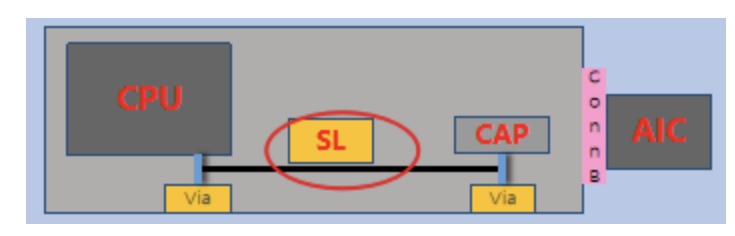

现在的问题就是,走表层和内层的差别是什么?见下图链路结构情况,最直接的差别就是多了两个过孔:

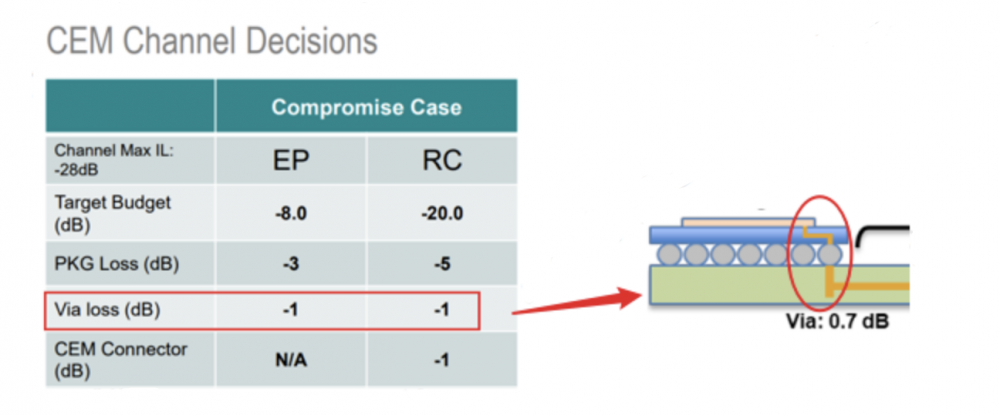

根据相关过孔指标,过孔0.7dB的标准,如果通过残桩、反焊盘等优化处理,这个数值还可以更小一点,两个过孔取值为1 dB。

量化为过孔指标,那么两种走线模式的差别就变成了走线长度的问题,即表层走线(MicroStrip)和内层走线(StripLine)长度差问题。

考虑到表层走线和内层走线的损耗插值是0.2dB/in,两个过孔的损耗是1dB。这里面可以简单认为5 inches 是一个标准值。

考虑到存储产品布线空间,以及相关产品尺寸的限制,一般主控离接口的距离控制在1inch 左右。

未来不排除存储产品的更新换代,性能和尺寸的变更,这个5 inches是一个基准值,这里面还没有考虑表层走线反射的问题,还有绿油带来的损耗问题,这些不可量化的因素才是信号完整性解决的关键。

两害取其轻,就目前的情况,选择走表层也是一个折中优化的选择。

未来随着未来存储产品速率的提升以及产品尺寸的变化,这个值可能是4 inches,也可能是3 inches ,当然不管怎么变,基本的原理不会变,知其然,知其所以然,这才是追求技术的本质。

我要赚赏金

我要赚赏金