这本书要完全搞懂难度有点大,如果尝试着从高速串行链路时钟架构开始,不妨可以讲一讲这本书理解的四点。

01

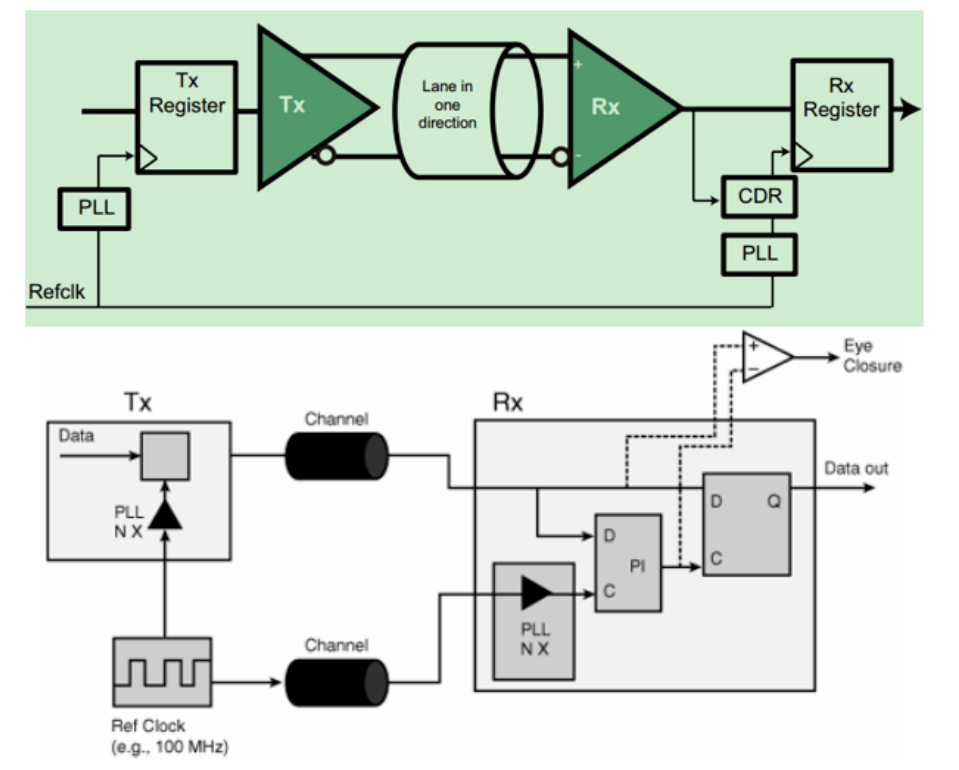

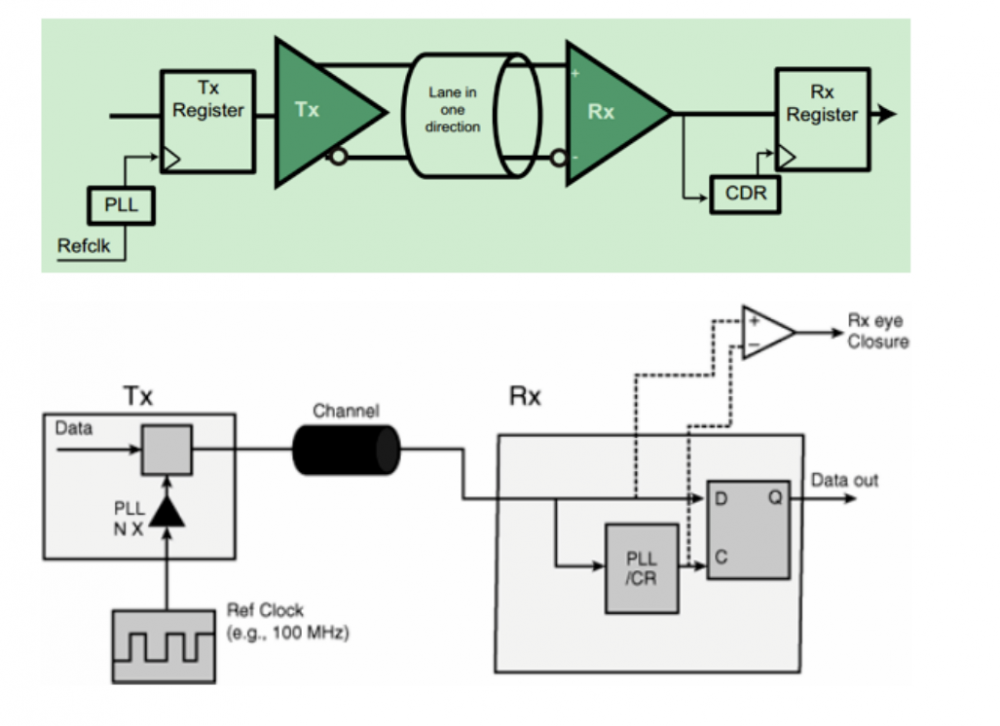

任何通信链路系统一般由三个部分组成:发送器(Tx),信号或媒介,接收器(Rx)。高速串行链路,特别是Gb/s级数据数率下,时钟恢复体系结构已成为重点关注点。

讲时钟,书中提了常见的两种时钟架构:

公共时钟架构

【Common Refclk (Shared Refclk) Architecture】

数据时钟架构

【Data Clocked Rx Architecture】

实际上,还有一种分立时钟架构(Separate Refclk Architecture),设计复杂,不常用。

高速链路系统参考时钟通常由晶振和锁相环生成。晶振会产生大约10MHz左右的低频时钟,而锁相环(PLL)会对低频时钟进行倍频,经过一个或多个锁相环(PLL)得到100MHz的时钟输出。

为了减小时钟引起的电磁干扰(EMI),大多数应用都采用扩频时钟的办法。关于扩频:调制波形是三角波,不是正弦波或方波;调制范围是向下扩频,而不是向上扩频或中心扩频。这样做的原理不多讲,目的很简单:为了得到更可靠的基准频率。

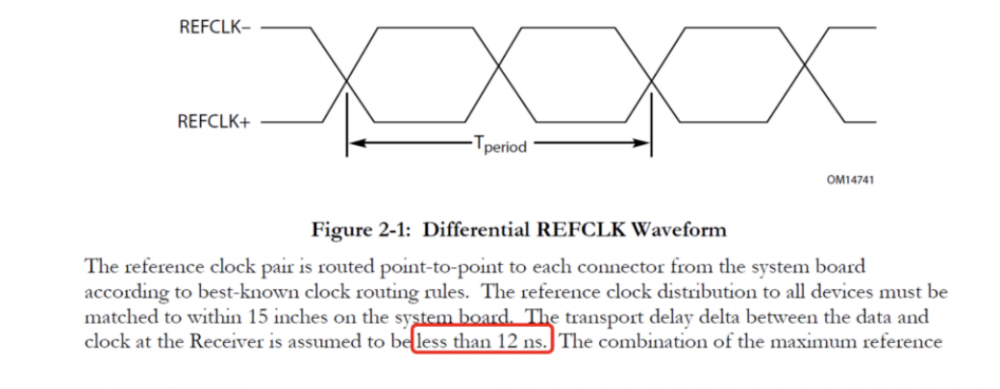

实际工作中,针对PCIe链路,在PCIe3.0规范文档物理层电气层章节,针对公共时钟架构,有时延的相关规定:

02

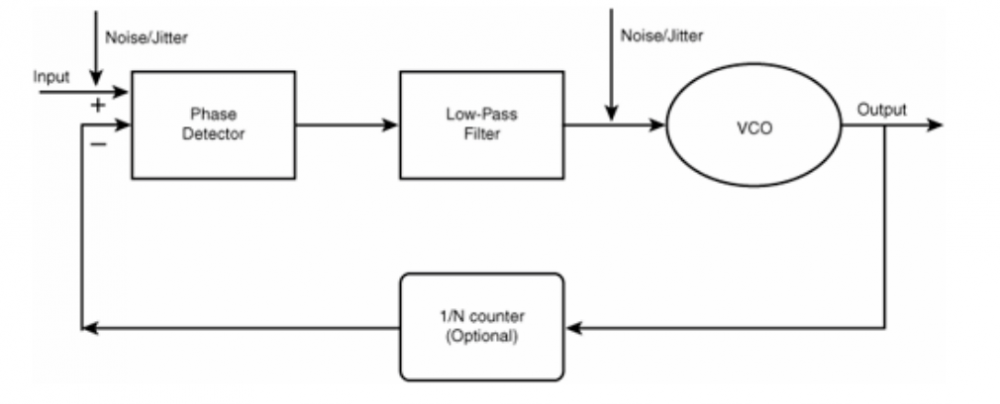

不仅是晶振会产生低频相位噪声或抖动,锁相环内部压控振荡器也会产生,这些都是需要关注的。讲讲锁相环(PLL)吧。

锁相环(PLL)由鉴相器(PD)、低通滤波器(LPF)、压控振荡器(VCO)和分频/倍频器组成。

外部的抖动或噪声源是输入的参考时钟,内部的噪声源是压控振荡器(VCO)。

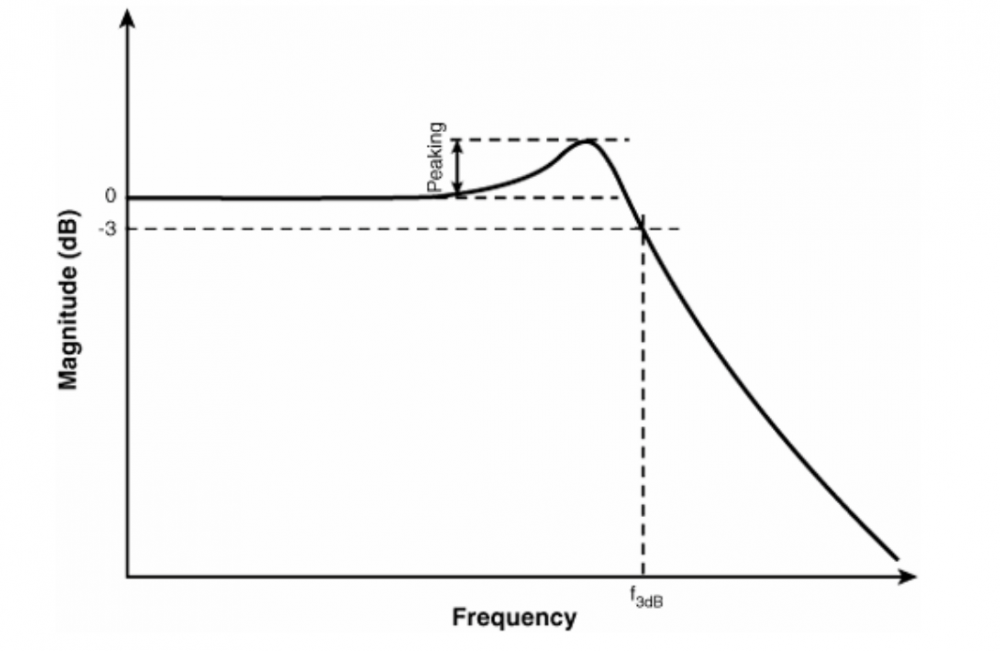

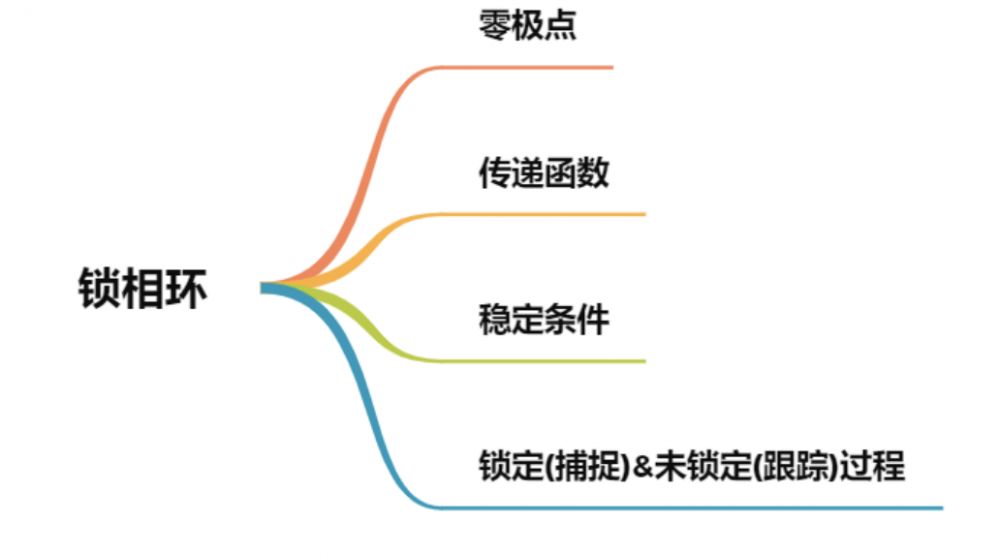

锁相环(PLL)是一个复杂的反馈系统,无意在这里做时域和频域转换的建模与分析。但一些功能与参数还是得讲一下。既然是反馈,那就有传递函数,下图即为传递函数幅度响应及尖峰和3 dB带宽:

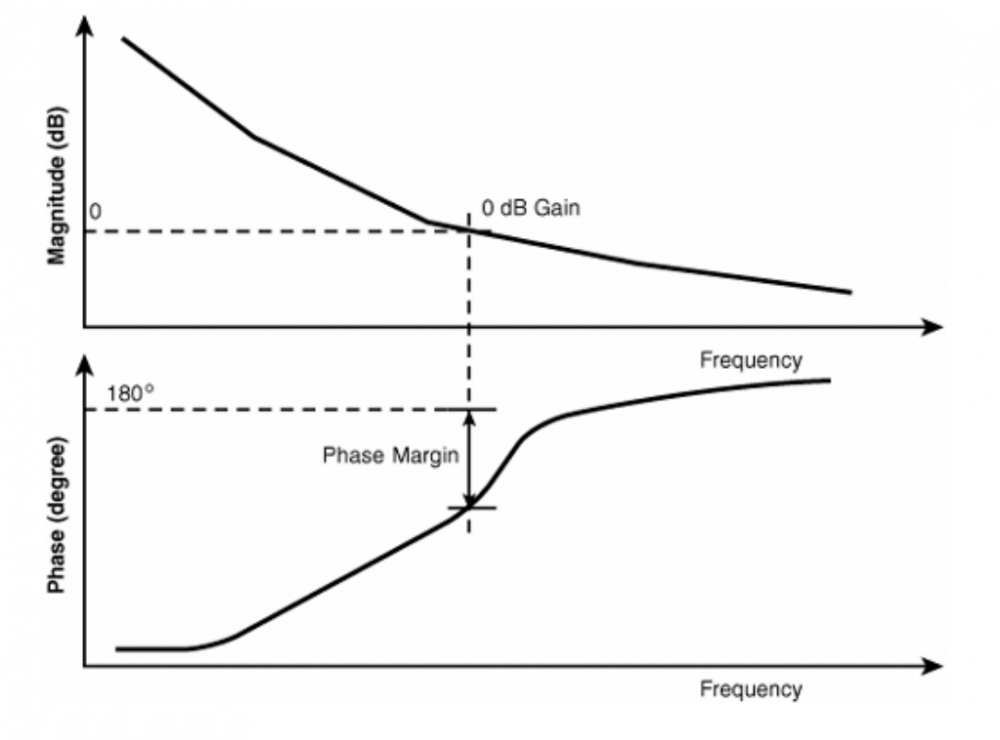

一个稳定的锁相环(PLL)应当满足:相位为180°时,开环增益小于1。开环增益为1时,相位小于180°。幅度和相位的频率函数称为伯德图,如下图:

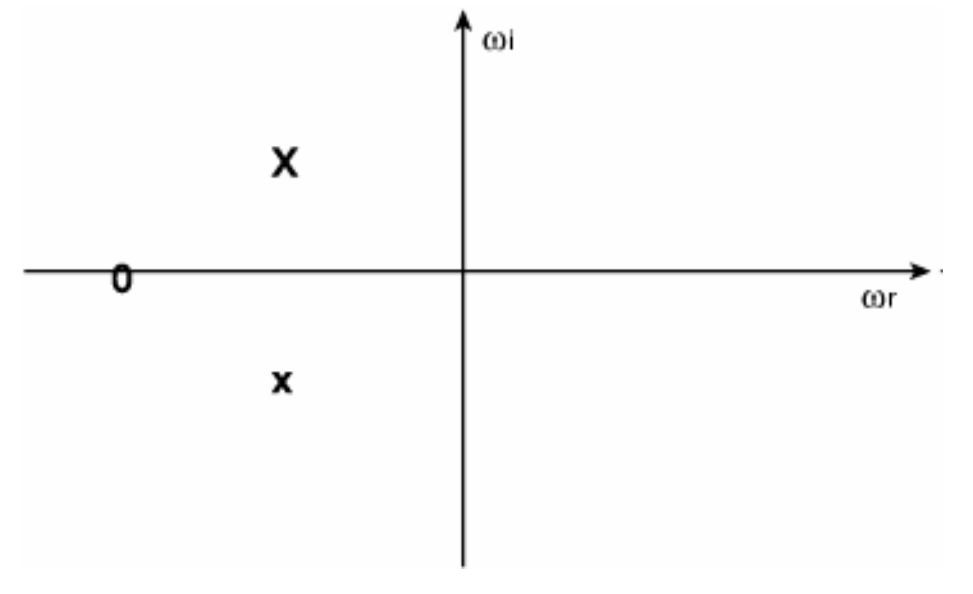

极点和零点

零极点数量和复频域的分布,可以快速确定系统的不稳定性、振铃和衰减的特性。

极点是使系统函数趋于无穷大的一组复频率。零点位置是系统出现在零传输的位置。

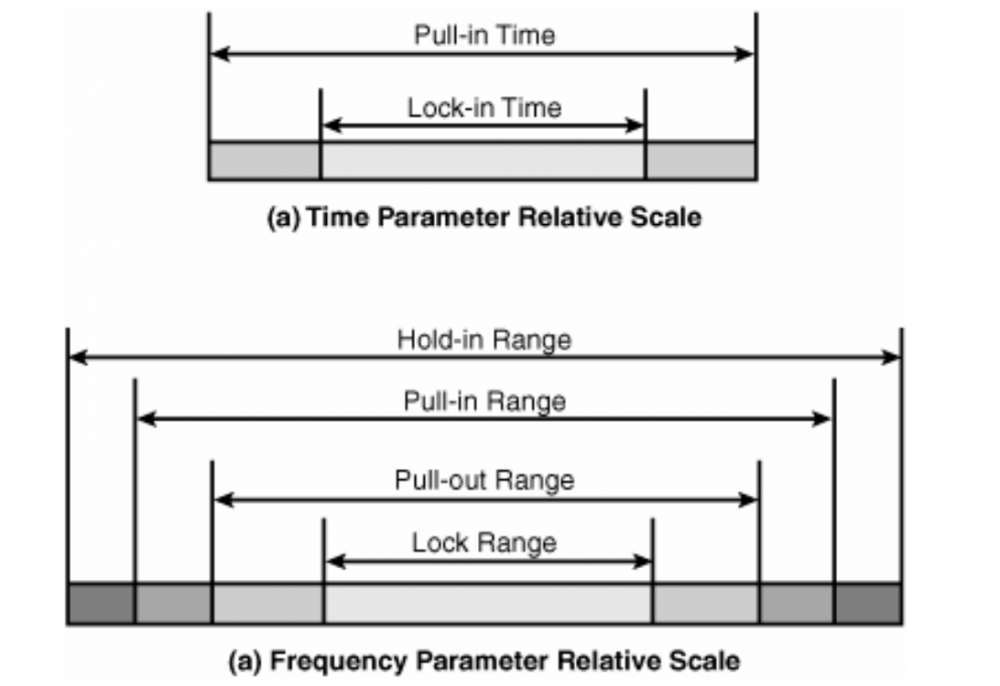

锁相环(PLL)有锁定(捕捉)和未锁定(跟踪)过程,这里面有锁定时间,捕捉范围,跟踪失步范围等。

锁定范围是指锁相环(PLL)在一个频率差拍周期(从输入参考到PLL输出之间)锁定参考频率的范围。

失步范围是指维持PLL锁定状态条件时,输入参考信号所允许的最大频率突变。

回到最初的时钟架构,公共时钟架构时钟抖动控制在300~+2800ppm范围,才能保证不失锁。

数据时钟架构保证在5600ppm的抖动范围内,CDR才会不失锁。印象中,时钟芯片范围20ppm或50ppm。

以上便是锁相环(PLL)基础知识。

03

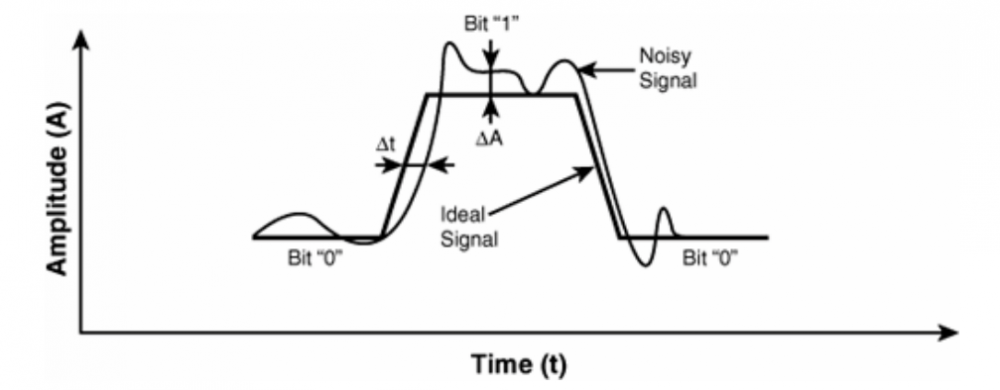

信号和理想值的偏离,分两个方面:

信号幅度的偏离,称之为幅度噪声;

时间的偏离,称之为时序抖动。

幅度噪声是一个持续的过程,时刻影响整个系统,时序抖动只是在边沿跳变时影响系统。

抖动是指信号边沿跳变时序相对于理想时序的任意偏离。

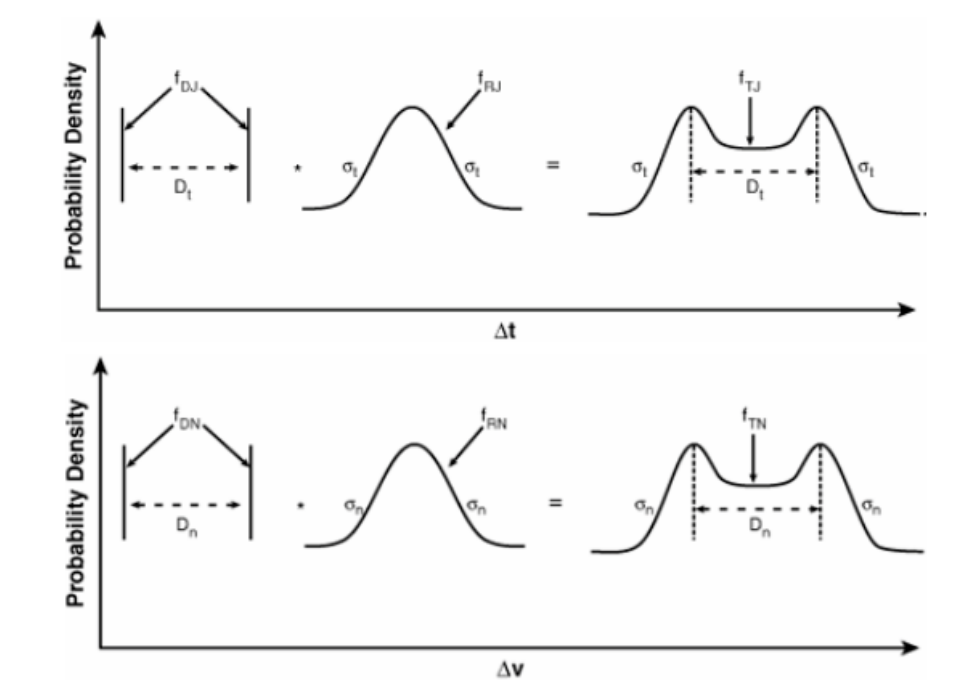

关于抖动,分两个部分确定性抖动&随机抖动来展开。

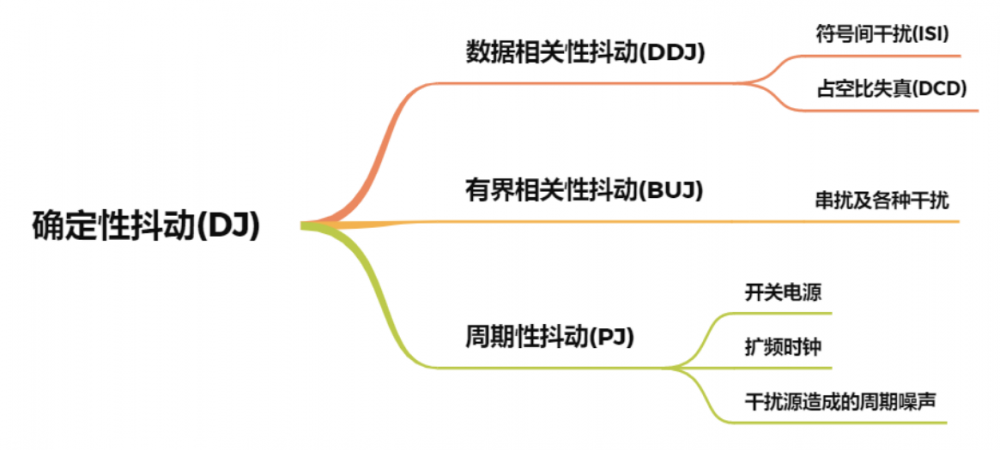

确定性抖动(DJ)根源可能是媒质的有限带宽、反射、串扰、EMI、地弹、周期性调整或模式。

①周期性调制(相位、幅度和频率)

典型的调制形式:正弦曲线,三角波,锯齿波。开关电源,扩频时钟和周期性电磁干扰源都会造成周期性的噪声。

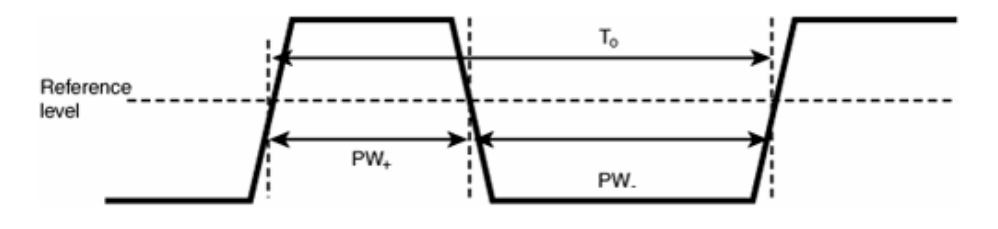

②占空比失真(DCD)

信号脉冲宽度与信号周期的比值。

脉冲的占空比相对于正常值发生的偏离,或变长或变短都会造成DCD。

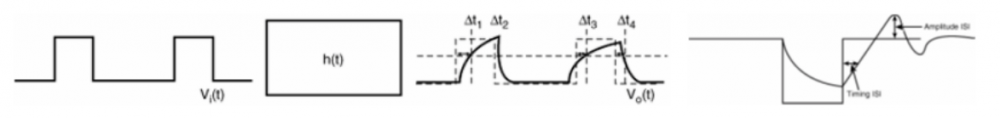

③符号间干扰(ISI)

关于符号间干扰(ISI),有两种说法:

1.当信号沿传输线传播时,总存在反射、串扰或其他噪声源引起的噪声。这些噪声会影响发送到传输线上的信号,降低时序容限和信号完整性容限。这种现象称为ISI。

2.在有损媒质中,(较高频率的)比特流可能会造成跳变时序和信号幅度偏离理想值。……由于容性效应,每次电平跳变都要有一定的电荷充放电时间。如果前次跳变的电平在达到预定电平之前,紧接着发生又一次跳变,那么当前比特就可能产生时间和电平量级的偏差,这种效应会级联累积”。

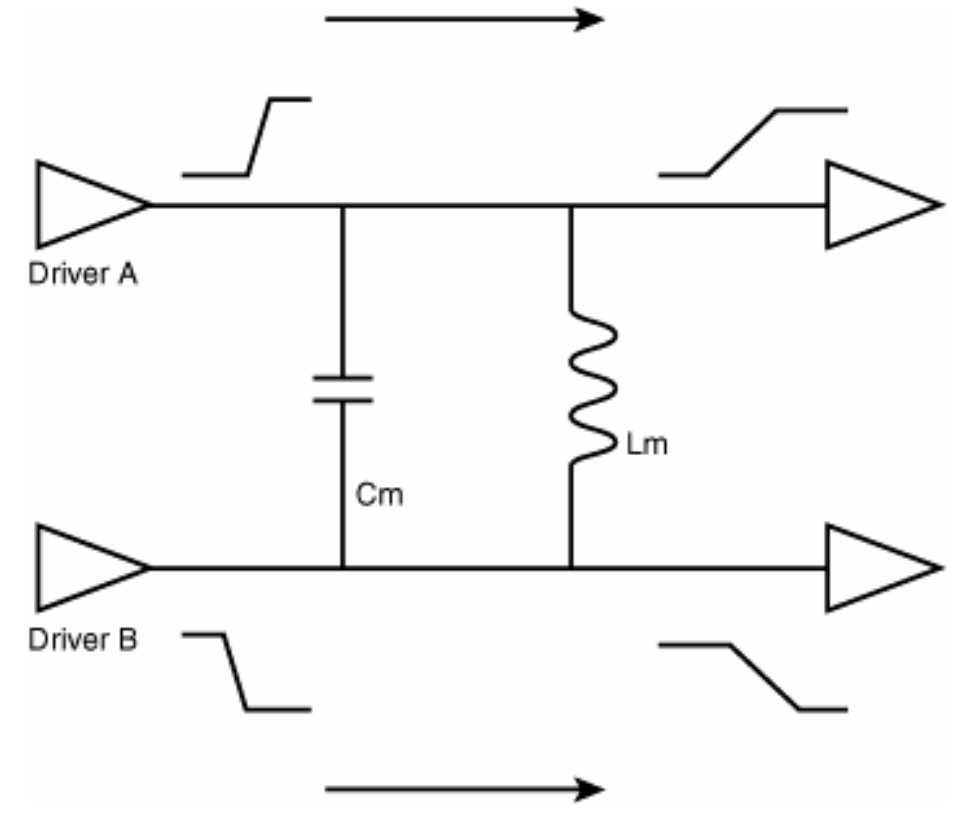

④串扰以及各种干扰(反射&EMI等)

串扰是一种干扰,表现为电压波动或噪声,表现形式:容性耦合(相位相同)&感性耦合(相位相反)。

随机抖动(RJ)根源可能是固有噪声(热噪声、散弹噪声、闪烁噪声)、随机调制或非平衡干扰。

随机抖动的成因于固有噪声和抖动。

固有噪声是电路、光学设备或半导体材料中电子和空穴的随机性和波动性导致的噪声。

①热噪声(Thermal Noise):在温度平衡条件下由于电荷载流子的随机运动所产生的噪声。

②散弹噪声:由于随机的电流波动导致的,源于电荷中单个量子化电荷流。

半导体器件中,散弹噪声大于热噪声。

③闪烁噪声:元件杂质污染和工艺缺陷使得直流电流中载流子可能被束缚,然后释放的过程,这个过程是随机的,主要集中在低频段。

04

除了和噪声无关的DCD,大多数关于抖动和噪声分量的概念对两者是适用的,同类型分量的抖动和噪声可能有一定的相关性。

至于抖动和噪声相关转换及分离的关系,用到了很多函数及公式工具。

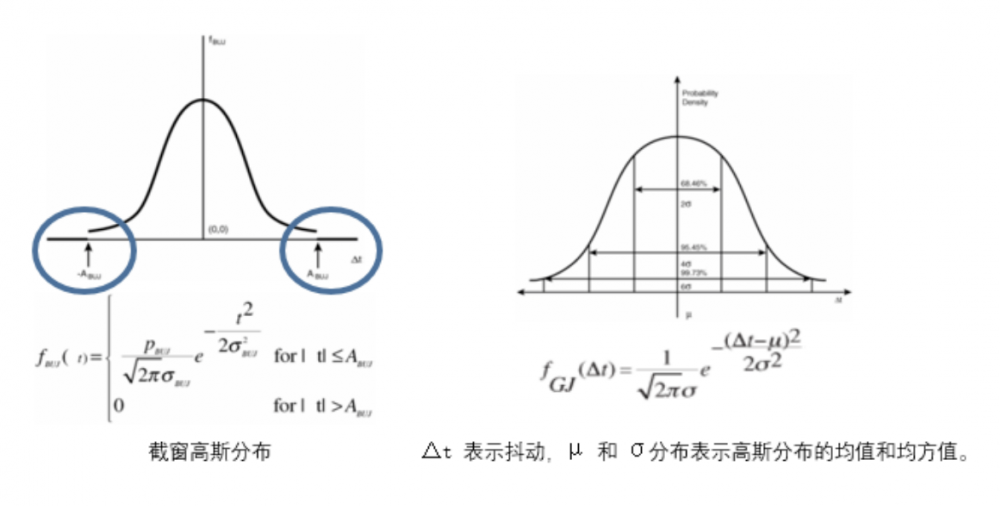

随机抖动(RJ)引入的数学模型是高斯分布,高斯抖动和随机抖动却有所不同,这两者的区别是白噪声。

还有个截窗高斯分布,这个和高斯分布又有不同,区别于PDF的拖尾部分。如下图蓝色标记。

看到截窗高斯函数,想起的是时域与频域中,离散傅里叶变换,周期性信号产生拼接不连续现象。为了避免这个问题,通常采用加窗滤波器,以保证两头的电压在同一个值处连续。汉宁(Hanning)窗就是实现这一功能的滤波器。

眼图睁开程度:

UI 取决于抖动&内眼是否闭合及其外眼过大取决于噪声。当然也和各自形状和特性相关。

备注一下术语:

probability density function PDF 概率密度函数

cumulative distribution function CDF 积累分配函数

Power Spectrum Density PSD 输出功率谱密度

Dual-Dirac 双狄拉克

data-dependent jitter DDJ 数据相关性抖动

bounded uncorrelated jitter BUJ 有界非相关性抖动

除了简单的时域频域的傅里叶变换(Fourier transform)及微积分方程的拉普拉斯(Laplace transformation),还有蒙特卡罗(Monte Carlo method),切比雪夫不等式(Chebyshev Inequality),巴特沃斯滤波器(Butterworth filter),伯德图(Bode Plots),巴克豪森(Barkhausen condition),平方和根(Root-Sum-Square),泊松分布(Poisson distribution)等。

看到上面这些,头大得很。这本书只是半知半解,还得二刷或三刷。

我要赚赏金

我要赚赏金