共7条

1/1 1 跳转至页

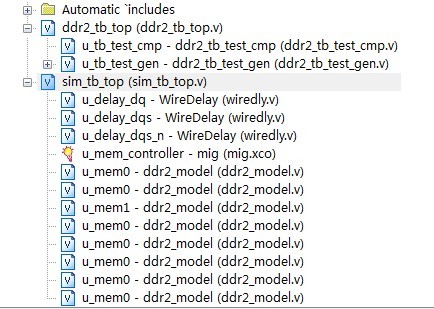

如何使用MIG3.6生成的example design

2楼

MIG3.6,这么高的版本啊,你用的ISE13.1吗?

我之前只用过MIG2.1的,我记得example design应该是可以直接仿真的。可以做一个状态机与DDR2 IP进行接口。

这个接口还是比较复杂的,建议你还是多花些时间看看DDR2 IP手册吧

我之前只用过MIG2.1的,我记得example design应该是可以直接仿真的。可以做一个状态机与DDR2 IP进行接口。

这个接口还是比较复杂的,建议你还是多花些时间看看DDR2 IP手册吧

用的是ISE12.3的,里面自带的MIG。我用的是ISE自带的仿真器,把user design里面的仿真文件导入就能进行行为仿真,但导入example design里的仿真文件运行就会出这样的错:

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

user guide也看过了,里面就说把文件添加进去就行。。

你之前用的MIG2.1里面,example design和user design里面的东西有什么不同吗?

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

user guide也看过了,里面就说把文件添加进去就行。。

你之前用的MIG2.1里面,example design和user design里面的东西有什么不同吗?

7楼

哦。我用MIG3.4生成的,example design导入后顶层文件和testbench的端口不匹配。而用user design的就可以。

那你就在user design的基础上改吧

你的这个错误应该就是顶层文件找不到或接口不匹配的原因

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

那你就在user design的基础上改吧

你的这个错误应该就是顶层文件找不到或接口不匹配的原因

ERROR:Simulator:778 - Static elaboration of top level Verilog design unit(s) in library work failed

共7条

1/1 1 跳转至页

我要赚赏金

我要赚赏金