13、PLL简单的配置实验

PLL(锁相环),给PLL一个时钟输入,经过PLL内部处理后,在输出端口就可以得到一定范围的时钟频率。

下面用图文对PLL的配置简单的说明下。

步骤:

1、先建一个PLL的工程,这个大家都会,不用做介绍;

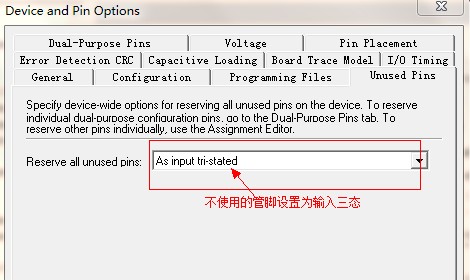

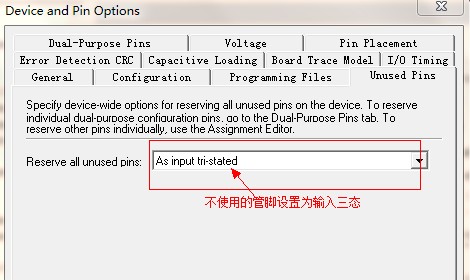

2、建完工程后,将不用的管脚设置为输入三态;

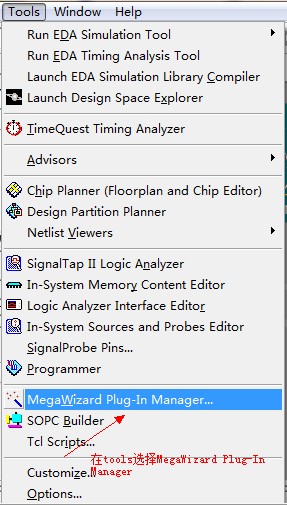

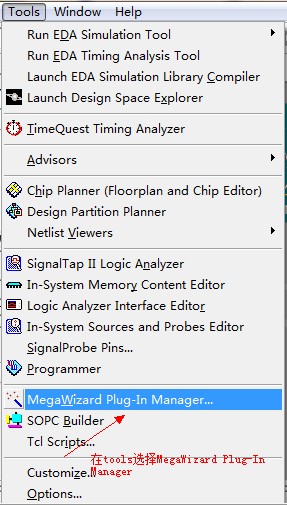

3、在Quartus的菜单栏选择tools--->MegaWizard Wizard Plug - In Manager

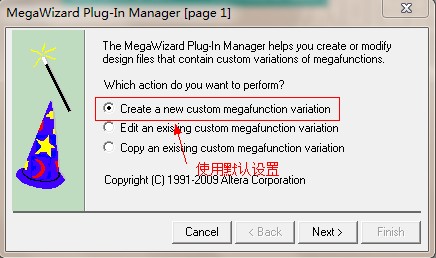

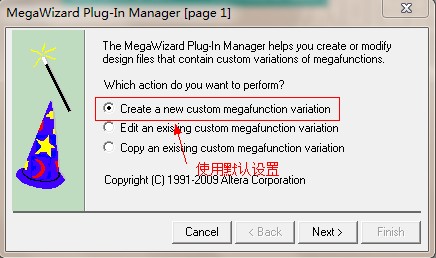

4、选择默认选项,如下图

5、如下图进行操作

(1)在I/O下,选择ALTPLL;

(2)选择Verilog HDL为配置PLL内核的使用语言;

(3)输入例化PLL的文件名;

6、选择器件的速度等级及外接晶振的大小

7、配置时钟c0的相关参数

8、配置时钟c1的参数

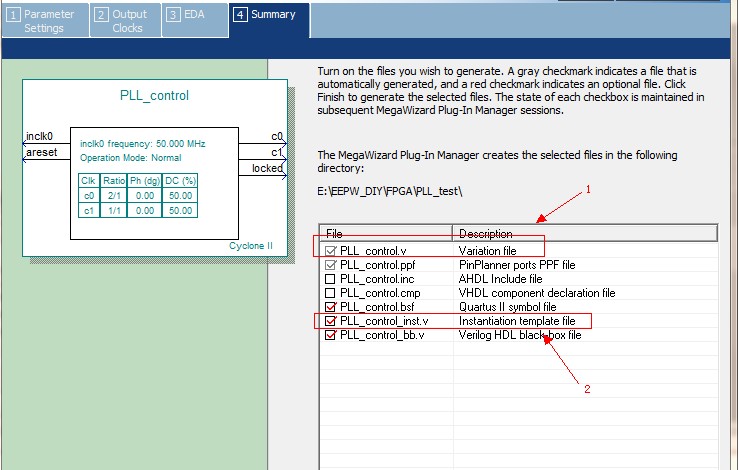

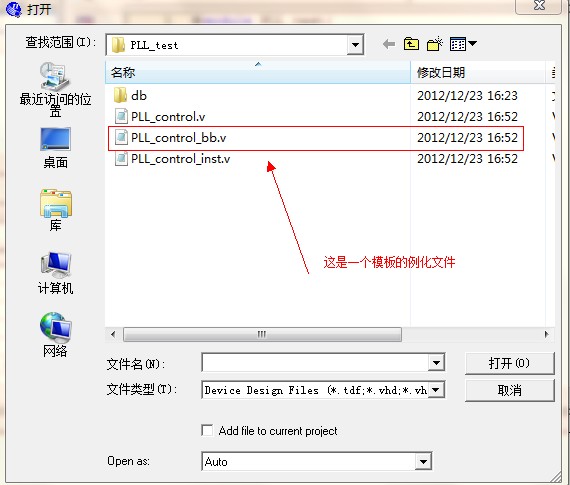

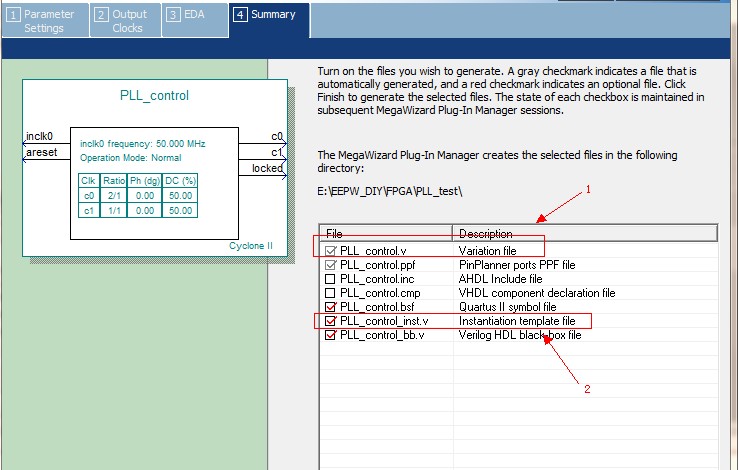

9、PLL核最终输出文件

(1)PLL_control.v PLL内部的控制IP核

(2)PLL_control_inst.v 是PLL的例化文件,可以直接复制来使用。

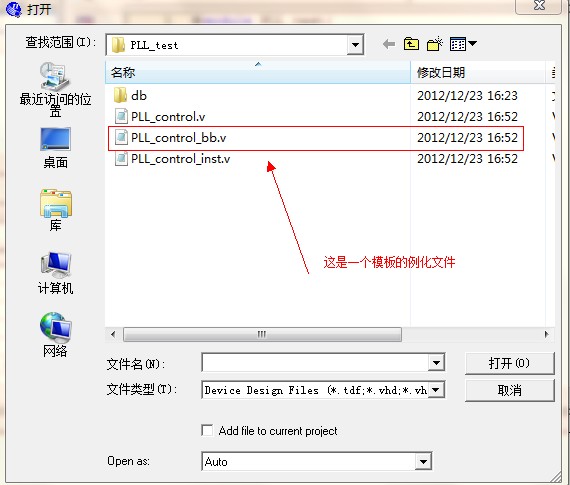

10、打开红框下面的 PLL_control_inst.v文件 复制里面PLL的例化模板

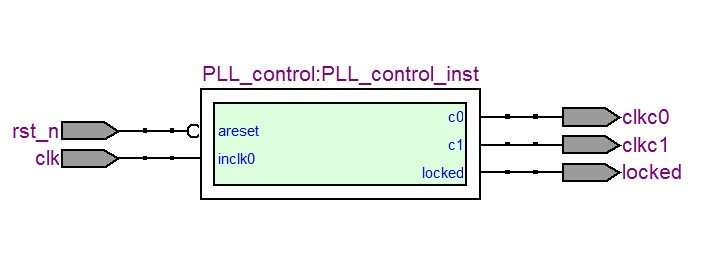

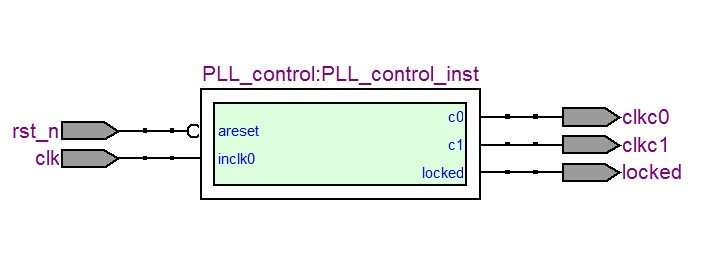

11、将PLL例化文件粘贴到PLL_test文件中,修改信号接口,与自己的定义的接口对应。

12、编译,打开RTL视图

PLL(锁相环),给PLL一个时钟输入,经过PLL内部处理后,在输出端口就可以得到一定范围的时钟频率。

下面用图文对PLL的配置简单的说明下。

步骤:

1、先建一个PLL的工程,这个大家都会,不用做介绍;

2、建完工程后,将不用的管脚设置为输入三态;

3、在Quartus的菜单栏选择tools--->MegaWizard Wizard Plug - In Manager

4、选择默认选项,如下图

5、如下图进行操作

(1)在I/O下,选择ALTPLL;

(2)选择Verilog HDL为配置PLL内核的使用语言;

(3)输入例化PLL的文件名;

6、选择器件的速度等级及外接晶振的大小

7、配置时钟c0的相关参数

8、配置时钟c1的参数

9、PLL核最终输出文件

(1)PLL_control.v PLL内部的控制IP核

(2)PLL_control_inst.v 是PLL的例化文件,可以直接复制来使用。

10、打开红框下面的 PLL_control_inst.v文件 复制里面PLL的例化模板

11、将PLL例化文件粘贴到PLL_test文件中,修改信号接口,与自己的定义的接口对应。

12、编译,打开RTL视图

回复

| 有奖活动 | |

|---|---|

| 2026年“我要开发板活动”第三季,开始了! | |

| 硬核工程师专属补给计划——填盲盒 | |

| “我踩过的那些坑”主题活动——第002期 | |

| 【EEPW电子工程师创研计划】技术变现通道已开启~ | |

| 发原创文章 【每月瓜分千元赏金 凭实力攒钱买好礼~】 | |

| 【EEPW在线】E起听工程师的声音! | |

| 高校联络员开始招募啦!有惊喜!! | |

| 【工程师专属福利】每天30秒,积分轻松拿!EEPW宠粉打卡计划启动! | |

我要赚赏金打赏帖 我要赚赏金打赏帖 |

|

|---|---|

| RTOS怎么选?让我来给你答案!被打赏¥15元 | |

| 【S32K3XX】Flash驱动使用被打赏¥26元 | |

| 【FreeRtos】第一个任务的启动过程被打赏¥21元 | |

| 【分享开发笔记,赚取电动螺丝刀】FPB-RA6E2开发板的WDT功能测试被打赏¥22元 | |

| 关于cmakelist特性presets的使用被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】M5STACK系列屏幕质量测试程序,竟然有块亮斑?被打赏¥20元 | |

| 【分享开发笔记,赚取电动螺丝刀】快速搭建瑞萨FPB-RA6E2开发板开发环境被打赏¥14元 | |

| 【分享开发笔记,赚取电动螺丝刀】在音频测试中顺序的调整可改变功效被打赏¥18元 | |

| 【分享开发笔记,赚取电动螺丝刀】点阵显示模块及其应用-----献给新年的小礼物被打赏¥22元 | |

| 基于地奇星开发板的数码管模块显示技术被打赏¥23元 | |